# Signetics

# FAST Data Manual Manual

## WWW

#### ARROW ELECTRONICS, INC.

521 WEDDELL DRIVE SUNNYVALE, CALIFORNIA 94086 SALES (408) 745-6010 CUST. SERV. (408) 745-6630 ADMIN. (408) 745-6600 TWX 910-339-9371

# FAST Data Manual 1984

Signetics reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and Signetics makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

© Copyright 1984 Signetics Corporation

#### **PREFACE**

Signetics would like to thank you for your interest in our FAST<sup>TM</sup> product line. Because of its wide customer acceptance, FAST has become the preferred high-performance Logic family of the 80's. We are proud to participate in and contribute to the dynamic growth of this market.

Each data sheet contained in this manual is designed to stand alone and reflect the latest DC and AC specifications for a particular product. Features of this first Signetics FAST Data Manual include:

- · Availability and Functional Cross-Reference Guides

- A Circuit Characteristics Section

- · A User's Guide

- · Selected Application Notes

- · A Chapter on Surface-Mounted Devices (SMD)

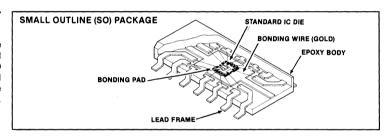

- Introduction of the SO surface-mounted package as a commercial option

New FAST part types are being released monthly. As you see new product announcements, you should contact your local Signetics sales office, representative or authorized distributor, or write Signetics, c/o Information Services at 811 East Arques Avenue, P.O. Box 3409, Sunnyvale, California 94088-3409, for the latest technical information.

In addition to FAST, Signetics Logic Division offers a line of commercial Logic products which spans a wide speed/power spectrum from 10K/100K ECL to HC/HCT High-Speed CMOS, and includes industry-standard families such as 4000 Series CMOS, 74, 74LS, and 74S Logic. Information on these product lines is also available from your nearest Signetics sales office, sales representative or authorized distributor.

Signetics Logic Division

$<sup>^{\</sup>mathsf{TM}}\mathsf{FAST}$  is a trademark of Fairchild Camera and Instruments Corporation

#### **CONTENTS**

| Introductionv                                                       |

|---------------------------------------------------------------------|

| Ordering Information                                                |

| Product Status and Definitions                                      |

| Section 1 — Indices                                                 |

| Numerical Index                                                     |

| Section 2 — Quality and Reliability                                 |

| Section 3 — Circuit Characteristics                                 |

| Section 4 — FAST User's Guide                                       |

| Data Sheet Specification Guide    4      Design Considerations    4 |

| Section 5 — 54/74F Series                                           |

| Data Sheets                                                         |

| Section 6 — FAST Application Notes                                  |

| Using FAST Logic Functions in Microprocessor Systems — App Note 201 |

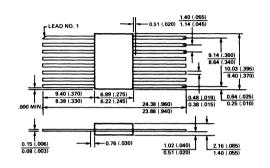

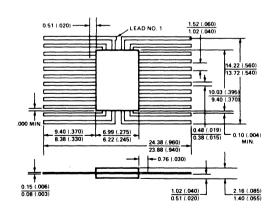

| Section 7 — Surface Mounted Devices (SMD)                           |

| Section 8 — Military Products                                       |

| Product Information                                                 |

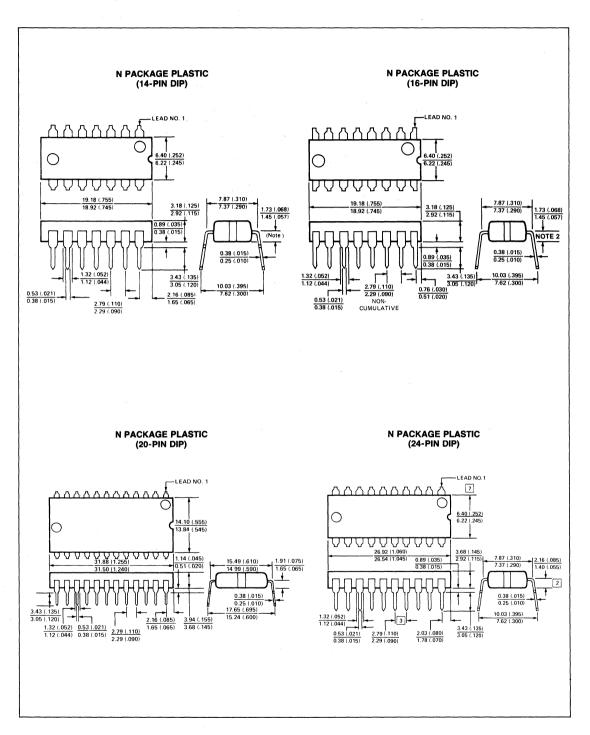

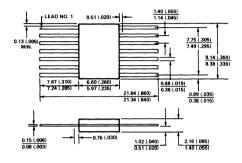

| Section 9 — Package Outlines                                        |

| Data Information                                                    |

| Section 10 — Sales Offices                                          |

#### INTRODUCTION

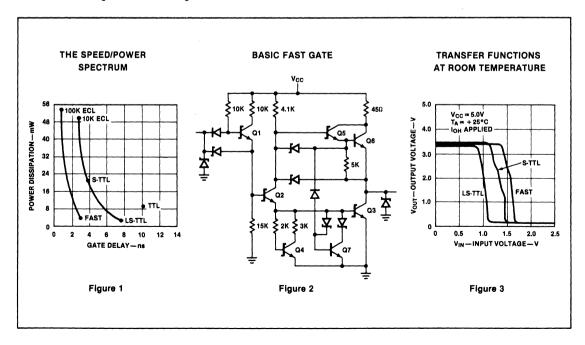

#### THE HIGH-SPEED LOGIC OF THE 80's

#### PRODUCT DESCRIPTION

Signetics has combined advanced oxide-isolated fabrication techniques with standard TTL functions to create a new family designed for the 80's. The high operating speeds of FAST can push system operating speeds into areas previously reserved for 10K ECL, but with simple TTL design rules and single 5V power supplies. Low input loading allows the user to mix LS, ALS, and HCMOS in the same system without the need for translators and restrictive fanout requirements.

FAST circuits are pin-for-pin replacements for 74S types, but offer power dissipation 3-4 times lower and higher operating speeds. Existing systems can achieve much lower power by replacing the 74S types with the corresponding FAST devices, with no changes other than reducing the size of the power supply.

The input structure provides better noise immunity because of higher thresholds, while the oxide-isolation and new circuit techniques create devices that have less variation with temperature or supply voltage than existing TTL logic families. Signetics guarantees all ac parameters under realistic system conditions—across the supply voltage spread and the temperature range, and with heavy 50pF output loads.

The use of high-capacitance PNP inputs has been avoided, and clamping diodes have been added to both the inputs and outputs to prevent negative overshoots. High input breakdown voltages allow unused inputs to be tied directly to  $V_{CC}$  without pullup resistors.

Multiple sources and a complete family of powerful circuits combine to make Signetics FAST the logic choice of the 80's!

#### **FEATURES**

- 3ns propagation delays

- 4mW/gate power dissipation

- Guaranteed AC performance over temperature and supply voltage spreads

- · Improved input and output structures

- Standard TTL functions and pinouts

- · Replacement for "S" types . . . 1/4 the power

- · Designer's choice for new system designs

#### INTRODUCTION

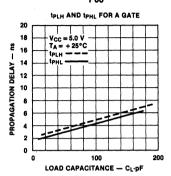

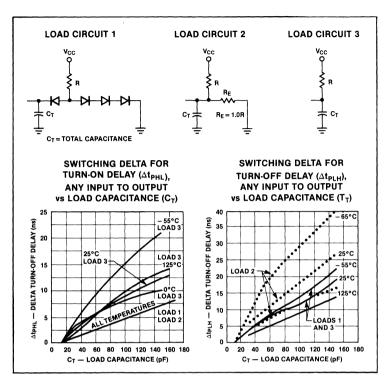

#### PROPAGATION DELAY VS LOAD CAPACITANCE 'F00

Figure 4

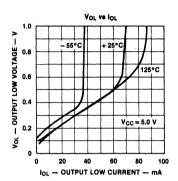

## OUTPUT LOW CHARACTERISTICS 'F00

Figure 5

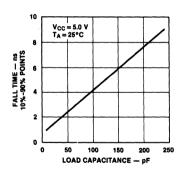

### FALL TIME VS LOAD CAPACITANCE 'F00

Figure 6

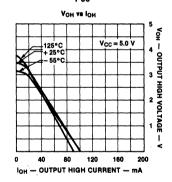

## OUTPUT HIGH CHARACTERISTICS 'F00

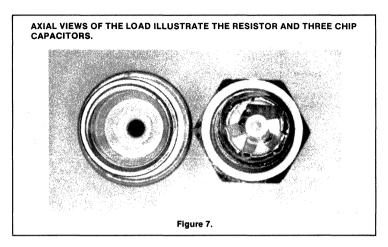

Figure 7

#### **ORDERING INFORMATION**

#### ORDERING INFORMATION

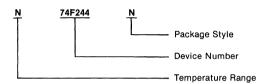

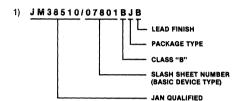

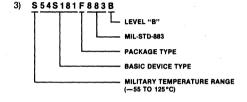

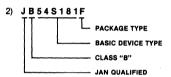

The Signetics FAST products are available in a variety of packages and two temperature ranges. The correct ordering code of part number for the devices is an alphanumeric sequence as explained below. The commercial range (74FXX) devices are

available in plastic dual-in-line (DIP) and SO packages, and the military range (54FXX) devices are available in ceramic DIP and leadless chip carrier (LLCC). All devices are not available in both temperature ranges or all packages. The ordering codes on the individual data sheets indicate the normal or planned availability of

the product. However, the availability of specifc part numbers can be obtained from your local Signetics sales office or franchised distributor.

#### **ORDERING CODE**

| TEMPERATURE RANGE                       | DEVICE NUMBER | PACKAGE STYLE                             |  |

|-----------------------------------------|---------------|-------------------------------------------|--|

| N = Commercial Range<br>0°C to +70°C    | 74F244        | N = Plastic DIP<br>D = SO Plastic         |  |

| S = Military Range<br>- 55°C to + 125°C | 54F244        | F = Ceramic DIP G = Leadless Chip Carrier |  |

#### **PRODUCT STATUS AND DEFINITIONS**

#### **DEFINITION OF TERMS**

| Data Sheet Identification     | Product Status                | Definition                                                                                                                                                                                                                                   |

|-------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preview                       | Formative or In Design        | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                          |

| Advance Information           | Sampling or<br>Pre-Production | This data sheet contains advance information and specifications are subject to change without notice.                                                                                                                                        |

| Preliminary                   | First<br>Production           | This data sheet contains preliminary data and supplementary data will be published at a later data. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| No<br>Identification<br>Noted | Full<br>Production            | This data sheet contains final specifications. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |

# Section 1 Indices

Signetics

#### **NUMERICAL INDEX**

| 74F SERIES        | DESCRIPTION                                                              | PAGE  |

|-------------------|--------------------------------------------------------------------------|-------|

| 74F00             | Quad 2-Input NAND Gate                                                   |       |

| 74F02             | Quad 2-Input NOR Gate                                                    |       |

| 74F04             | Hex Inverter                                                             |       |

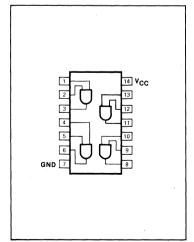

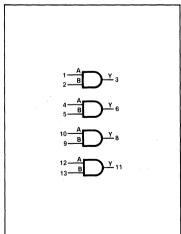

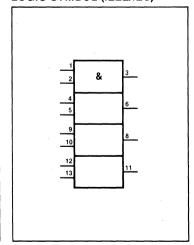

| 74F08             | Quad 2-Input AND Gate                                                    |       |

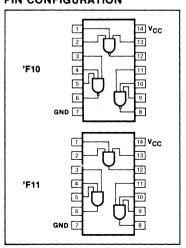

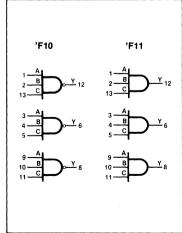

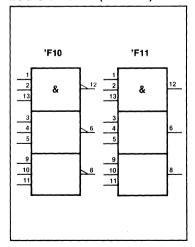

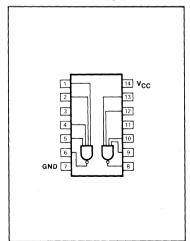

| 74F10             | Triple 3-Input NAND Gate                                                 |       |

| 74F11             | Triple 3-Input AND Gate                                                  |       |

| 74F13             | Dual 4-Input NAND Schmitt Trigger                                        | 5-16  |

| 74F14             | Hex Inverter Schmitt Trigger                                             | 5-19  |

| 74F20             | Dual 4-Input NAND Gate                                                   |       |

| 74F32             | Quad 2-Input OR Gate                                                     |       |

| 74F37             | Quad 2-Input NAND Buffer                                                 |       |

| 74F38             | Quad 2-Input NAND Buffer (Open Collector)                                | 5-31  |

| 74F40             | Dual 4-Input NAND Buffer                                                 | 5-34  |

| 74F64             | 4-2-3-2 Input AND-OR-Invert Gate                                         |       |

| 74F74             | Dual D-Type Flip-Flop                                                    |       |

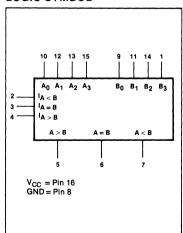

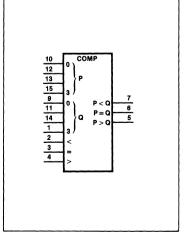

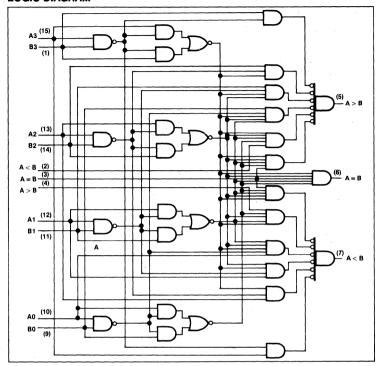

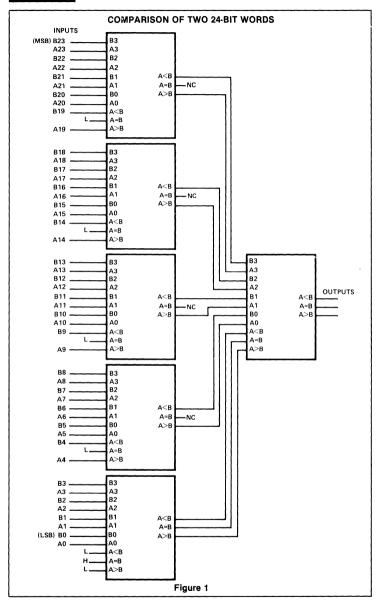

| 74F85             | 4-Bit Magnitude Comparator                                               |       |

| 74F86             | Quad 2-Input Exclusive-OR Gate                                           |       |

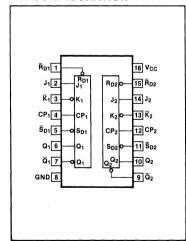

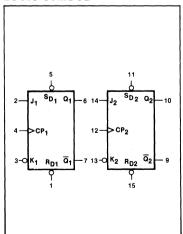

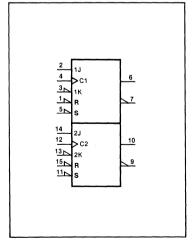

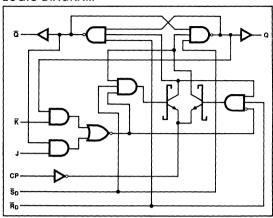

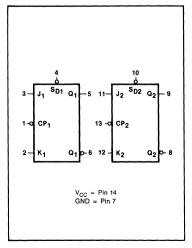

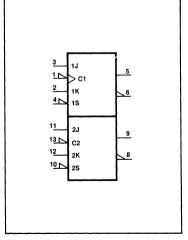

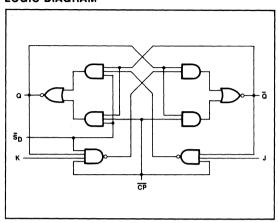

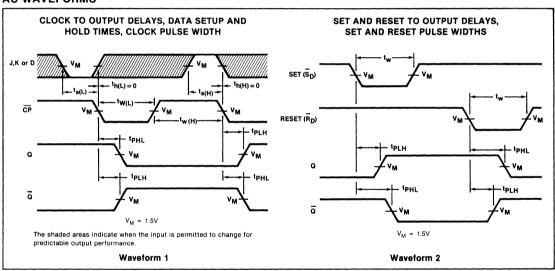

| 74F109            | Dual J-K Positive Edge-Triggered Flip-Flop                               |       |

| 74F112            | Dual J-K Negative Edge-Triggered Flip-Flop.                              |       |

| 74F113            | Dual J-K Negative Edge-Triggered Flip-Flop Without Reset                 |       |

| 74F114            | Dual J-K Negative Edge-Triggered Flip-Flop (With Common Clock and Reset) | 5-69  |

| 74F132            | Quad 2-Input NAND Schmitt Trigger                                        |       |

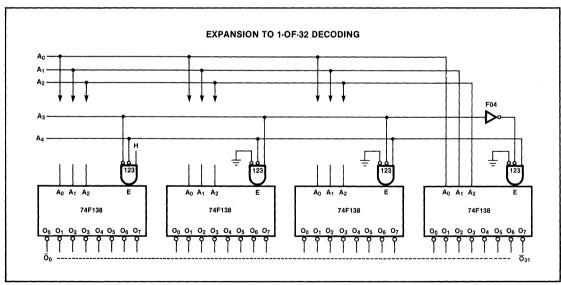

| 74F138            | 1-of-8 Decoder/Demultiplexer                                             |       |

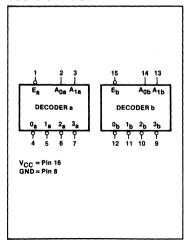

| 74F139            | Dual 1-of-4 Decoder/Demultiplexer                                        |       |

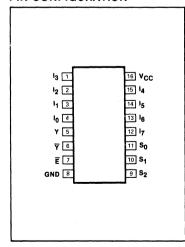

| 74F148            | 8-Input Priority Encoder                                                 |       |

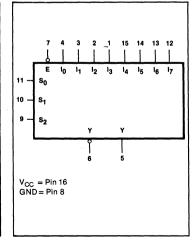

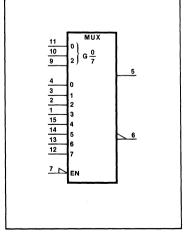

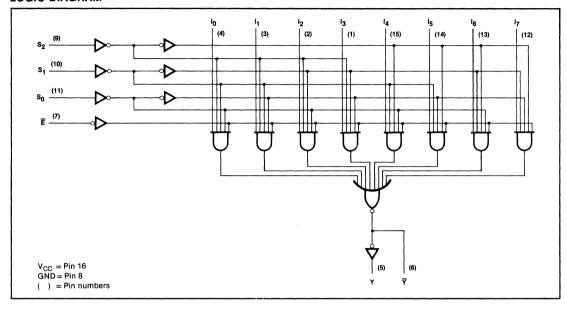

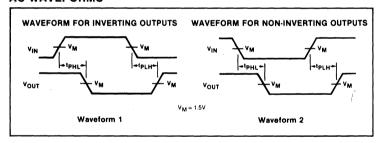

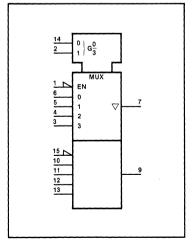

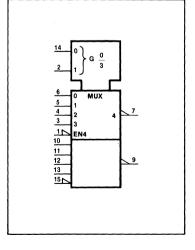

| 74F151            | 8-Input Multiplexer                                                      |       |

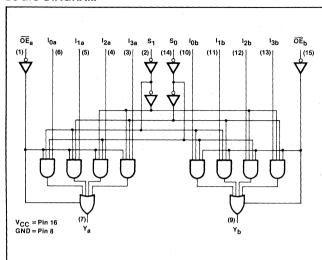

| 74F153            | Quad 2-Input Data Selector/Multiplexer (Non-Inverted)                    |       |

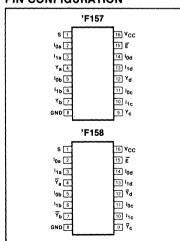

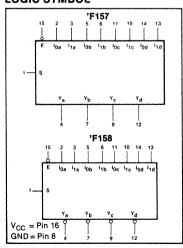

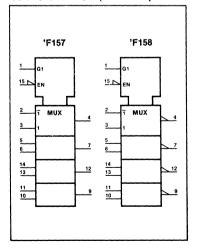

| 74F157<br>74F158  | Quad 2-Input Data Selector/Multiplexer (Nor-Inverted)                    |       |

| 74F156<br>74F160A | Synchronous BCD Decade Counter, Asynchronous Reset                       | 5-103 |

| 74F160A           | Synchronous Binary Counter, Asynchronous Reset                           | 5-103 |

| 74F161A           | Synchronous BCD Decade Counter, Synchronous Reset                        |       |

| 74F162A           | Synchronous Binary Counter, Synchronous Reset                            |       |

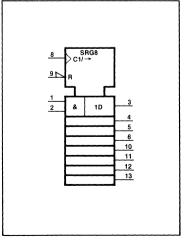

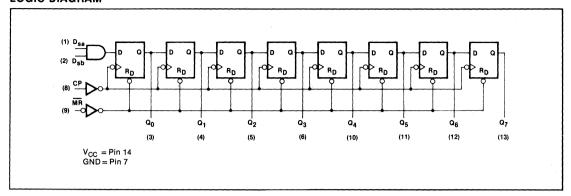

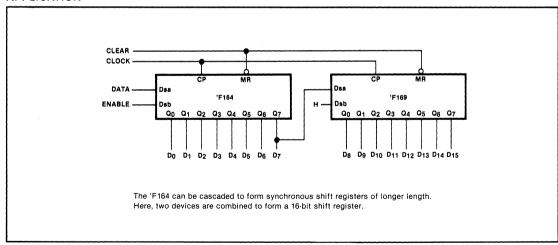

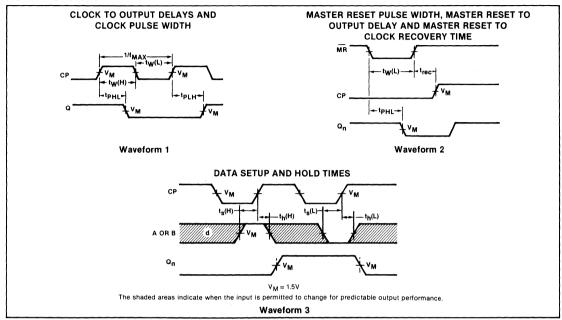

| 74F163A           | 8-Bit Serial-In Parallel-Out Shift Register                              | 5-111 |

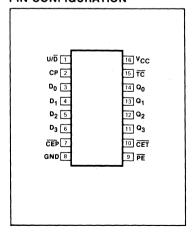

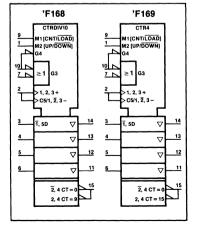

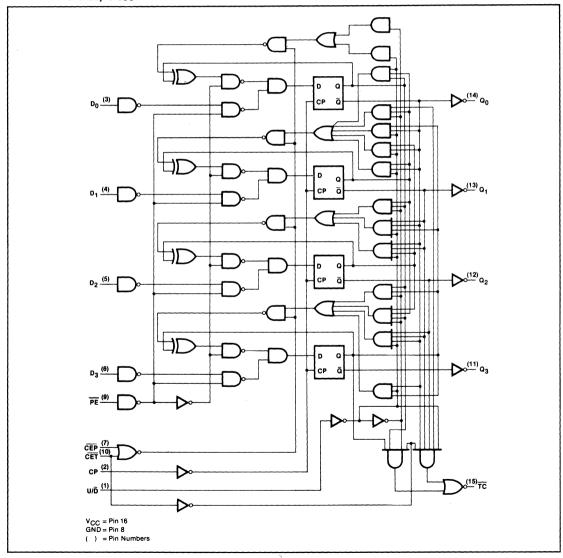

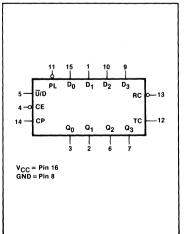

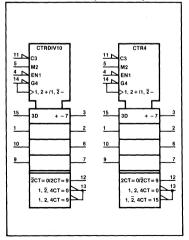

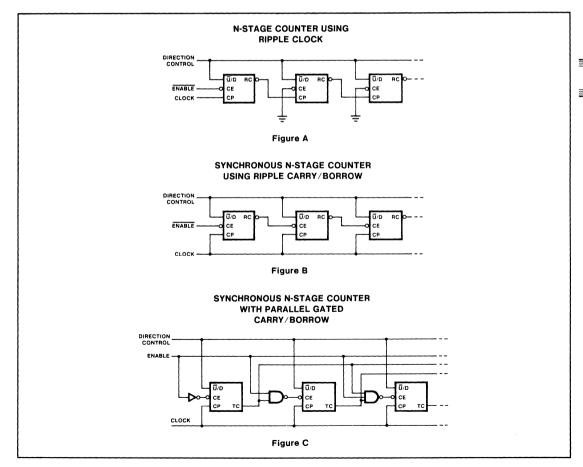

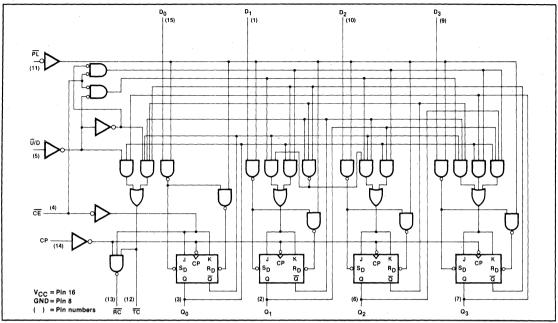

| 74F168            | 4-Bit Up/Down BCD Decade Synchronous Counter.                            | 5-116 |

| 74F169            | 4-Bit Up/Down Binary Synchronous Counter                                 |       |

| 74F174            | Hex D Flip-Flop                                                          |       |

| 74F175            | Quad D Flip-Flop                                                         |       |

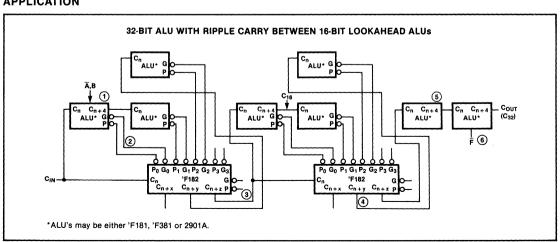

| 74F181            | 4-Bit Arithmetic Logic Unit                                              | 5-133 |

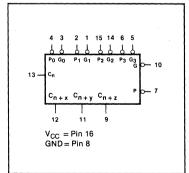

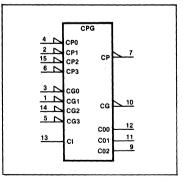

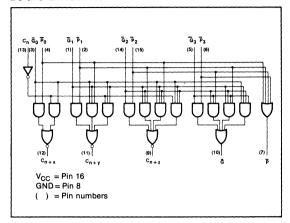

| 74F182            | Carry Lookahead Generator                                                | 5-140 |

| 74F190            | Asynchronous Presettable BCD/Decade Up/Down Counter                      | 5-144 |

| 74F191            | Asynchronous Presettable 4-Bit Binary Up/Down Counter                    |       |

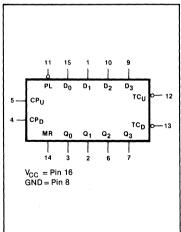

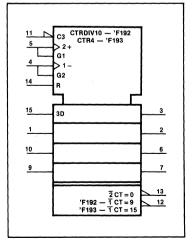

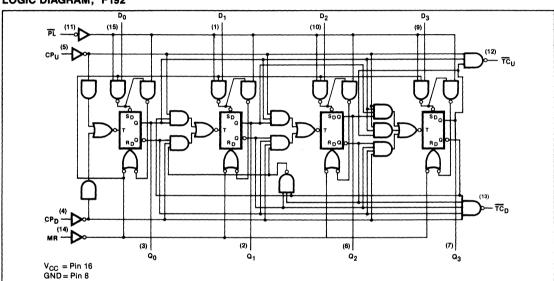

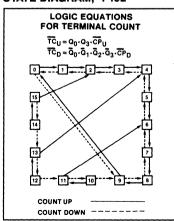

| 74F192            | Synchronous Presettable BCD Decade Up/Down Conter.                       |       |

| 74F193            | Synchronous Presettable 4-Bit Binary Up/Down Counter.                    |       |

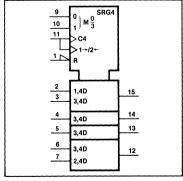

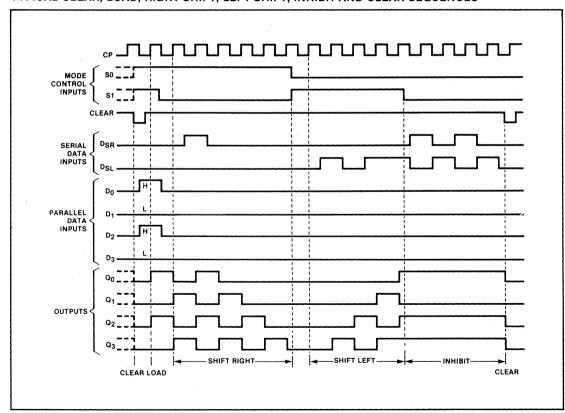

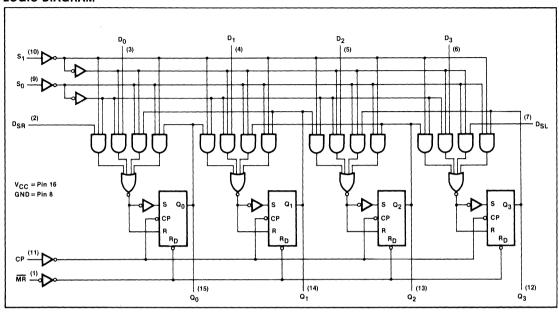

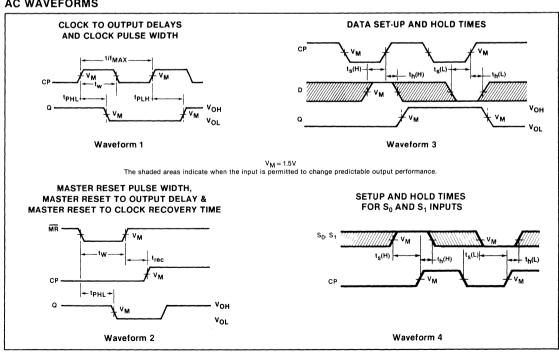

| 74F194            | 4-Bit Bidirectional Universal Shift Register                             |       |

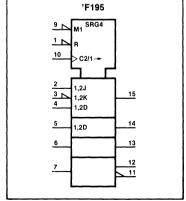

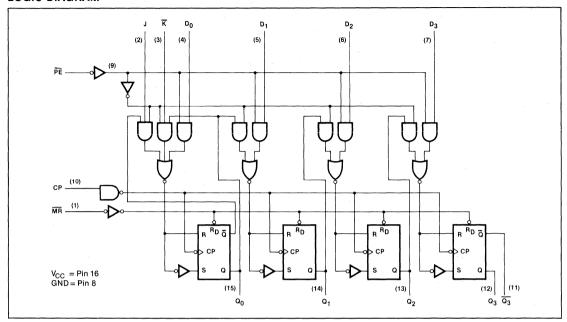

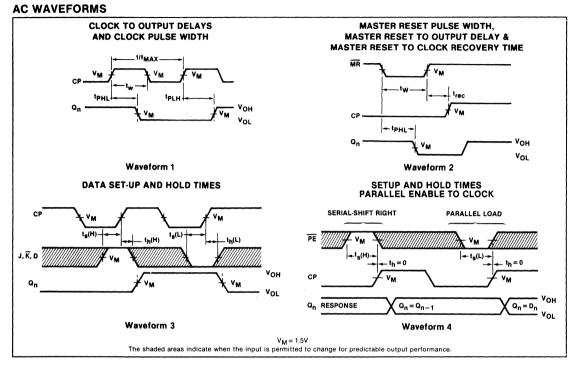

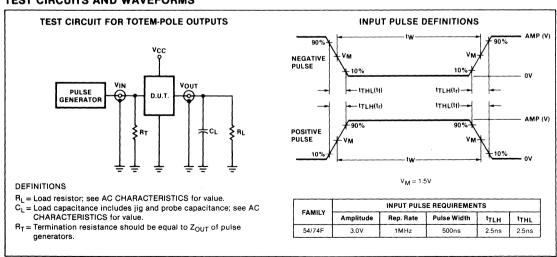

| 74F195            | 4-Bit Parallel Access Shift Register.                                    |       |

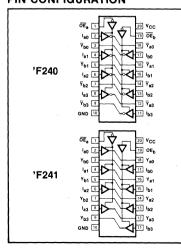

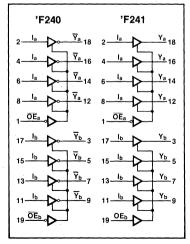

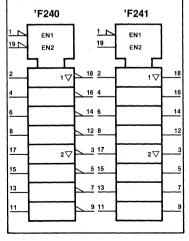

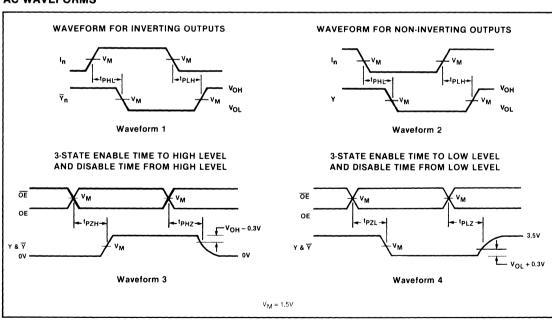

| 74F240            | Octal Inverter Buffer (3-State)                                          |       |

| 74F241            | Octal Buffer (3-State)                                                   | 5-170 |

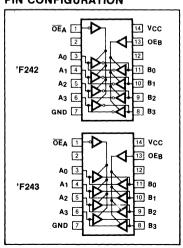

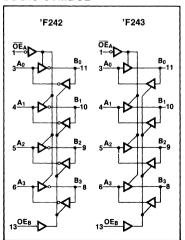

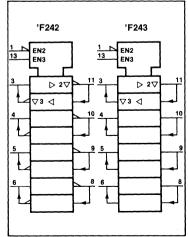

| 74F242            | Quad Transceiver, Inverting (3-State)                                    | 5-175 |

| 74F243            | Quad Transceiver (3-State)                                               | 5-175 |

| 74F244            | Octal Buffer (3-State).                                                  | 5-180 |

| 74F245            | Octal Transceiver (3-State)                                              | 5-184 |

| 74F251            | 8-Input Multiplexer (3-State)                                            | 5-188 |

| 74F253            | Dual 4-Input Multiplexer (3-State)                                       | 5-193 |

| 74F256            | Dual 4-Bit Addressable Latch                                             |       |

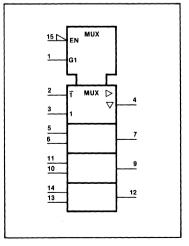

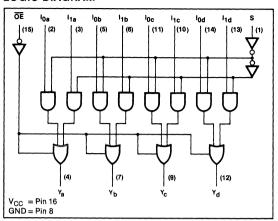

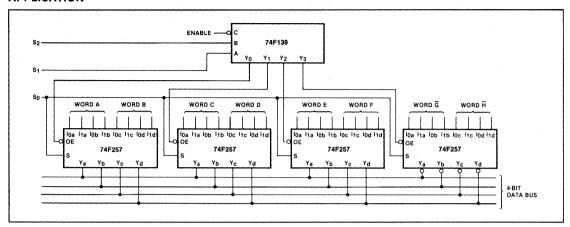

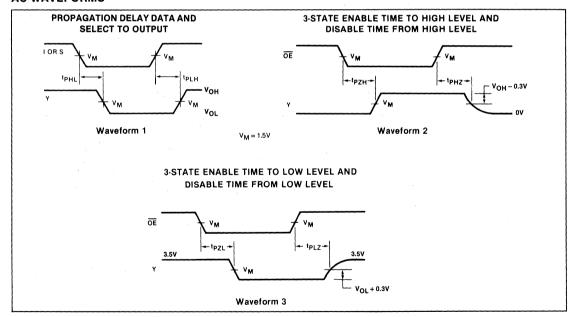

| 74F257            | Quad 2-Line to 1-Line Data Selector/Multiplexer (3-State)                | 5-203 |

| 74F258            | Quad 2-Line to 1-Line Data Selector/Multiplexer (3-State)                | 5-208 |

| 74F259            | 8-Bit Addressable Latch                                                  |       |

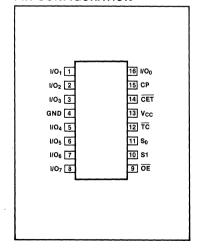

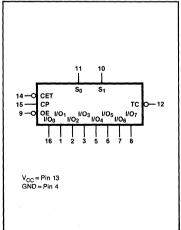

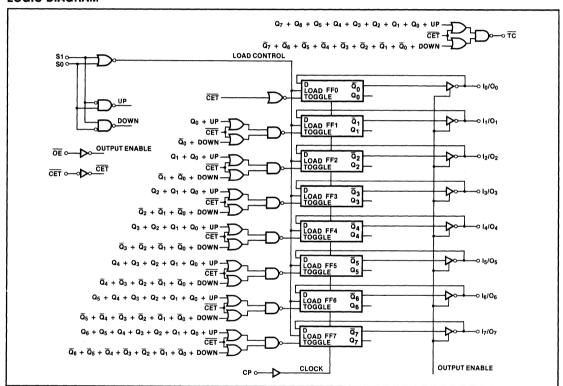

| 74F269            | 8-Bit Bidirectional Binary Counter                                       |       |

| 74F273            | Octal D Flip-Flop                                                        | 5-223 |

#### **NUMERICAL INDEX**

| 74F SERIES | DESCRIPTION                                                                                   | PAGE  |

|------------|-----------------------------------------------------------------------------------------------|-------|

| 74F280A    | 9-Bit Odd/Even Parity Generator/Checker                                                       | 5-227 |

| 74F283     | 4-Bit Binary Full Adder With Fast Carry                                                       | 5-231 |

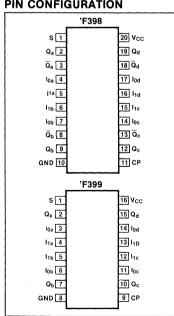

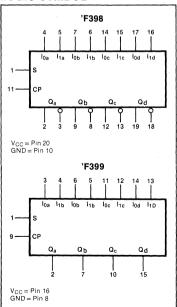

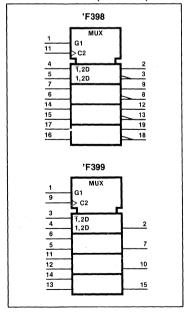

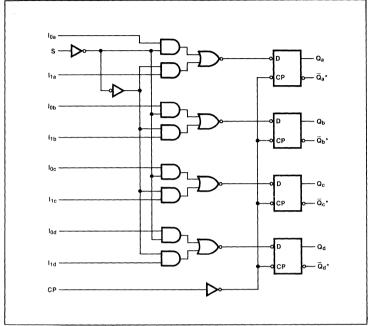

| 74F298     | Quad 2-Input Multiplexer With Storage                                                         | 5-236 |

| 74F299     | 8-Input Universal Shift/Storage Register (3-State)                                            | 5-240 |

| 74F322     | 8-Input Serial/Parallel Register With Sign Extend (3-State)                                   | 5-246 |

| 74F323     | 8-Input Universal Shift/Storage Register With Synchronous Reset and Common I/O Pins (3-State) | 5-253 |

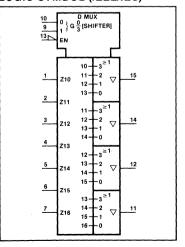

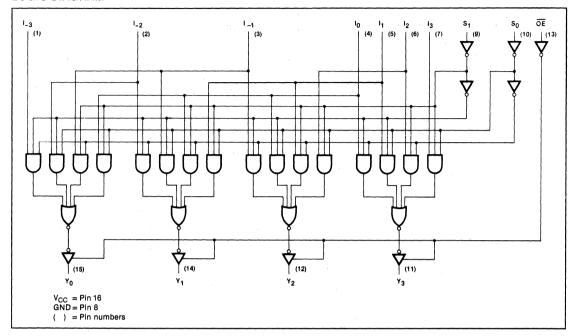

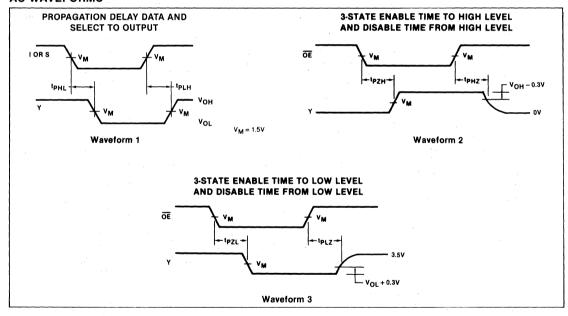

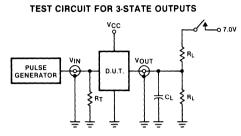

| 74F350     | 4-Bit Shifter (3-State)                                                                       |       |

| 74F352     | Dual 4-Line to 1-Line Multiplexer                                                             | 5-265 |

| 74F353     | Dual 4-Input Multiplexer (3-State)                                                            | 5-269 |

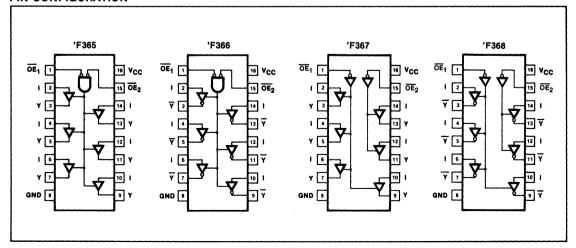

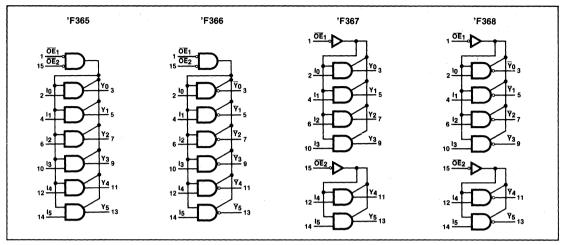

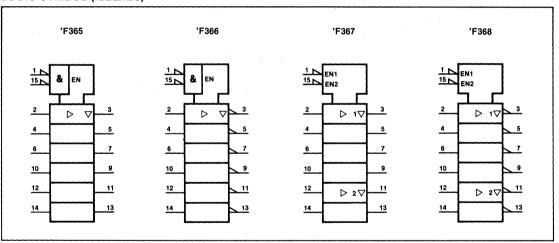

| 74F365     | Hex Buffer Driver (3-State)                                                                   | 5-273 |

| 74F366     | Hex Inverter Buffer (3-State)                                                                 | 5-273 |

| 74F367     | Hex (Dual + Quad) Buffer Driver (3-State)                                                     | 5-273 |

| 74F368     | Hex (Dual + Quad) Inverter Buffer (3-State)                                                   | 5-273 |

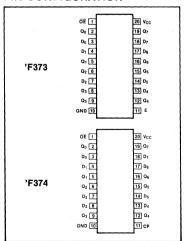

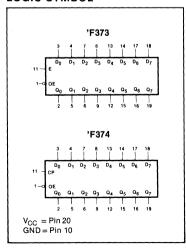

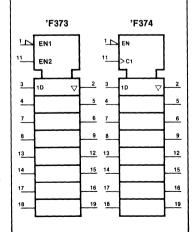

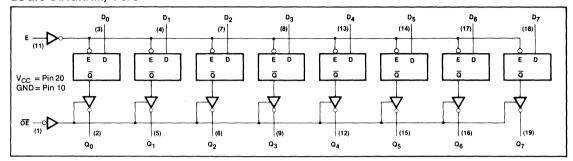

| 74F373     | Octal Transparent Latch (3-State)                                                             | 5-278 |

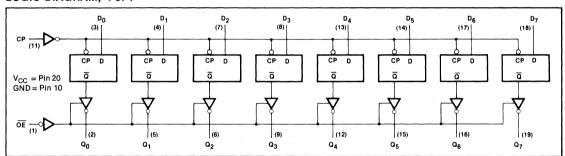

| 74F374     | Octal D Flip-Flop (3-State)                                                                   |       |

| 74F377     | Octal D Flip-Flop With Clock Enable                                                           |       |

| 74F378     | Hex D Flip-Flop With Clock Enable                                                             |       |

| 74F379     | Quad Parallel Register (With Enable)                                                          |       |

| 74F395     | 4-Bit Cascadable Shift Register (3-State)                                                     |       |

| 74F398     | Quad 2-Port Register With True and Complement Outputs                                         |       |

| 74F399     | Quad 2-Port Register.                                                                         |       |

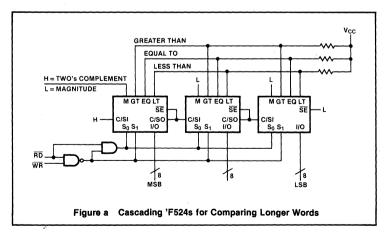

| 74F521     | 8-Bit Identity Comparator                                                                     |       |

| 74F524     | 8-Bit Registered Comparator (Open-Collector + 3-State)                                        | 5-311 |

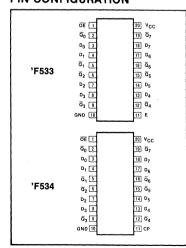

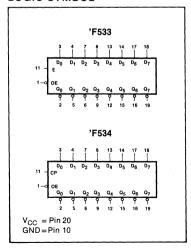

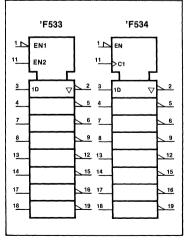

| 74F533     | Octal Transparent Latch (3-State)                                                             |       |

| 74F534     | Octal D Flip-Flop (3-State)                                                                   |       |

| 74F545     | Octal Bidirectional Transceiver (With 3-State Inputs/Outputs)                                 |       |

| 74F579     | 8-Bit Bidirectional Binary Counter (3-State)                                                  |       |

| 74F588     | Octal Bidirectional Transceiver With IEEE-488 Termination Resistors (3-State Inputs/Outputs)  |       |

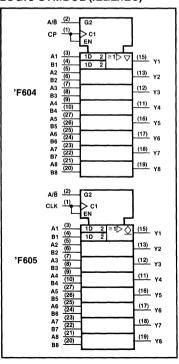

| 74F604     | Dual Octal Register (3-State)                                                                 |       |

| 74F605     | Dual Octal Register (Open-Collector)                                                          |       |

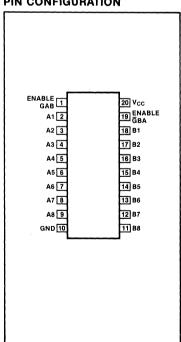

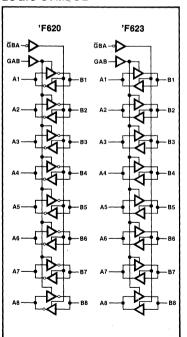

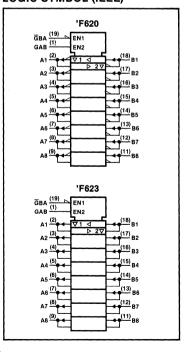

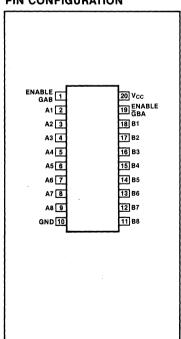

| 74F620     | Octal Bus Transceiver, Inverting (3-State)                                                    |       |

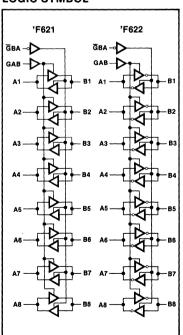

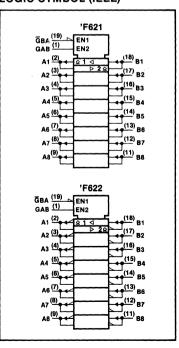

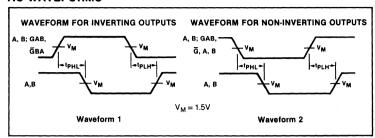

| 74F621     | Octal Bus Transceiver, Non-Inverting (Open Collector).                                        |       |

| 74F622     | Octal Bus Transceiver, Inverting (Open Collector)                                             |       |

| 74F623     | Octal Bus Transceiver, Non-Inverting (3-State)                                                |       |

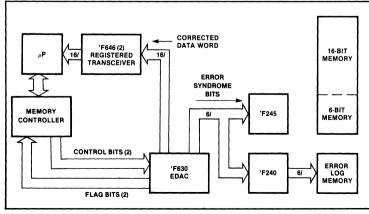

| 74F630     | 16-Bit Parallel Error Detection and Correction Circuit (3-State)                              |       |

| 74F631     | 16-Bit Parallel Error Detection and Correction Circuit (Open Collector)                       |       |

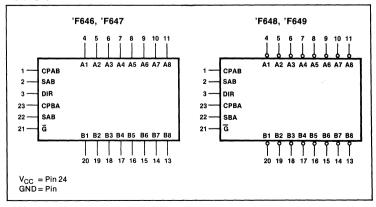

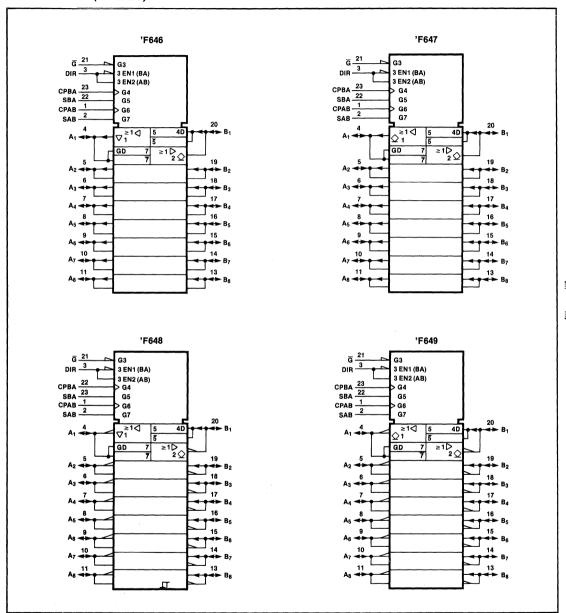

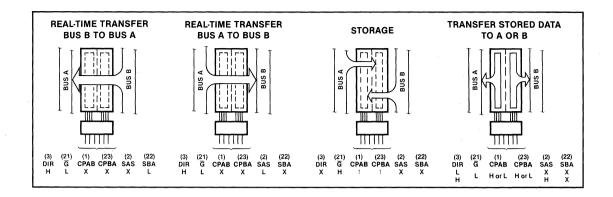

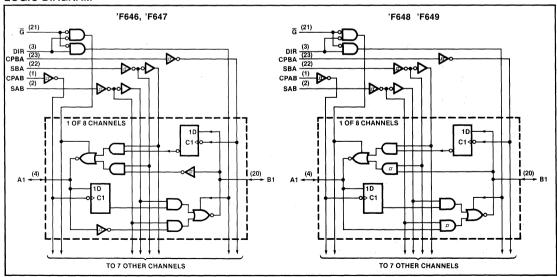

| 74F646     | Octal Transceiver/Register, Non-Inverting (3-State)                                           |       |

| 74F647     | Octal Transceiver/Register, Non-Inverting (Open Collector)                                    |       |

| 74F648     | Octal Transceiver/Register, Inverting (3-State)                                               |       |

| 74F649     | Octal Transceiver/Register, Inverting (Open Collector).                                       |       |

| 74F655     | Octal Buffer/Line Driver With Parity, Inverting (3-State)                                     |       |

| 74F656     | Octal Buffer/Line Driver With Parity, Non-Inverting (3-State)                                 |       |

| 74F657     | Octal Bidirectional Transceiver With 8-Bit Parity Generator/Checker (3-State)                 |       |

| 74F673     | 16-Bit Shift Register (Serial-In/Serial-Parallel Out).                                        |       |

| 74F674     | 16-Bit Shift Register (Serial-Parallel In/Serial-Out), 3-State.                               |       |

| 74F675     | 16-Bit Shift Register (Serial-In/Serial-Parallel Out)                                         |       |

| 74F676     | 16-Bit Shift Register (Parallel-In to Serial-Out, Serial-In to Serial-Out).                   |       |

| 74F779     | 8-Bit Bidirectional Binary Counter (Multiplexed 3-State I/O Ports)                            |       |

| 74F3037*   | Quad 2-Input 30Ω Transmission Line Driver                                                     |       |

| 74F3040*   | Dual 4-Input 30Ω Transmission Line Driver                                                     |       |

<sup>\*</sup>Data sheets soon to be available. Contact nearest Signetics sales office.

#### **AVAILABILITY GUIDE**

| DEVICE                                             | DESCRIPTION                                                                                                                                                             | AVAIL-<br>ABILITY                 | DEVICE                                                   | DESCRIPTION                                                                                                                                                                           | AVAIL-<br>ABILITY                     |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 74F00<br>74F02<br>74F04<br>74F08<br>74F10          | Quad 2-Input NAND Gate Quad 2-Input NOR Gate Hex Inverter Quad 2-Input AND Gate Triple 3-Input NAND Gate                                                                | A<br>A<br>A                       | 74F242<br>74F243<br>74F244<br>74F245<br>74F251           | Quad Bus Transceiver (3-State) Quad Bus Transceiver (3-State) Quad Bus/Line Driver (3-State) Octal Bus Transceiver (3-State) 8-Input Multiplexer (3-State)                            | A<br>A<br>A<br>1H 84<br>1H 84         |

| 74F10<br>74F11<br>74F13<br>74F14<br>74F20<br>74F32 | Triple 3-Input NAND Gate  Dual 4-Input NAND Schmitt Trigger  Hex Schmitt Trigger  Dual 4-Input NAND Gate  Quad 2-Input OR Gate                                          | A<br>A<br>A<br>A                  | 74F251<br>74F253<br>74F256<br>74F257<br>74F258<br>74F259 | Dual 4-Input Multiplexer (3-State) Dual 4-Bit Addressable Latch Quad 2-Input Multiplexer (3-State) Quad 2-Input Multiplexer (3-State) 8-Bit Addressable Latch                         | 2H 84<br>A<br>A<br>A<br>A             |

| 74F37<br>74F38<br>74F40<br>74F64<br>74F74          | Quad 2-Input NAND Buffer<br>Quad 2-Input NAND Buffer, OC<br>Dual 4-Input NAND Buffer<br>4-2-3-2 Input AND/OR Invert Gate<br>Dual D-Type Flip-Flop                       | 1H 84<br>1H 84<br>1H 84<br>A<br>A | 74F269<br>74F273<br>74F280A<br>74F283<br>74F298          | 8-Bit Up/Down Counter (3-State) Octal D Flip-Flop 9-Bit Parity Generator/Checker 4-Bit Adder Quad 2-Input Multiplexer                                                                 | 1H 84<br>1H 84<br>A<br>1985<br>1H 84  |

| 74F85<br>74F86<br>74F109<br>74F112<br>74F113       | 4-Bit Magnitude Comparator<br>Quad 2-Input Exclusive-OR Gate<br>Dual JK Flip-Flop<br>Dual JK Flip-Flop<br>Dual JK Flip-Flop                                             | 1H 84<br>A<br>A<br>2H 84<br>2H 84 | 74F299<br>74F322<br>74F323<br>74F350<br>74F352           | Octal Shift/Storage Register (3-State) Octal Shift/Storage Register (3-State) Octal Shift/Storage Register (3-State) 4-Bit Shifter (3-State) Dual 4-Input Multiplexer (Inverted '153) | 2H 84<br>2H 84<br>2H 84<br>A<br>2H 84 |

| 74F114<br>74F132<br>74F138<br>74F139<br>74F148     | Dual JK Flip-Flop<br>Quad 2-Input NAND Schmitt Trigger<br>1-of-8 Decoder/Demultiplexer<br>Dual 1-of-4 Decoder/Demultiplexer<br>8-Bit Priority Encoder                   | 2H 84<br>A<br>A<br>A<br>2H 84     | 74F353<br>74F365<br>74F366                               | Dual 4-Input Multiplexer (Inverted '253) Hex Buffer with Common Enable (3-State) Hex Inverter with Common Enable (3-State)                                                            | 2H 84<br>1H 84<br>1H 84               |

| 74F151<br>74F153<br>74F157<br>74F158<br>74F160A    | 8-Input Multiplexer Dual 4-Input Multiplexer Quad 2-Input Multiplexer Quad 2-Input Multiplexer Quad 2-Input Multiplexer BCD Decade Counter, Asynch Reset                | 1H 84<br>2H 84<br>A<br>A<br>2H 84 | 74F367<br>74F368<br>74F373<br>74F374<br>74F377           | Hex Buffer, 4-Bit and 2-Bit (3-State) Hex Inverter, 4-Bit and 2-Bit (3-State)  Octal D Latch (3-State) Octal D Flip-Flop (3-State) Octal D-Type Flip-Flop with Enable                 | 1H 84<br>1H 84<br>A<br>A              |

| 74F161A<br>74F162A<br>74F163A<br>74F164            | 4-Bit Binary Counter, Asynch Reset<br>BCD Decade Counter, Synch Reset<br>4-Bit Binary Counter, Synch Reset<br>8-Bit SIPO Shift Register                                 | 2H 84<br>2H 84<br>2H 84<br>2H 84  | 74F378<br>74F379<br>74F381*<br>74F382*                   | Hex D Flip-Flop with Enable Quad D Flip-Flop with Enable  4-Bit Arithmetic Logic Unit 4-Bit Arithmetic Logic Unit                                                                     | 2H 84<br>2H 84<br>1985<br>1985        |

| 74F168<br>74F169<br>74F174                         | 4-Bit Up/Down Decade Counter (3-State)     4-Bit Up/Down Binary Counter (3-State)     Hex D Flip-Flop with Common Master     Reset                                      | 2H 84<br>2H 84<br>2H 84           | 74F384*<br>74F385*<br>74F395                             | 8-Bit Serial/Parallel Two's Complement<br>Multiplier<br>Quad Serial Adder/Subtractor<br>4-Bit Cascadable Shift Register (3-State)                                                     | 1985<br>1985<br>1H 84                 |

| 74F175<br>74F181<br>74F182                         | Quad D Flip-Flop with Common Master<br>Reset<br>4-Bit Arithmetic Logic Unit<br>Carry Lookahead Generator                                                                | 2H 84<br>2H 84<br>2H 84           | 74F398<br>74F399                                         | 4-Bit Flip-Flop, True and Complement Outputs 4-Bit Flip-Flop, True and Complement Outputs Outputs Authorized Puffered Label (2 Chats)                                                 | 2H 84<br>2H 84                        |

| 74F189<br>74F190<br>74F191<br>74F192               | 4-Bit Random Access Memory (3-State) Up/Down Decade Counter Up/Down Binary Counter Up/Down Decade Counter                                                               | 1985<br>2H 84<br>2H 84<br>2H 84   | 74F412<br>74F521<br>74F524<br>74F533                     | Multi-Mode Buffered Latch (3-State) Octal Comparator 8-Bit Register Comparator (OC) Inverting Octal D Latch (3-State)                                                                 | 1985<br>A<br>2H 84                    |

| 74F193<br>74F194                                   | Up/Down Binary Counter  4-Bit Bidirectional Universal Shift Register                                                                                                    | 2H 84<br>A                        | 74F534<br>74F545<br>74F568<br>74F569                     | Inverting Octal D Elip-Flop (3-State) Octal Bus Transceiver (3-State) 4-Bit Binary Up/Down Counter (3-State) 4-Bit Decade Up/Down Counter (3-State)                                   | A<br>1H 84<br>2H 84<br>2H 84          |

| 74F195<br>74F198*<br>74F240<br>74F241              | 4-Bit Parallel Access Shift Register<br>8-Bit Bidirectional Universal Shift<br>Register<br>Octal Inverting Bus/Line Driver (3-State)<br>Octal Bus/Line Driver (3-State) | 1H 84<br>1985<br>A                | 74F589<br>74F588<br>74F595*                              | 8-Bit Up/Down Counter, Common I/O (3-State) GPIB Compatible Octal Transceiver 8-Bit Shift Register with Output Latch                                                                  | 2H 84<br>1H 84<br>1985                |

<sup>\*</sup>Data sheets soon to be available. Contact nearest Signetics sales office.

#### **AVAILABILITY GUIDE**

| DEVICE  | DESCRIPTION                                                       | AVAIL-<br>ABILITY |

|---------|-------------------------------------------------------------------|-------------------|

| 74F597* | 8-Bit Shift Register with Input Latch                             | 1985              |

| 74F598* | 8-Bit Shift Register with Input Latch                             | 1985              |

| 74F604  | Dual 8-Bit Latch (3-State)                                        | 1H 84             |

| 74F605  | Dual 8-Bit Latch (OC)                                             | 1H 84             |

| 74F620  | Octal Bus Transceiver (3-State)                                   | 1H 84             |

| 74F621  | Octal Bus Transceiver (3-State)                                   | 1H 84             |

| 74F622  | Octal Bus Transceiver (OC)                                        | 1H 84             |

| 74F623  | Octal Bus Transceiver (3-State)                                   | 1H 84             |

| 74F630  | Memory Error Detector/Corrector (3-State)                         | 2H 84             |

| 74F631  | Memory Error Detector/Corrector (OC)                              | 2H 84             |

| 74F646  | Octal Bus Transceiver and Register (3-State)                      | 1H 84             |

| 74F647  | Octal Bus Transceiver and Register (OC)                           | 1H 84             |

| 74F648  | Octal Bus Transceiver and Register (3-State)                      | 1H 84             |

| 74F649  | Octal Bus Transceiver and Register (OC)                           | 1H 84             |

| 74F655  | Octal Inverting Buffer with Parity<br>Generator-Checker (3-State) | Α                 |

| DEVICE   | DESCRIPTION                                                        | AVAIL-<br>ABILITY |

|----------|--------------------------------------------------------------------|-------------------|

| 74F656   | Octal Buffer with Parity Generator-<br>Checker (3-State)           | A                 |

| 74F657   | Octal Bus Transceiver with Parity Generator-Checker (3-State)      | 2H 84             |

| 74F673   | 16-Bit Serial-In/Parallel-Out Shift<br>Register (3-State)          | 1985:             |

| 74F674   | 16-Bit Parallel-In/Serial-Out Shift<br>Register (3-State)          | 1985              |

| 74F675   | 16-Bit Serial-In/Parallel-Out Shift<br>Register with SO Capability | 1985              |

| 74F676   | 16-Bit Parallel-In/Serial-Out Shift<br>Register with SO Capability | 1985              |

| 74F779   | 8-Bit Counter (3-State)                                            | 2H 84             |

| 74F784*  | 8-Bit Serial/Parallel Multiplier (with<br>Adder/Subtractor)        | 1985              |

| 74F3037* | Quad 2-Input 30Ω Transmission Line<br>Driver                       | A                 |

| 74F3040* | Dual 4-Input 30Ω Transmission Line<br>Driver                       | A                 |

#### **FAST ORDERING INFORMATION**

| PACKAGES                    | COMMERCIAL RANGES  V <sub>CC</sub> = 5V ± 5%; T <sub>A</sub> = 0°C to + 70°C | MILITARY RANGES  V <sub>CC</sub> = 5V ± 10%; T <sub>A</sub> = -55°C to + 125°C |

|-----------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Plastic DIP                 | N74FN                                                                        | ·                                                                              |

| Plastic SO <sup>(1)</sup>   | N74FD                                                                        |                                                                                |

| Ceramic DIP                 |                                                                              | S54FF                                                                          |

| Ceramic LLCC <sup>(2)</sup> |                                                                              | S54FG                                                                          |

NOTE

SO package is surface-mounted micro-miniature DIP available 1984. LLCC is ceramic surface-mounted leadless chip carrier.

<sup>\*</sup>Data sheets soon to be available. Contact nearest Signetics sales office.

# 1

#### **FUNCTION SELECTION GUIDE**

#### **GATES**

| FUNCTION                      | DEVICE NUMBER |

|-------------------------------|---------------|

| Inverters                     |               |

| Hex Inverter                  | 54/74F04      |

| Hex Inverter Schmitt Trigger  | 74F14         |

| NAND                          |               |

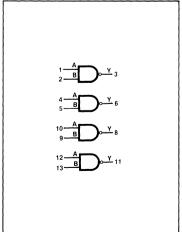

| Quad 2-Input                  | 54/74F00      |

| Triple 3-Input                | 54/74F10      |

| Dual 4-Input, Schmitt Trigger | 74F13         |

| Dual 4-Input                  | 54/74F20      |

| Quad 2-Input, Schmitt Trigger | 74F132        |

| AND                           |               |

| Quad 2-Input                  | 54/74F08      |

| Triple 3-Input                | 54/74F11      |

| NOR                           |               |

| Quad 2-Input                  | 54/74F02      |

| OR                            |               |

| Quad 2-Input                  | 54/74F32      |

| Exclusive-OR                  |               |

| Quad                          | 54/74F86      |

| Combination Gates             |               |

| 4-2-3-2 Input AND-OR-Invert   | 74F64         |

#### **DUAL FLIP-FLOPS**

| FUNCTION | DEVICE NUMBER | CLOCK EDGE | SET | CLEAR |

|----------|---------------|------------|-----|-------|

| D        | 54/74F74      |            | LOW | LOW   |

| JK       | 54/74F109     | 7          | LOW | LOW   |

| JK       | 74F112        | ı.         | LOW | LOW   |

| JK       | 74F113        | 2          | LOW |       |

| JK       | 74F114        | ٦.         | LOW | LOW   |

#### **MULTIPLE FLIP-FLOPS**

| FUNCTION            | DEVICE NUMBER | RESET LEVEL | CLOCK EDGE | OUTPUT    |

|---------------------|---------------|-------------|------------|-----------|

| Quad D              | 54/74F175     | LOW         |            | True Comp |

| Quad D with Enable  | 74F379        |             |            | True Comp |

| Hex D               | 74F174        | LOW         | 7          | True      |

| Hex D with Enable   | 74F378        |             | <b>.</b>   | True      |

| Octal D             | 74F273        | LOW         |            | True      |

| Octal D, 3-State    | 54/74F374     |             |            | True      |

| Octal D, 3-State    | 74F534        |             |            | Comp      |

| Octal D with Enable | 74F377        |             |            | True      |

#### OTHER REGISTERS, REGISTER FILES

| FUNCTION    | DEVICE NUMBER | BITS | SERIAL ENTRY | PARALLEL ENTRY | CLOCK |

|-------------|---------------|------|--------------|----------------|-------|

| Quad 2 Port | 74F298        | 4×2  |              | 2D (mux)       | T.    |

| Quad 2 Port | 74F398        | 4×2  |              | 2D (mux)       | 7     |

| Quad 2 Port | 74F399        | 4×2  |              | 2D (mux)       | 7     |

#### **FUNCTION SELECTION GUIDE**

#### **LATCHES**

| FUNCTION                     | DEVICE NUMBER | COMMON CLEAR (LEVEL)                    | ENABLE INPUT (LEVEL) | OUTPUT |

|------------------------------|---------------|-----------------------------------------|----------------------|--------|

| Dual 4-Bit Addressable       | 74F256        | LOW                                     | 1 (L)                | True   |

| Dual 4-Bit Addressable       | 74F259        | LOW                                     | 1 (H)                | True   |

| Octal, 3-State               | 54/74F373     |                                         | 1 (H)                | True   |

| Octal Inverting, 3-State     | 74F533        | # · · · · · · · · · · · · · · · · · · · | 1 (H)                | Comp   |

| Multi-Mode Buffered, 3-State | 74F412*       | LOW                                     | 1 (L), 2 (H)         | True   |

#### MULTIPLEXERS

| FUNCTION              | DEVICE NUMBER | ENABLE INPUT (LEVEL) | SELECT INPUTS | OUTPUT    |

|-----------------------|---------------|----------------------|---------------|-----------|

| Quad 2-Input          | 54/74F157     | 1 (L)                | 1             | True      |

| Quad 2-Input          | 74F158        | 1 (L)                | 1             | True      |

| Quad 2-Input, 3-State | 54/74F257     |                      | 1             | True      |

| Quad 2-Input, 3-State | 74F258        |                      | 1             | Comp      |

| Dual 4-Input          | 54/74F153     | 2 (L)                | 2             | True Comp |

| Dual 4-Input          | 74F352        | 2                    | 2             | Comp      |

| Dual 4-Input, 3-State | 54/74F253     | ·                    | 2             | True      |

| Dual 4-Input, 3-State | 74F353        | 2                    | 2             | Comp      |

| 8-Input               | 74F151        | 1 (L)                | 3             | True Comp |

| 8-Input, 3-State      | 54/74F251     | 1                    | - 1           | True Comp |

#### **DECODER/DEMULTIPLEXERS**

| FUNCTION    | DEVICE NUMBER | ADDRESS INPUTS | ENABLE LEVEL | OUTPUT LEVEL  |

|-------------|---------------|----------------|--------------|---------------|

| Dual 1-of-4 | 74F139        | 2+2            | 1 (L)+1 (L)  | 4 (L) + 4 (L) |

| 1-of-8      | 54/74F138     | 3              | 2 (L), 1 (H) | 8 (L)         |

#### **BUFFERS, DRIVERS AND TRANSCEIVERS**

| FUNCTION                              | DEVICE NUMBER | OUTPUT |

|---------------------------------------|---------------|--------|

| Quad 2-Input NAND Buffer              | 74F37         | Comp   |

| Quad 2-Input NAND Buffer, OC          | 74F38         | Comp   |

| Dual 4-Input NAND Buffer              | 74F40         | Comp   |

| Quad 2-Input NAND Transmission Driver | 74F3037*      | Comp   |

| Dual 4-Input NAND Transmission Driver | 74F3040*      | Comp   |

| Octal Transceiver                     | 74F621        | True   |

| Octal Transceiver                     | 74F622        | Comp   |

| Octal Transceiver and Registers       | 74F647        | True   |

| Octal Transceiver and Registers       | 74F649        | Comp   |

<sup>\*</sup>Data sheets soon to be available. Contact nearest Signetics sales office.

#### **FUNCTION SELECTION GUIDE**

#### **SHIFT REGISTERS**

| FUNCTION                                                | DEVICE NUMBER | BITS | SERIAL ENTRY                      | PARALLEL ENTRY                                                      | CLOCK    |

|---------------------------------------------------------|---------------|------|-----------------------------------|---------------------------------------------------------------------|----------|

| Serial-In/Parallel-Out                                  | 74F164        | 8    | D <sub>sa</sub> , D <sub>sb</sub> |                                                                     |          |

| Serial-In/Parallel-Out Output Latch, 3-State            | 74F595*       | 8    | D <sub>s</sub>                    |                                                                     |          |

| Serial-In/Serial-Out/Parallel-Out, 3-State              | 74F673        | 16   | SI/O                              |                                                                     | l        |

| Serial-In/Serial-Out/Parallel-Out                       | 74F675        | 16   | D                                 |                                                                     | 52       |

| Serial-In/Parallel-In/Serial-Out, Parallel-Out          | 74F195        | 4    | J,K                               | 4D                                                                  |          |

| Serial-In/Parallel-In/Serial-Out, Parallel-Out          | 74F598*       | 8    | D <sub>so</sub> , D <sub>si</sub> | 8 1/0                                                               |          |

| Serial-In/Parallel-In/Serial-Out                        | 74F674        | 16   | SI/O                              | SI/O, 16D                                                           | 1 7      |

| Serial-In/Parallel-In/Serial-Out                        | 74F676        | 16   | SI                                | 16D                                                                 | 5        |

| Serial-In/Parallel-In/Parallel-Out Shift Right, 3-State | 74F395        | 4    | D <sub>s</sub>                    | 4D                                                                  |          |

| Serial-In/Parallel-In/Serial-Out, Parallel-Out, 3-State | 74F322        | 8    | $D_0, D_1$                        | 8 I/O                                                               |          |

| Serial-In/Parallel-In/Parallel-Out                      | 54/74F194     | - 4  | D <sub>sr</sub> , D <sub>si</sub> | 4D                                                                  | <u> </u> |

| Serial-In/Parallel-In/Parallel-Out, Bidirectional       | 74F198*       | 8    | D <sub>sr</sub> , D <sub>si</sub> | 8D                                                                  | 5        |

| Serial-In/Parallel-In/Serial-Out, Parallel-Out, 3-State | 74F299        | 8    | D <sub>s0</sub> , D <sub>s7</sub> | 8 I/O                                                               |          |

| Serial-In/Parallel-In/Serial-Out, Parallel-Out, 3-State | 74F323        | 8    | D <sub>s0</sub> , D <sub>s7</sub> | 8 I/O                                                               |          |

| Parallel-In/Serial-Out Input Latch                      | 74F597*       | 8    | D <sub>s</sub>                    | 8D                                                                  |          |

| Parallel-In/Parallel-Out, 3-State                       | 74F350        | 4    | 1_3-1+3                           | 4Y                                                                  |          |

| Parallel-In/Parallel-Out, 3-State                       | 74F604        | 16   |                                   | A <sub>1</sub> -A <sub>8</sub> , B <sub>1</sub> -B <sub>8</sub>     |          |

| Parallel-In/Parallel-Out, OC                            | 74F605        | 16   | }                                 | A <sub>1</sub> -A <sub>8</sub> , B <sub>1</sub> -B <sub>8</sub>     |          |

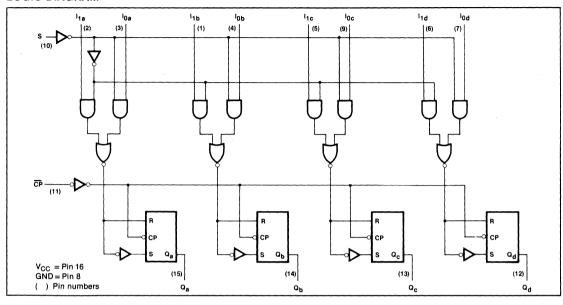

| Parallel-In/Parallel-Out, True and Complement Output    | 74F398        | 8    | s                                 | I <sub>0a</sub> -I <sub>0d</sub> , I <sub>1a</sub> -I <sub>1d</sub> |          |

| Parallel-In/Parallel-Out                                | 74F399        | 8    | S                                 | I <sub>0a</sub> -I <sub>0d</sub> , I <sub>1a</sub> -I <sub>1d</sub> | 7        |

#### **COUNTERS**

| FUNCTION                     | DEVICE NUMBER | MODULUS | PARALLEL ENTRY | PRESETTABLE | CLOCK EDGE |

|------------------------------|---------------|---------|----------------|-------------|------------|

| Synchronous                  | 74F160        | 10      | S              | Х           | 7          |

| Synchronous                  | 74F161        | 16      | s              | X           |            |

| Synchronous                  | 74F162        | 10      | S              | X           | 1 5        |

| Synchronous                  | 74F163        | 16      | S              | X           |            |

| Up/Down                      | 74F168        | 10      | s              | X           | 1 5        |

| Up/Down                      | 74F169        | 16      | S              | X           | 5          |

| Up/Down                      | 74F190        | 10      | Α              | X           |            |

| Up/Down                      | 74F191        | 16      | Α              | X           |            |

| Up/Down                      | 74F192        | 10      | Α              | x           |            |

| Up/Down                      | 74F193        | 16      | Α              | x           |            |

| Up/Down                      | 74F269        | 8       | s              | X           | 1 5        |

| Up/Down                      | 74F579        | 8       | S (I/O)        | X           |            |

| Up/Down, 3-State Multiplexed | 74F779        | 8       | S (I/O)        | X           | 1 5        |

#### THREE-STATE BUFFERS, DRIVERS AND TRANSCEIVERS

| FUNCTION                                              | DEVICE NUMBER | OUTPUT |

|-------------------------------------------------------|---------------|--------|

| Quad Bus Transceiver                                  | 74F242        | Comp   |

| Quad Bus Transceiver                                  | 74F243        | True   |

| Hex Buffer                                            | 74F365        | True   |

| Hex Inverter                                          | 74F366        | Comp   |

| Hex Buffer, 4-Bit and 2-Bit                           | 74F367        | True   |

| Hex Inverter, 4-Bit and 2-Bit                         | 74F368        | Comp   |

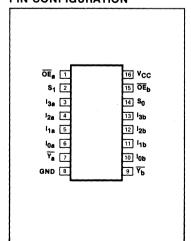

| Octal Buffer                                          | 54/74F240     | Comp   |

| Octal Buffer                                          | 54/74F241     | True   |

| Octal Buffer                                          | 54/74F244     | True   |

| Octal Buffer with Parity                              | 74F655        | Comp   |

| Octal Buffer with Parity                              | 74F656        | True   |

| Octal Transceiver                                     | 74F245        | True   |

| Octal Transceiver                                     | 74F545        | True   |

| Octal Transceiver with IEEE-488 Termination Resistors | 74F588        | True   |

| Octal Transceiver                                     | 74F620        | Comp   |

| Octal Transceiver                                     | 74F623        | True   |

| Octal Transceiver with Parity                         | 74F657        | True   |

| Octal Transceiver/Register                            | 74F646        | True   |

| Octal Transceiver/Register                            | 74F648        | Comp   |

<sup>\*</sup>Data sheets soon to be available. Contact nearest Signetics sales office.

#### **FUNCTION SELECTION GUIDE**

#### **PRIORITY ENCODERS**

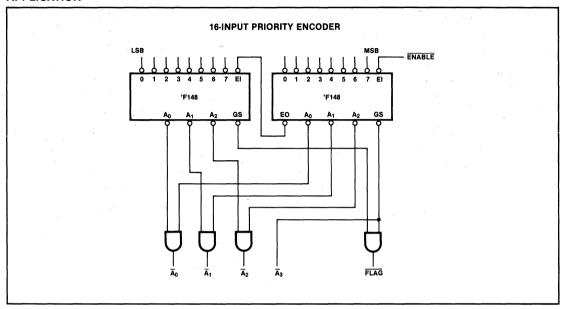

| FUNCTION | DEVICE NUMBER | INPUT ENABLE (LEVEL) | INPUT/OUTPUT (LEVEL) |

|----------|---------------|----------------------|----------------------|

| 8-to-3   | 74F148        | LOW                  | Active-LOW           |

#### **ARITHMETIC FUNCTIONS**

| FUNCTION                                            | DEVICE NUMBER |

|-----------------------------------------------------|---------------|

| 4-Bit ALU                                           | 74F181        |

| 4-Bit ALU                                           | 74F381*       |

| 4-Bit ALU with Overflow Output for Two's Complement | 74F382*       |

| 4-Bit Binary Full Adder with FAST Carry             | 54/74F283     |

| Lookahead Carry Generator                           | 74F182        |

| Quad Serial Adder/Subtractor                        | 74F385*       |

#### **COMPARATORS**

| FUNCTION                  | DEVICE NUMBER |

|---------------------------|---------------|

| 4-Bit Comparator          | 74F85         |

| 8-Bit Comparator          | 54/74F521     |

| 8-Bit Register Comparator | 74F524        |

#### **PARITY**

| FUNCTION                                | DEVICE NUMBER |

|-----------------------------------------|---------------|

| 9-Bit Odd/Even Parity Generator/Checker | 54/74F280A    |

#### **SPECIAL FUNCTIONS**

| FUNCTION                                          | DEVICE NUMBER |  |

|---------------------------------------------------|---------------|--|

| 16-Bit Error Detection                            | 74F630        |  |

| 16-Bit Error Detection/Correction Circuit         | 74F631        |  |

| 64-Bit RAM                                        | 74F189        |  |

| 8-Bit Serial/Parallel Two's Complement Multiplier | 74F384*       |  |

| 2-Bit Serial/Parallel (with Adder/Subtractor)     | 74F784*       |  |

<sup>\*</sup>Data sheets soon to be available. Contact nearest Signetics sales office.

# Section 2 Quality and Reliability

#### SIGNETICS LOGIC QUALITY

Signetics' Logic Division has put together a winning process for manufacturing ICs with built-in quality and reliability. We're striving to ship zero defects, and current quality levels demonstrate our commitment to this goal. Quality guarantees are continually being reviewed to reflect the tangible improvements we have made.

The digital ICs produced in the Logic Division must meet rigid criteria as defined by our design rules and evaluated in a thorough product characterization process. The capabilities of our manufacturing process are measured and the results evaluated and reported through our corporatewide data base system, QA05. The SURE (Systematic Uniform Reliability Evaluation) program monitors the performance of our product in a variety of accelerated environmental stress conditions. All of these programs and systems are intended to prevent product-related problems and to inform our customers and employees of our progress in achieving zero defects.

# RELIABILITY BEGINS WITH THE DESIGN

Reliability and quality must begin with design. No amount of extra testing or inspection will produce reliable ICs from a design that is inherently unreliable. Signetics follows very strict design and layout practices with its digital circuits. To eliminate the possibility of metal migration, current density in any path cannot exceed 2×10<sup>5</sup> amps/cm². Layout rules are followed to minimize the possibility of shorts, circuit anomalies, and SCR type latch-up effects. Numerous ground-to-substrate connections are required to ensure that the entire chip is at the same ground potential, thereby precluding internal noise problems.

#### PRODUCT CHARACTERIZATION

Before a new design is released, the characterization phase must be completed so that the distribution of parameters resulting from lot-to-lot variations is well within specified limits. Such extensive characterization data also provides a basis for identifying unique application-related problems which are not part of normal data sheet guarantees. Characterization takes place from -55°C to +125°C and a +10% supply voltage.

#### **QA05**

The QA05 system collects the results of product assurance testing on all finished goods lots and feeds this data back to concerned organizations where appropriate action can be taken. The QA05 reports EPA (Estimated Process Average) and AOQ (Average Outgoing Quality) results for electrical, visual/mechanical, hermeticity, and documentation audits. Data from this system is available on request.

#### THE SURE PROGRAM

The SURE (Systematic Uniform Reliability Evaluation) program audits/monitors products from all Signetics' divisions under a variety of accelerated environmental stress conditions. This program, first introduced in 1964, has evolved to suit changing product complexities and performance requirements.

The SURE III program has two major functions: long-term accelerated stress performance audit and a short-term accelerated stress monitor. In the case of logic products, samples are selected which represent all generic product groups in all wafer fabrication and assembly locations. A series of detailed specifications (3230-009X) defines the criteria by which sample selection and evaluation testing is conducted.

#### THE LONG-TERM AUDIT

One-hundred devices from each generic family are subjected to each of the following stresses every eight weeks:

- High Temperature Operating Life: T<sub>j</sub>= 150°C, 1000 hours, static biased or dynamic operation, as appropriate (worst-case bias configuration is chosen);

- High Temperature Storage: T<sub>j</sub> = 150 °C, 1000 hours;

- Temperature-Humidity Biased Life: 85°C, 85% relative humidity, 1000 hours, static biased:

- Temperature Cycling (Air-to-Air): -65°C to +150°C, 1000 cycles.

#### THE SHORT-TERM MONITOR

Every other week a 50-piece sample from each generic family is run to 168 hours of pressure pot (15 psig, 121°C, 100% saturated steam) and 300 cycles of thermal shock (-65°C to +150°C).

In addition, each Signetics assembly plant performs SURE product monitor stresses weekly on each generic family and molded package, by pin count and frame type. Fifty pieces are run on each stress, in pressure pot to 96 hours, thermal shock to 300 cycles.

#### **SURE REPORTS**

The data from these test matrices provides a basic understanding of product capability, an estimated failure rate resulting from each stress, and an indication of major failure mechanisms. This data is compiled periodically and is available to customers upon request.

#### RELIABILITY ENGINEERING

In addition to the product performance monitors encompassed in the Logic SURE Program, Signetics' Corporate and Division Reliability Engineering departments sustain a broad range of evaluation and qualification activities.

Included in the engineering program are:

- evaluation and qualification of new or changed materials, assembly/wafer-fab processes and equipment, product designs, facilities and subcontractors;

- device or generic group failure rate studies:

- advanced environmental stress development;

- · failure mechanism characterization.

The environmental stresses utilized in the engineering programs are similar to those utilized for the SURE monitor; however, more highly accelerated conditions and extended durations typify the engineering projects. Additional stress systems such as biased pressure pot, power-temperature cycling, and cycle-biased temperature-humidity, are also included in the evaluation programs.

#### **FAILURE ANALYSIS**

The SURE Program and the Reliability Engineering Program both include failure analysis activities and are complemented by Corporate, Divisional, and Plant Failure Analysis departments. These engineering units provide a service to our customers who desire detailed failure analysis support, and they in turn provide Signetics with the technical understanding of the failure

modes and mechanisms actually experienced in service. This information is essential feedback, necessary for the continued assessment of the applicability of the stress conditions utilized to measure product performance.

#### ZERO DEFECTS PROGRAM

# Industry Requires Improved Product Quality

In recent years United States industry, and particularly those of you who buy integrated circuits, has increasingly demanded improved product quality. We at Signetics believe you have every right to expect quality products. If you buy components from a quality conscious manufacturer, the reward can be summed up in the words, lower cost of ownership.

Those of you who invest in costly test equipment and engineering to assure that

# LOGIC PRODUCT QUALITY GOALS (1984-1986)

|                           | ELECTRICAL | VISUAL/MECHANICAL | CUMULATIVE |

|---------------------------|------------|-------------------|------------|

| 1984 EPQ/AOQ Targets, PPM | 150/100    | 500/250           | 650/350    |

| 1985 EPQ/AOQ Targets, PPM | 100/50     | 300/100           | 400/150    |

| 1986 EPQ/AOQ Targets, PPM | 50/10      | 100/50            | 150/60     |

incoming products meet your specifications have a special understanding of the cost of ownership. And your cost does not end there; you are also burdened with inflated inventories, lengthened lead times, and more rework.

#### Signetics Understands Customers' Needs

Signetics has long had an organization of quality professionals inside the operating units, coordinated by a corporate quality department. This organization provides leadership, feedback, and direction for

achieving our high level of quality. Special programs are targeted on specific quality issues. For example, a program to reduce electrically defective units improved outgoing quality levels by an order of magnitude.

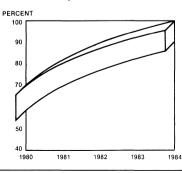

In 1980 we recognized that in order to achieve outgoing levels on the order of 100 PPM (parts per million), down from an industry practice of 10,000 PPM, we needed to supplement our traditional quality programs with one that encompassed all activities and all levels of the company. Such unprecedented low defect levels could only be achieved by contributions from all employees, from the R&D laboratory to the shipping dock. In short, a program that would effect a total cultural change within Signetics in our attitude toward quality.

This new concept is based on the 14-step quality improvement program developed by Phil Crosby and outlined in his book *Quality is Free*. The program focuses on defect prevention as the means of attaining improved quality.

#### Quality Pays Off for Our Customers

Signetics' dedicated programs in product quality improvement, supplemented by close working relationships with many of our customers, have improved outgoing product quality more than twenty-fold. Today, many major customers no longer test Signetics circuits. Incoming product moves directly from the receiving dock to the production line, greatly accelerating throughput and reducing inventories. Additional customers have pared significantly the amount of sampling done on our products. Others are beginning to adopt these cost-saving practices.

We closely monitor the electrical, visual, and mechanical quality of all our products and review each return to find and correct the cause. Since 1981, over 90% of our customers report a significant improvement in overall quality.

At Signetics, quality means more than working circuits. It means on-time delivery of the *right* quantity of the *right* product at

the agreed upon price. Our quality improvement programs extend out from the traditional areas of product conformance into the administrative areas which affect order entry, scheduling, delivery, shipping, and invoicing.

# Ongoing Quality Programs at Signetics

#### The "14-Step" Quality Improvement Program or "Do it Right the First Time"

The intent of this innovative program is to change the perception of Signetics' employees that somehow quality is solely a manufacturing issue where some level of defects is inevitable. This attitude has been replaced by one of acceptance of the fact that all errors and defects are preventable, a point of view shared by technical and administrative functions equally, and, we are sure, welcomed by our customers.

This program is company-wide and top down. It is personally led by President Charles Harwood who, with his staff, forms the corporate quality improvement team which implements corporate quality policy. Supporting the corporate quality improvement team are more than 40 quality improvement teams representing every unit in the company, each led by the unit manager.

Key components of the program are the Quality College, the "Make Certain" Program, Corrective Action Teams, and the Error Cause Removal System.

# The core concepts of doing it right the first time are embodied in the four absolutes of quality:

- 1. The definition of quality is conformance to requirements.

- 2. The system to achieve quality improvement is prevention.

- The performance standard is zero defects.

- 4. The measurement system is the cost of quality.

#### Quality College

Almost continuously in session, the Quality College is a prerequisite for all management and technical employees. The intensive two-day curriculum is built around the four "absolutes" of quality; colleges are conducted at company facilities throughout the world. More than 3000 employees have attended.

#### "Making Certain" — Administrative Quality Improvement

Signetics' experience has shown that the largest source of errors affecting product and service quality is found in paperwork and in other administrative functions. The "Make Certain" program focuses the attention of management and administrative personnel on error prevention, beginning with each employee's own actions.

This program promotes defect prevention in three ways: by educating employees as

to the impact and cost of administrative errors, by changing attitudes from accepting occasional errors to one of accepting a personal work standard of zero defects, and by providing a formal mechanism for preventing errors.

#### **Corrective Action Teams**

Employees with the perspective, knowledge, and necessary skills are formed into ad hoc groups called Correction Action Teams. These teams, the major force within the company for quality improvement, resolve administrative, technical and manufacturing problems.

#### Error Cause Removal (ECR) System

The ECR System permits our employees to report to management any impediment to doing their job right the first time. Once reported, management is obliged to respond promptly with a corrective program. Doing it right the first time in all company activities produces lower cost of ownership through product defect prevention and in all other ways meets our customers' expectations.

#### **Product Quality Program**

To reduce defects in outgoing products to nearly immeasurable levels, we created the Product Quality Program. This is managed by the Product Engineering Council, a task force composed of the top product engineering and test professionals in the company. This group:

- Sets aggressive product quality improvement goals.

- 2. Provides corporate-level visibility and focuses on problem areas.

- Serves as a corporate resource for any group requiring assistance in quality improvement.

- 4. Drives quality improvement projects.

As a result of this aggressive program, every major customer who reports back to us on product performance is reporting significant progress.

#### Standard Quality Programs

"SURE" — The acronym stands for Systematic Uniform Quality Evaluation and is an ongoing product evaluation first introduced in 1964. This activity provides our customers and us with an ongoing view of reliability performance of all generic families of Signetics' products.

**Product Monitor** — Each manufacturing facility monitors its generic product groups with short-term stress tests, pressure pot and thermal shock. These tests are performed weekly, and performance trends are

#### Performance to Schedule

Signetics' attention to administrative quality has resulted in improved performance to schedule. Doing it right the first time means on-time delivery.

#### On-Time Delivery

#### Signetics is Organized for Quality

#### Managing Cultural Change — The "14-Step" Program

Quality College

Quality Improvement Teams

"Make Certain" Program

Corrective Action Teams

Error Cause Removal System

#### Engineering Quality into the Product

SURE Program

Manufacturing Plant Product

Monitoring

Qualification Programs

Vendor Certification Programs

Product Quality Program

#### **Supporting Quality Maintenance**

Product Line

Quality and Reliability Assurance

Corporate Quality and Reliability

Failure Analysis Laboratories

Reliability Data Base

Statistical Quality Control

monitored to ensure that unwanted process deviations are spotted quickly and corrected before appearing in products received by our customers.

Qualification — Formal qualification procedures are required for all new or changed products, processes and facilities. These procedures ensure the high level of product reliability our customers expect. New facilities are qualified by the corporation and by the quality organizations of the product line that will operate the facility. After qualification, products manufactured by the new facility are subjected to highly accelerated environmental stresses to ensure that the products can meet rigorous failure rate requirements. New or changed processes are qualified similarly.

Fallure Analysis — This vital function is conducted by product line and plant fallure analysis units coordinated through the corporate fallure analysis group, a part of corporate reliability engineering. Our ten fallure analysis groups will be expanded to 16 by the end of 1984 in our ongoing effort to accelerate and improve our understanding of product fallure mechanisms.

Reliability Data Base — This computerized data base contains product reliability information collected from around the world. It is updated and published quarterly in "Signetics Product Reliability Summary."

Many customers use this information in lieu of running their own qualification tests, thereby eliminating time-consuming and costly procedures.

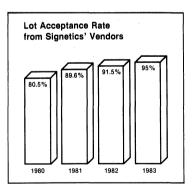

Vendor Certification Program — Our vendors are taking ownership of their own product quality by establishing improved process control and inspection systems. They subscribe to the zero defects philosophy. Progress has been excellent. Through intensive work with vendors, we have improved our lot acceptance rate on incoming materials as shown in the graph. Simultaneously, waivers of incoming material have been eliminated.

#### **Material Walvers** 1983 — 0 (Goal) 1982 — 2 1981 — 3 1980 — 134

Higher incoming quality material to us ensures higher outgoing quality products for you.

# Quality and Reliability Organization

Quality and reliability specialists at the product-line level are involved in all aspects of the product, from design through every step in the manufacturing process, and provide product assurance testing of outgoing product. A separance corporate-level group provides direction and common facilities.

#### **Quality and Reliability Functions**

- · Manufacturing quality control

- · Product assurance testing

- Laboratory facilities failure analysis, chemical, metallurgy, thin film, oxides

- Environmental stress testingQuality and reliability engineering

- Customer liaison

#### Communicating with Each Other

For information on Signetics' quality programs or for any question concerning product quality, the field representative in your area will provide you with the quickest access to answers. Or, write on your letterhead directly to the Corporate Director of Quality at the corporate address shown at the back of this data manual.

We are dedicated to preventing defects. When product problems do occur, we want to know about them so we can eliminate their causes. We are committed to zero defects. Here are some ways we can help each other:

- Provide us with one informed contact within your organization. This will establish continuity and build confidence levels.

- Periodic face-to-face exchanges of data and quality improvement ideas between your engineers and ours can help prevent problems before they occur.

- Test correlation data is very useful. Linepull information and field failure reports also help us improve product performance.

- Provide us with as much specific data on the problem as soon as possible to speed analysis and enable us to take corrective action.

- An advance sample of the devices in question can start us on the problem resolution before physical return of shipment

This teamwork with you will allow us to achieve our mutual goal of improved product quality.

# **NOTES**

# Section 3 Circuit Characteristics

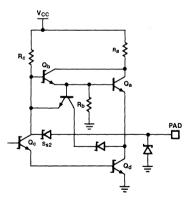

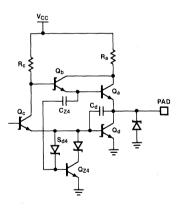

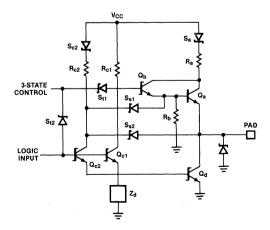

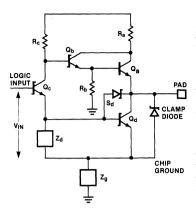

#### INPUT STRUCTURES

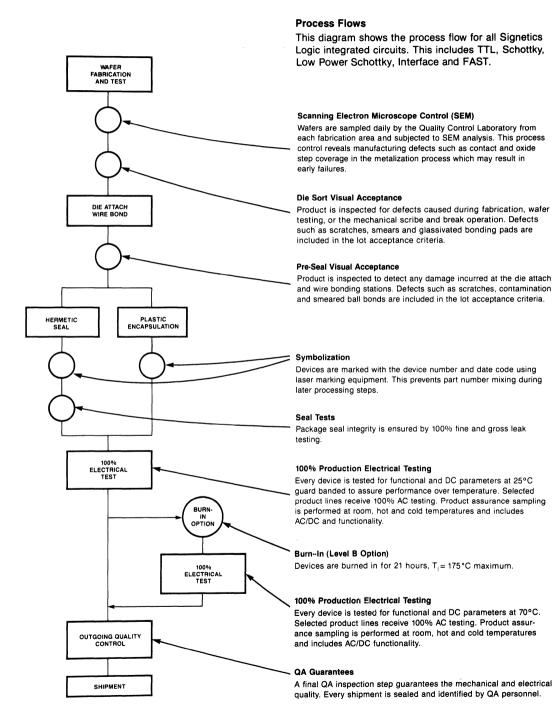

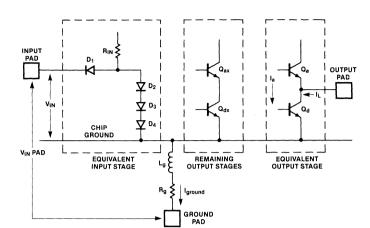

There are six types of input structures that are commonly employed in TTL families: diffusion diode, Schottky diode, multiple emiter, diode cluster, PNP, and NPN.

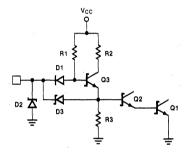

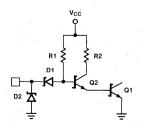

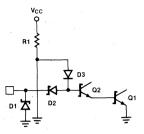

The diffusion diode input is most often used with FAST circuits. The input diode is labeled as D1 in Figure 1. There can be more than one of them if NAND logic is to be performed. In the oxide-isolated processes these are base-collector diffusions. Each input pad also has a Schottky clamp diode D2. This diode is standard for most TTL circuits, and is included to limit negative input voltage excursions that are generally the result of inductive undershoot.

Figure 1. Diode Input

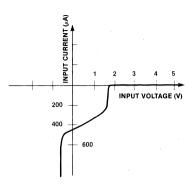

The static diode input function of voltage versus current is shown in Figure 2. If the pad voltage is negative, most of the relatively high, negative current flows through the clamp Schottky D2. At zero volts the current flows from V<sub>CC</sub> through R1 and D1 to the pad. Switching from a logic LOW level to a logic HIGH level occurs when the input pad voltage rises high enough to force the current from the D1 path to the Q3-Q2-Q1 path. This happens when the base voltage of transistor Q3 is at three base-emitter drops (3VRF), and the pad is at 2V<sub>BF</sub>, which is the standard FAST threshold switching voltage. At this voltage the input current is very small, just the leakage currents of diodes D1, D3 and clamp diode D2. The current remains at this small, positive value until breakdown voltage is reached.

Transistor Q3 and resistor R2 provide a current gain by increasing the amount of current available to Q2 and Q1 when the pad voltage is high. R3 bleeds current off the base of Q2 to pull it low when the pad voltage is low. D3 speeds up this process during the HIGH-to-LOW pad transition. When the switching transients are over, D3 is reverse biased.

Figure 2. Static Diode Input Function of Voltage vs Current

The current of Figure 2 is scaled for the case where the pad is required to pull down a single 10K-ohm resistor R1 (20µA maximum in the HIGH state and 0.6mA maximum in the LOW state), which is defined as a standard FAST Unit Load (UL). For some parts, pad current can exceed a UL, especially in the logic LOW state. This will happen if the pad must sink the current from more than one R1 resistor or if the value of R1 is less than 10K ohms, which will be the case if the capacitance at the base of the transistor Q3 is too large for the required switching speed. In this event, the actual number of ULs is listed for each input in the specification sheet for the part. Note that a UL as defined here is less than the normally defined Schottky TTL Unit Load; the correlation is one Schottky Unit Load = 1.67 ULs. This is an important point to remember for fan-in and fan-out calculations in systems that mix FAST with other TTL families.

The Schottky diode input is shown in Figure 3. Its function is much the same as the diffusion diode input, except that the switching threshold voltage is lower by the Schottky diode forward drop, about 500mV. Because a higher threshold voltage is usually advantageous from a noise-margin standpoint in high-speed systems, the Schottky diode input is not used with FAST.

Figure 3. Schottky Diode Input

The multiple-emitter input is shown in Figure 4. Its function is also much the same as the diffusion diode input, but with the base-emitter junction used instead of the base-emitter junction. In some respects this would be a better choice for high-speed logic, but it has one serious disadvantage which is the emitter-base breakdown voltage that may be as low as 5 volts. This low breakdown allows a high input current to flow through the Q2–Q1 base-emitter path which cannot be limited to an acceptable value with a series resistor.

Figure 4. Multiple-Emitter input

The diode cluster input (Figure 5) looks like a multiple-emitter input, except that its breakdown voltage is higher because separate Schottky junctions are used instead of a transistor. It has limited use in FAST circuits.

Figure 5. Diode Cluster Input

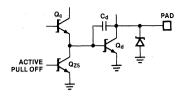

The PNP input in various forms has found wide acceptance in low power Schottky logic because it provides a desirable high-impedance input. Unfortunately, it is not well-suited for FAST circuits using the presently available processes because of problems associated with the vertical PNP device. A typical TTL usage is shown in Figure 6.

Figure 6. PNP Input

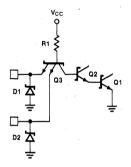

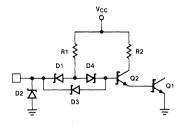

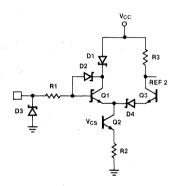

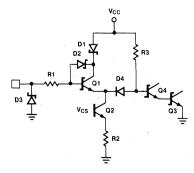

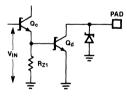

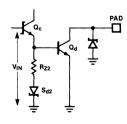

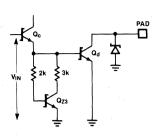

The NPN input is shown with two variations in Figures 7a and 7b. It has limited use in standard TTL circuits, and is used in selected FAST devices, especially where its superior high-impedance input characteristics are useful. A typical plot of static input current versus input voltage is shown in Figure 8. There are some significant differences between this function and that of the diffusion diode input shown in Figure 2, the most important being the much lower input current in the region from zero volts to threshold, and the controlled increase of input current above V<sub>CC</sub>.

Figure 7a. NPN Input

Figure 7b. NPN Input

When the pad voltage is negative, the large negative clamp current is supplied through the clamp Schottky diode D3. For positive voltages, from zero volts to the switching threshold of 2V<sub>RE</sub>, Q1 is off, and the input current III is very small, just the leakage current of Q1, D2, and D3 with low reverse bias. As the input voltage rises above 2V<sub>RF</sub>, Q1 turns on and the current that had been flowing through D4 now flows through Q1, and blocking Schottky diode D1 to V<sub>CC</sub>. The value of this current is determined by the current source transistor Q2 with its base connected to voltage reference V<sub>CS</sub>, and by the size of the emitter resistor R2. The current is nearly constant within the normal operating range of input voltages, and has a typical value of 0.1mA to 1.0mA. The pad must supply only a small fraction of this bias current, the ratio of Q1 collector current to base current being the bipolar BETA factor. Typically, I<sub>IH</sub> base input current is less than 20µA in the voltage range from zero volts to V<sub>CC</sub>. This value is the specification for a standard FAST NPN Unit Load. As in the diode input case, if larger currents are needed to reduce delay times or to provide for multiple-input transistors connected to the same pad, the specification sheet for the particular device will identify the input pads which have NPN ULs larger than one, and will list their values.

Figure 8. NPN Input Characteristics (not to scale)

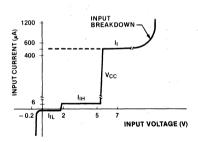

In normal operation, the negative input voltage is limited by clamp Schottky D3 and the positive input voltage is less than  $V_{CC}.$  The actual input voltage may exceed  $V_{CC}$  for three reasons: there will be inductive overshoot in badly terminated systems; the  $V_{CC}$  pad may be floating or grounded; or the input pad may be forced high by electrostatic discharge or incoming inspection testing.

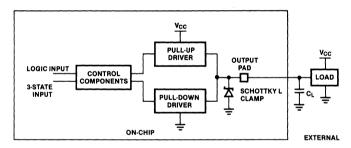

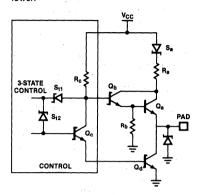

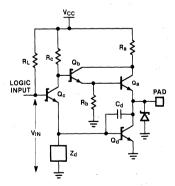

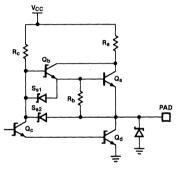

For the inductive overshoot case, when the pad voltage exceeds  $V_{\rm CC}$ , part of the Q1 collector current begins to flow from the pad through limiting resistor R1 and Schottky diode D2. The current from  $V_{\rm CC}$  through D1