ES 1800 Satellite Emulator Reference Manual For 68000 Family Microprocessors

# ES 1800 Satellite Emulator Reference Manual For 68000 Family Microprocessors

P/N 920-00069-04 August 1988 Copyright © 1987 Applied Microsystems Corporation. All rights reserved.

# **Table of Contents**

| Page                           |

|--------------------------------|

| PREFACE                        |

| Unpacking and Inspectionii     |

| Warningiii                     |

| Serviceiv                      |

| Limited Hardware Warranty v    |

| Hardware Extended Warranty vi  |

| Hardware Service Agreements vi |

| SECTION 1: INTRODUCTION        |

| How to Use This Manual1-2      |

| System Setup                   |

| System Operation               |

| SECTION 2: GETTING STARTED     |

| Introduction2-1                |

| Emulator Set-up. 2-1           |

| Target System Set-up2-4        |

| Power-On Sequence              |

| Test Run of System             |

| SECTION 3: HARDWARE            |

| Emulator Chassis Assembly 3-1  |

| Emulator Control Boards        |

| Emulator Chassis Rear Panel    |

## Table of Contents (cont)

|                                      | Page  |

|--------------------------------------|-------|

| Pod Assembly                         | 3-8   |

| Null Target Software Simulation Tool | 3-10  |

| Logic State Analyzer (LSA) Assembly  | 3-11  |

| Serial Ports                         | 3-12  |

| Maintenance                          | 3-16  |

| Troubleshooting                      | 3-21  |

| ES1800 Emulator Specifications       | 3-23  |

| SECTION 4: ES LANGUAGE               |       |

| Structure of the ES Language         | 4-1   |

| Notes on ESL                         | 4-6   |

| Help                                 | 4-20  |

| Log In Banner                        | 4-25  |

| Prompts                              | 4-27  |

| Special Modes                        | 4-28  |

| Special Characters                   | 4-31  |

| Errors                               | 4-32  |

| ES Language Error Messages           | 4-33  |

| SECTION 5: SYSTEM COMMANDS           |       |

| Set-Up Commands                      | 5-1   |

| Serial Communications                | 5-29  |

| Overlay Memory                       | 5-53  |

| Registers                            | 5-68  |

| Trace Memory                         | 5-92  |

| Emulation                            | 5-93  |

| Macros                               | 5-117 |

| The Repeat Operators                 | 5-122 |

| Symbols                              | 5-126 |

| Miscellaneous Commands.              | 5-134 |

|                                           | Page |

|-------------------------------------------|------|

| SECTION 6: TARGET COMMANDS                |      |

| Introduction                              | 6-1  |

| Emulation.                                |      |

| Memory Commands                           |      |

| Line Assembler                            |      |

| Memory Mode                               |      |

| Diagnostic Functions                      |      |

| SECTION 7: 68000/08/10 EVENT MONITOR SYST | EM   |

| Overview                                  |      |

| Defining Events                           | 7-9  |

| Defining Action Lists                     | 7-10 |

| Breaking Emulation                        | 7-15 |

| Tracing Events                            | 7-17 |

| Counting Events                           | 7-20 |

| Trigger Signal                            | 7-24 |

| Special Interrupts                        | 7-25 |

| Changing Event Groups                     | 7-27 |

| SECTION 8: 68020 EVENT MONITOR SYSTEM     |      |

| Overview                                  | 8-1  |

| Defining Events                           | 8-5  |

| Defining Action Lists                     | 8-6  |

| Breaking Emulation                        | 8-11 |

| Tracing Events                            | 8-12 |

| Tracing and Breaking with the 68020       | 8-14 |

| Trace Mode 0                              | 8-19 |

| Trace Mode 1                              | 8-27 |

| Trace Mode 2                              | 8-36 |

## Table of Contents (cont)

|                                       | Page |

|---------------------------------------|------|

| Trace Mode 3                          | 8-45 |

| Counting Events                       | 8-55 |

| Trigger Signal                        |      |

| Special Interrupts                    | 8-60 |

| Changing Event Groups                 | 8-62 |

| Shortcuts for Setting Up              | 8-64 |

| APPENDIX A: ES LANGUAGE MNEMONICS     |      |

| ES Language Commands                  | A 1  |

| L3 Language Commanus                  | A-1  |

| APPENDIX B: ERROR MESSAGES            |      |

| Error Messages                        | B-1  |

| Data Strobe Messages                  | B-4  |

| APPENDIX C: SERIAL DATA FORMATS       |      |

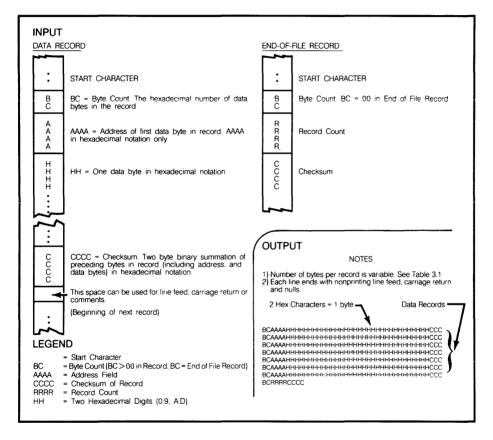

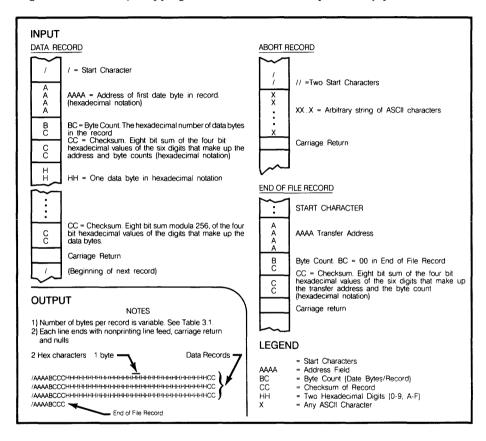

| MOS Technology Format                 | C-2  |

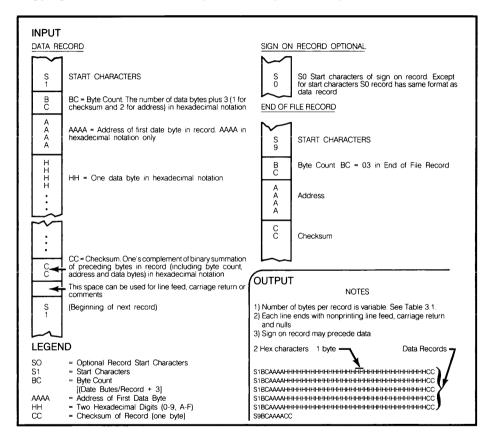

| Motorola Exorcisor Format             | C-3  |

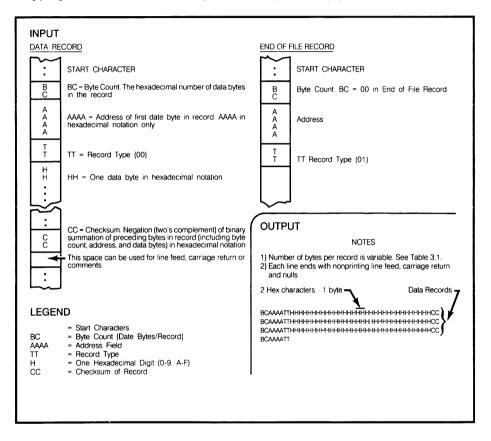

| Intel Intellec Format                 | C-4  |

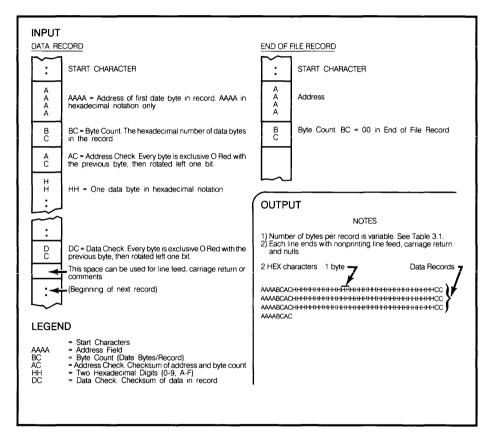

| Signetics/Absolute Object File Format | C-5  |

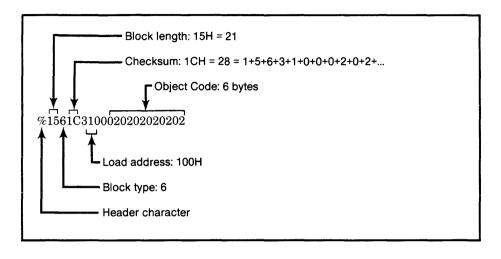

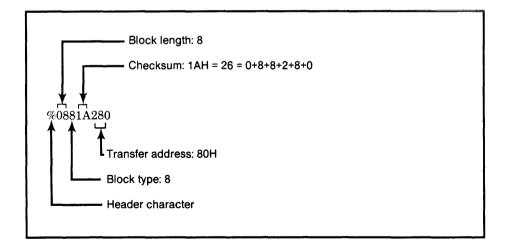

| Tektronix Hexadecimal Format          |      |

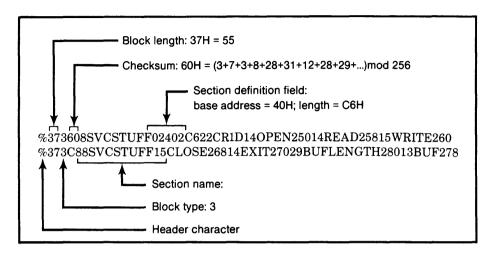

| Extended Tekhex Format                | C-7  |

| Motorola S-Record Format              | C-15 |

### **Table of Contents**

# Preface

|                             | Page |

|-----------------------------|------|

| UNPACKING AND INSPECTION    | ii   |

| Standard Equipment          |      |

| Optional Equipment          | ii   |

| WARNING.                    | iii  |

| SERVICE                     | iv   |

| LIMITED HARDWARE WARRANTY   | v    |

| HARDWARE EXTENDED WARRANTY  | vi   |

| HARDWARE SERVICE AGREEMENTS | vi   |

### **PREFACE**

APPLIED MICROSYSTEMS CORPORATION is proud of its role in the systems development industry and conscious of its important contribution. However, it assumes no liability for errors or for any damages from use of this manual or the equipment it accompanies.

We have made every effort to document this product accurately and completely. We reserve the right to make changes to this manual without notice.

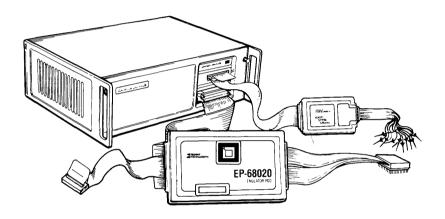

The ES1800 Emulator is intended for use in developing, debugging, and testing Motorola 68000/68008/68010/68020 microprocessor-based systems. This manual assumes that the user is familiar with the terminology and capabilities of the Motorola series microprocessor.

## **Unpacking and Inspection**

Your Emulator has been inspected and tested for electrical and mechanical defects before shipping, then configured for the line voltage requested. Although the Emulator was carefully packed, check it for possible transit damage and verify that the following units are present. If you find any damage, file a claim with the carrier and notify Applied Microsystems Corporation (Customer Service 1-800-426-3925).

#### STANDARD EQUIPMENT

- Emulator chassis with power cord

- Main control boards and pod assembly

- ES1800 Emulator Reference Manual for 68000 Series Microprocessors

### **OPTIONAL EQUIPMENT**

- Control Boards

- overlay memory

- symbolic debug

- Logic state analysis pod assembly

- Carrying case

## Warning

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It is temporarily permitted by regulation and has not been tested for compliance with the limits of Class A computing devices pursuant to Subpart J of Part 156 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference. It is up to the user, at his own expense, to take whatever measures may be required to correct the interference.

### **Service**

If the ES1800 unit needs to be returned for repairs, Applied Microsystems Customer Service will issue a return authorization number. To obtain the necessary return authorization number and shipping information, call 1-800-426-3925, and ask for Customer Service. After the expiration of the warranty period, service and repairs are billed at standard hourly rates, plus shipping to and from your premises.

## **Limited Hardware Warranty**

Applied Microsystems Corporation warrants that all Applied Microsystems manufactured products are free from defects in materials and workmanship from date of shipment for a period of one (1) year, with the exception of mechanical parts (such as probe tips, cables, pin adapters, test clips, leadless chip sockets, and pin grid array adapters), which are warranted for a period of 90 days. If any such product proves defective during the warranty period, Applied Microsystems Corporation, at its option, will either repair or replace the defective product. This warranty applies to the original owner only and is not transferable.

To obtain warranty service, the customer must notify Applied Microsystems Corporation of any defect prior to the warranty expiration and make arrangements for repair and prepaid shipment to Applied Microsystems Corporation. Applied Microsystems Corporation will prepay the return shipping to US locations. For international shipments, the customer is responsible for all shipping charges, duties, and taxes. Prior to returning any unit to Applied Microsystems Corporation for warranty repair, a return authorization number must be obtained from Applied Microsystems Corporation's Customer Service Department (see Service section on the previous page).

This warranty shall not apply to any defect, failure, or damage caused by improper use, improper maintenance, unauthorized repair, modification, or integration of the product.

## **Hardware Extended Warranty**

Applied Microsystems Corporation's optional EXTENDED WARRANTY is available for all hardware products for an additional charge at the time of the original purchase. The EXTENDED WARRANTY may be purchased to extend the warranty period on mechanical parts normally restricted to 90 days to a total of one (1) or two (2) years and to extend the warranty on electrical parts and all other mechanical parts to two (2) years.

## **Hardware Service Agreements**

SERVICE AGREEMENTS are available for purchase at any time for qualified Applied Microsystems Corporation manufactured products. The SERVICE AGREEMENT covers the repair of electrical and mechanical parts for defects in materials and workmanship. For information, contact your local sales office.

## **SECTION 1**

## **Table of Contents**

# Introduction

| Page                                |

|-------------------------------------|

| HOW TO USE THIS MANUAL1-2           |

| SYSTEM SETUP. 1-4                   |

| SYSTEM OPERATION1-7                 |

| Overview1-7                         |

| ES Language1-7                      |

| Real time1-8                        |

| Trace Memory                        |

| Overlay Memory1-9                   |

| Event Monitor System1-9             |

| Optional Symbolic Debugger1-10      |

| Optional Logic State Analyzer (LSA) |

| Diagnostic Functions. 1-11          |

### INTRODUCTION

The ES1800 Emulation system allows you to analyze and control a target environment, consisting of hardware or software, in real time. To use the ES1800 with your target hardware, simply remove the target system's microprocessor and plug in the ES1800 Emulator. Your system uses the Emulator in place of the microprocessor and behaves as if the target microprocessor is present. The Emulator continues to run until you manually stop it or it encounters a user defined stop condition. This predefined condition can be in the form of single-step operation statements or more complex event monitoring (WHEN/THEN) statements.

During the debugging or integration process you can read and write to the microprocessor registers or memory locations and execute programs contained in the target system memory. The ES1800 Emulator also allows you to debug software without being physically connected to the target system. In this configuration, the Emulator uses a null target combined with overlay memory capabilities.

Information in this manual applies to Motorola 68000/68008/68010/68020 microprocessors only. For more complete information on your particular chip, refer to the reference manuals: 16 Bit Microprocessors Users Manual (for the 68000/08/10 microprocessors) or the MC68020 32 Bit Microprocessors Users Manual (for the 68020 microprocessor) published by Motorola Corporation.

### How to Use This Manual

This manual is your guide to using the Applied Microsystems Corporation's ES1800 Emulator for Motorola 68000/08/10/20 microprocessors. For your first time using the ES1800, read through the Introduction and Getting Started sections and refer to the Hardware section to make sure your hardware is set up correctly.

Once you are familiar with the Emulator, the sections on the ES language, system commands and target commands provide information on all of the available commands. The comprehensive Index and Appendix A: ES Language Mnemonics are useful for finding specific information in the manual.

The manual is organized as follows:

Section 1: Introduction introduces Applied Microsystems Corporation's ES1800 Emulator for the 68000/08/10/20 microprocessors. It explains emulation, set-up, and configuration requirements, and provides an overview of the features of the ES1800.

Section 2: Getting Started provides a checklist for setting up your Emulator and target system, starting and testing the Emulator, and storing customized system variables in EEPROM.

Section 3: Hardware contains all the information on the Emulator, the control boards, the rear panel, the pod, and the serial ports, as well as information on maintenance and troubleshooting.

Section 4: ES Language explains the structure of the language that controls the Emulator, with clear explanations of the help menus, prompts, special modes and characters, and language-related error messages.

Section 5: System Commands provides a reference to commands that control the Emulator system. It is divided into sections on setup, serial communications, download operations, registers, trace memory, macros, and symbols.

Section 6: Target Commands is a reference to commands that directly control the target system. It is divided into sections on running the target program, memory commands, the line assembler, the memory disassembler, memory mode, and diagnostics.

Section 7: 68000/08/10 Event Monitor System explains the powerful breakpoint and control system, including the structure of the system, breaking emulation, counting events, using special interrupts, and tracing events. (This chapter pertains to the 68000, 68008, and 68010 microprocessors.)

Section 8: 68020 Event Monitor System explains the powerful breakpoint and control system, including the structure of the system, breaking emulation, counting events, using special interrupts, and tracing events. The different trace modes that pertain only to the 68020 microprocessor are covered, as well as setup shortcuts.

The Appendices are a quick reference to ES Language mnemonics, explanations of the hardware error messages and serial data formats.

## System Setup

The ES1800 can debug and integrate software and hardware. Setups for each system may be different. In every combination, there is a target system, which can be hardware, software alone (if you are using the Emulator's overlay memory to debug software), or a combination of the two. The target system is the environment you intend to emulate.

The ES1800 Emulator consists of a chassis assembly which houses the control boards and an emulator pod which houses the emulating microprocessor. The Emulator can be controlled with a dumb terminal, which can be your development system CRT or another device set to function in dumb terminal mode. You can enhance this basic system by adding the optional Logic State Analyzer (LSA) pod. This provides 16 additional input lines giving access to signals other than the normal address, data, and control signals of the microprocessor. You may also add an optional overlay memory board. Overlay memory can be mapped anywhere in the address space of the target system. The overlay memory board provides additional capabilities including the ability to debug software with or without a target system.

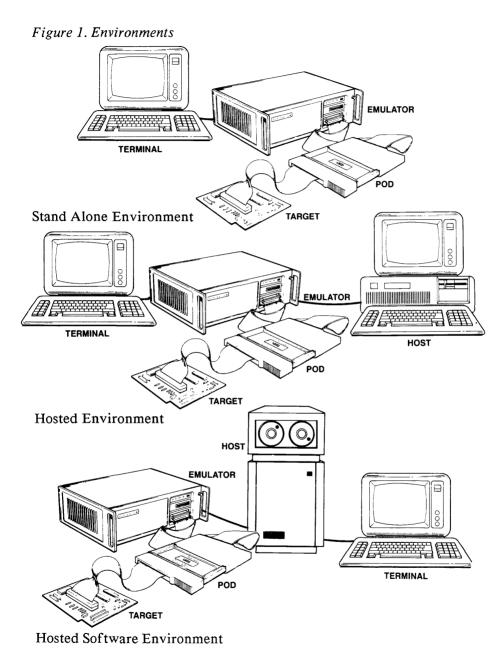

The stand alone environment (refer to diagram on page 1-6) consists of the Emulator and a dumb terminal or equivalent connected to the terminal port. This setup can debug target systems with software already installed, or short hand-entered routines. The stand alone configuration is common in manufacturing test and service facilities.

The Emulator can also use data stored in a host development system by setting up a hosted environment (refer to diagram on page 1-6). The Emulator is still under the direct control of the CRT but can load data from the host system's data files.

By attaching a printer, data and code from your target system can be printed out in machine or assembly language. You can also print all Emulator commands and their results. The Emulator system has two serial ports and uses standard RS232C serial port protocol. Each port can be independently configured for baud rate, data length, and number of stop bits.

Software for driving the Emulator is available from Applied Microsystems Corporation for the IBM PC and compatibles, SUN, APOLLO and VAX.

The Emulator can also be totally controlled by your host system. This hosted software environment (refer to diagram on page 1-6) requires special host resident software. Drivers and High Level Debuggers are available from Applied Microsystems for most languages and host systems.

1-6

## System Operation

#### OVERVIEW

The ES1800 has two basic operational modes: run mode and pause mode. Pause mode is used to set up the system configuration and to display information after leaving emulation. System setup is accomplished from two menus. The first menu contains all external communication variables; the second contains the control switches for emulation and serial port data output. Both setups can be saved to EEPROM and automatically loaded at power-up.

Run mode or emulation means that the microprocessor in the Emulator pod is running a program in the target system, allowing you to see what is happening within the target system. Emulation stops when (1) you stop it, (2) user-defined breakpoints are enabled and occur, (3) you reset the system, or (4) errors occur in the target system.

When you manually stop emulation or a breakpoint is reached, you enter pause mode. All registers and addresses are then available for examination, along with a trace history of performance of the microprocessor. A command language allows you to enter emulation in the desired state and leave emulation when a specific combination of events is detected in the target.

#### ES LANGUAGE

The ES1800 uses its own command language. To take advantage of the sophisticated operations of the Emulator, you must understand the general concepts of this language. The Emulator operates in response to command statements composed of command menmonics and, for some commands, arguments. An argument to a command is an additional value entered as part of the command sequence, such as an address range or base value. Arguments can consist of single values, expressions, or lists.

The command statements form a control language, similar to higher-level computer languages. Like a computer language, the operators and values can be combined to form complex expressions. Statements have a maximum length of 76 characters and can be extended by the use of macros.

The ES Language contains registers, counters, and conditional statements allowing the user full control over the operation of the target system. To complete the language, a full set of error messages is provided for (1) target hardware, (2) Emulator hardware, (3) target software, and (4) ES Command Language syntax.

#### **REAL TIME**

Since the pod processor is identical to your target microprocessor, the target system runs in real time. No wait states are inserted by the Emulator during run mode. Additionally, the Emulator's internal clock provides a completely self-contained microprocessing environment that allows you to execute your software without connecting the Emulator to your target system, using the null target.

#### TRACE MEMORY

Trace memory functions as a history of your target system program's execution. This memory can record 2046 bus cycles and display these in machine or assembly language. All address lines, data lines, processor status lines, and 16 bits of external logic input are traced. If something unexpected happens during program execution, trace memory can be reviewed to determine the sequence of commands executed prior to the unexpected event. When used in conjunction with the trace disassembler, hardware and software problems can be quickly tracked down.

If you have the Dynamic Trace feature, you can view trace without stopping emulation. Without the Dynamic Trace feature, you can stop the program to read trace with either an asynchronous stop or by using the Event Monitor System to stop at the exact program state you are interested in.

#### **OVERLAY MEMORY**

Overlay memory is Emulator working memory, which can be used in a variety of ways. When debugging software without target hardware, the target program is loaded into overlay memory where it can be edited and positioned in the target system address space as desired. The program executes in real time as if it resided totally in the target system. Overlay memory is also useful when target hardware is connected, for loading portions of software, making patches, and checking programs not yet committed to PROM.

The overlay memory is RAM with appropriate address and control logic, ranging in size from 32K to 2M bytes and locatable in 2K-byte segments throughout the system. Each segment can be assigned one of four attributes: target, read/write, read-only, or illegal. Unmapped memory is assigned the target attribute by default. Overlay memory mapped as read-only can always be modified by the Emulator. However, if a target program tries to write to read-only overlay, emulation stops and an error message is displayed.

When a segment of memory is mapped, program accesses to that memory range are directed to the overlay instead of the target. Overlay memory accesses occur in real time, with no wait states added by the Emulator.

#### EVENT MONITOR SYSTEM

The ES1800's Event Monitor System provides unprecedented breakpoint and system control, enabling the user to isolate and break on any predefined series of events and then perform actions defined by WHEN/THEN conditional statements. The user controls and monitors the target with the Event Monitor System by defining statements that specify single or multiple events through logical combinations of address, data, status, pass counter, and optional logic field states. When those events are encountered in the target system program, the ES1800 can break emulation, trace specific sequences, count events, and trigger outputs, all independently, allowing the user to analyze the cause-effect relationship established by the event/action sequences defined.

The Event Monitor System uses four groups, each containing eight registers, to let the user monitor a complex series of events through multiple actions and combinations of comparator registers. The system uses one group at a time, with each WHEN/THEN statement active in a specific group. WHEN/THEN statements can switch to different groups and access conditional statements and registers for that group. The user can control the tracing of 2046 machine cycles, selecting the desired instructions to be recorded in the trace memory.

#### OPTIONAL SYMBOLIC DEBUGGER

The symbolic debug option allows you to assign frequently used values to symbol names that are easily remembered. Features include:

- Reference to an address by a name instead of a value

- Display of all symbols and sections with their values

- Editing (entry and deletion) of symbols and their values

- Automatic display of symbolic addresses during disassembly

- Section (module) symbols that can be used as range arguments and for section offsets in trace disassembly

- Upload and download of symbol and section definitions using standard serial formats

Because symbols are a powerful extension of the Emulator, they are frequently used in examples throughout Section 5, System Commands. Please note that if you have not yet purchased the symbolic debug option, you may need to modify these examples.

## OPTIONAL LOGIC STATE ANALYZER (LSA)

LSA inputs can qualify event specifications in the Event Monitor System. In the simplest form, specific bit patterns at the LSA inputs can cause a breakpoint. The LSA comparator can detect complex event specifications as well. The LSA provides an additional means of monitoring information from other parts of the target system, beyond the normal recording of trace data performed by the Emulator. This is useful when monitoring (1) buffers suspected of failure, (2) decode logic, (3) memory management circuit translations, and (4) asynchronous external events.

#### DIAGNOSTIC FUNCTIONS

Diagnostics available in the ES1800 Emulator include both RAM/ROM tests and scope loops. RAM test routines verify that RAM is operating properly. They can be run on the target RAM or Emulator overlay memory and may be executed in either byte or word mode. ROM tests include a built-in CRC algorithm.

High speed memory scope loops for troubleshooting with an oscilloscope are built into the Emulator firmware. They can be used for locating stuck address data, status or control lines, and generating signatures using signature analysis equipment.

The firmware that generates the scope loops is optimized for maximum speed of execution. This short cycle time allows the hardware engineer to review the timing of pertinent signals in the target system without using a storage oscilloscope. The scope loops can be executed in either byte, word, or long word mode.

## **SECTION 2**

## **Table of Contents**

# **Getting Started**

|                             | Page |

|-----------------------------|------|

| INTRODUCTION                | 2-1  |

| EMULATOR SET-UP             | 2-1  |

| TARGET SYSTEM SET-UP        | 2-4  |

| POWER-ON SEQUENCE           | 2-5  |

| Target System Present       | 2-5  |

| No Target System            | 2-5  |

| TEST RUN OF SYSTEM          | 2-6  |

| 1. Initialize The Emulator  | 2-6  |

| 2. Map Ram Memory           | 2-7  |

| 3. Test RAM                 | 2-7  |

| 4. Enter Program            | 2-8  |

| 5. Verify The Program       | 2-8  |

| 6. Run The Emulator         | 2-9  |

| 7. Stop The Program         | 2-9  |

| 8. Display The Trace Buffer |      |

| Q Set A Breakpoint          | 2 10 |

### **GETTING STARTED**

### Introduction

This section provides a checklist for setting up your Emulator and target system, starting and testing the Emulator, and storing customized system variables in EEPROM.

## Emulator Set-up

- 1. Refer to page 3-1 and verify that proper grounding and power requirements have been met.

- 2. Remove the front cover of the Emulator by turning the thumbscrews counterclockwise. The pod and LSA pod may need to be unplugged in order to do this.

- Verify that the main control board and the memory control board are in the top two slots of the Emulator chassis.

- 4. Verify that the trace/break board is in the third bus slot of the Emulator chassis.

- 5. If you are using overlay memory, verify that the overlay memory master, and/or master and slave boards, if needed, are inserted.

- 6. Verify that the correct Emulator board for your target microprocessor is in the bottom slot. (See page 3-4 for board positions.)

- 7. Verify that all boards are firmly seated in their mother-board connectors.

- 8. Set the thumbwheel switch on the main control board for your particular system variables (see page 3-5).

System default variables in switch position 0 are:

- 9600 baud 8-bit word length

One stop bit No parity

Full duplex No echo

Terminal control XON and XOFF are recognized

8th data bit set to 0 or a space

- 9. Verify that the three-position toggle switch on the memory control board is in the center position. (See page 3-4).

NOTE: If you are using an early ES1800 model, the above comment may not apply. Follow the instructions provided at the time of purchase.

- 10. Replace front panel and attach the correct pod assembly (see page 3-8). A pod assembly must be connected to the Emulator even if you are not using target hardware.

- 11. OPTIONAL: Connect Logic State Analyzer pod (see page 3-11).

- 12. Verify that the RS232C cable connections are correct for the system configuration you plan to use (see page 3-12, Pin Configurations).

- 13. Verify that the RS232C baud rates and data requirements are set the same on both the Emulator and the terminal (see pages 3-5).

NOTE: the 68020 microprocessor requires different pod connections depending on the trace memory mode you are intending to use (refer to page 3-8)

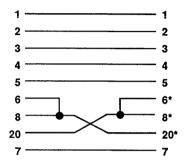

14. If using communications without a modem, you may need a null modem cable. If you purchase a null modem cable, it is likely to have the following configuration.

Check the specifications in your terminal manual before reversing the pins.

- \*Note that pins 6, 8, and 20 are not used and are unaffected by the cable configuration.

- 15. If you plan to use dynamic RAM, read the pages on the ON-OFF switches CAS and TAD. CAS controls whether the address strobe is active in pause mode (page 5-13), and TAD controls whether the emulator address bus is tri-stated during pause mode (page 5-24).

## Target System Set-up

- 1. Check that the target has a 48 pin package dual in-line socket for the 68008 chip, a 64 pin package for the 68000/68010 chips, and a 114 pin grid array for the 68020 chip.

- 2. Check that a good ground exists at the microprocessor socket using an ohmmeter.

- 3. Validate the power supply at the microprocessor socket. It should read  $5V \pm 10\%$ .

- Check for a valid clock signal at the target microprocessor socket.

- 5. Turn off target system power and Emulator power.

- 6. Plug in the probe tip (see page 3-8).

## Power-On Sequence

#### TARGET SYSTEM PRESENT

- 1. Turn on the target system.

- 2. Turn on the Emulator.

- 3. Reset the target system (see page 6-14).

#### NO TARGET SYSTEM

- 1. Verify that the pod is connected to the Emulator (see page 3-8).

- 2. Remove the conductive rubber probe tip protection and install Null Target Software Simulation Tool (see page 3-10).

- 3. Power-up the Emulator.

- 4. The log-in banner is displayed (see page 4-25).

When you power-up the Emulator, all registers, maps, event clauses, and system variables are either cleared or set to default values. Examine the SET and ON menus (see pages 5-3 and 5-9) and configure the system as desired. Your special setup can then be stored in EEPROM (see page 5-25). By setting the rotary switch on the controller board to the proper position, your special setup can be autoloaded on power-up.

The ES1800 Emulator system is now running and ready to accept ES Language commands.

## **Test Run of System**

Use this test guide after the system configuration is correct and the ES prompt is displayed ( $\geq$ ).

A system test run consists of the following 9 steps:

- 1. Initialize Emulator

- 2. Map overlay memory

- 3. Test RAM

- 4. Enter a program

- 5. Verify a program

- 6. Run the Emulator

- 7. Stop the program

- 8. Display the trace buffer

- 9. Set a breakpoint

This test requires that an optional overlay memory board is installed. This demonstration does not need a target system.

If you encounter difficulty with the ES1800 hardware, call the Applied Microsystems Corporation Customer Service hot line at 1-800-426-3925 for assistance.

#### 1. INITIALIZE THE EMULATOR

Enter the following to initialize the Emulator:

>SET 1,0; SAV; SET 1,1; SAV; SET 1,0

#### 2. MAP RAM MEMORY

Map all of the overlay memory available to the Emulator.

```

>MAP 0 TO XXXX

```

(Where XXXX is the ending address (in hex) of the amount of overlay memory installed.) The following table provides a quick reference for hex values corresponding to overlay memory sizes.

| Hex value | Overlay memory |  |

|-----------|----------------|--|

| 7FFF      | 32K            |  |

| OFFFF     | 64K            |  |

| 1FFFF     | 128K           |  |

| 3FFFF     | 256K           |  |

| 7FFFF     | 512K           |  |

For example, to map 64K, enter:

```

>MAP 0 to OFFFF

```

For more information, refer to page 5-55.

#### 3. TEST RAM

Test all overlay memory installed by entering:

```

>SF 1,0 TO XXXX

```

(Where XXXX is the ending address (in hex) of the amount of overlay memory installed.) If there is a failure, repeat mapping and testing.

If RAM test continues to fail, reseat all PAL and RAM chips on the overlay memory.

For more information, refer to Diagnostic Functions, page 6-49.

#### 4. ENTER PROGRAM

Enter a short program by invoking the line assembler and entering 68000 op codes (see page 6-34).

```

>ASM 400

**** 680XX LINE ASSEMBLER ****

000400>NOP

000402>/

000404>/

000406>/

000408>/

00040A>BRA $400

00040C>X

```

NOP is a null operation. Each time you type the slash ( ), you repeat the previous command. You have entered the equivalent of five lines of NOPs. The x at the end exits the assembler.

#### 5. VERIFY THE PROGRAM

Single step through the program, to verify that it works, by entering:

```

>PC = 400

>STP; DT

>/

>/

>/

>/

>/

>/

>/

```

The disassembled trace should show that NOPs were executed and that the branch was taken correctly.

For more information on the STP command, refer to page 6-8.

#### 6. RUN THE EMULATOR

Enter RUN.

>RUN R>

The prompt should be displayed with no error messages. This indicates the Emulator is running in real time, executing the program.

#### 7. STOP THE PROGRAM

Enter STP to stop.

R>STP

The Emulator should stop running and display the PC register value.

#### 8. DISPLAY THE TRACE BUFFER

Enter **DRT** to display the execution history of the program.

>DRT

The display should show sequence numbers between 0 and 20, and address values between 400 and 40E. Then enter **DTB**.

>DTB

The display should show a disassembled trace of the program with NOPs and BRA \$000400.

#### 9. SET A BREAKPOINT

Set a breakpoint to verify that the Event Monitor System will halt execution when a defined condition is met. In this case, the Emulator executes 100 (hex) bus cycles, then breaks.

#### Enter:

```

>WHEN DC1 THEN CNT

>WHEN CL THEN BRK

>DC1=0XXXX

>CL=100

>RBK

R>

```

This causes the counter to be incremented each time data comparator 1 sees a data bus value between 00000 and 0FFFF. When the count limit of 100 is reached, emulation will break.

If a break does not occur:

- 1. Enter STP.

- Set PC to 400.

- Enter DES 1 and verify that you have entered the WHEN/THEN statement and comparator values as shown above.

- 4. Type **RBK** again.

If no break occurs, call Applied Microsystems Customer Service at 1-800-426-3925 for assistance.

## **SECTION 3**

### **Table of Contents**

## **Hardware**

| <u>Pa</u>                              | ge  |

|----------------------------------------|-----|

| EMULATOR CHASSIS ASSEMBLY              | -1  |

| System Grounds                         | -1  |

| EMULATOR CONTROL BOARDS                | -3  |

| Main Control Board                     | -3  |

| Memory Control Board                   | -3  |

| Trace/Break Board                      |     |

| Overlay Memory Board(s)                | -3  |

| Emulation Board                        |     |

| EMULATOR CHASSIS REAR PANEL            | -6  |

| Serial Ports                           | -6  |

| Trigger Output3                        | -6  |

| Power Switch                           |     |

| Line Fuse                              | -7  |

| POD ASSEMBLY                           | 8-8 |

| Saving Desk Space 3-                   |     |

| NULL TARGET SOFTWARE SIMULATION TOOL3- | -10 |

| LOGIC STATE ANALYZER (LSA) ASSEMBLY    | -11 |

| SERIAL PORTS3-                         | -12 |

|                                                                                                                                                               | Page                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Baud Rate                                                                                                                                                     | 3-12                                         |

| Port Control.                                                                                                                                                 | 3-12                                         |

| Upload/Download                                                                                                                                               | 3-12                                         |

| Pin Configurations                                                                                                                                            | 3-12                                         |

| Data Requirements                                                                                                                                             |                                              |

| Stop Bits                                                                                                                                                     | 3-14                                         |

| Parity                                                                                                                                                        | 3-14                                         |

| Hardware Handshake                                                                                                                                            | 3-14                                         |

| Software Handshake XON XOFF                                                                                                                                   | 3-14                                         |

| MAINTENANCE                                                                                                                                                   | 3-16                                         |

| Cables                                                                                                                                                        | 3-16                                         |

| Probe Tip Assembly                                                                                                                                            | 3-16                                         |

| Cleaning the Fan Filter                                                                                                                                       | 3-17                                         |

| Parts                                                                                                                                                         | 3-20                                         |

| TROUBLESHOOTING                                                                                                                                               | 3-21                                         |

| ES1800 EMULATOR SPECIFICATIONS                                                                                                                                | 3-23                                         |

| Input Power                                                                                                                                                   | 3-23                                         |

| Standard                                                                                                                                                      | 3-23                                         |

| Optional                                                                                                                                                      | 3-23                                         |

| - P                                                                                                                                                           |                                              |

| Environmental                                                                                                                                                 | 3-23                                         |

|                                                                                                                                                               |                                              |

| Environmental                                                                                                                                                 | 3-23                                         |

| Environmental Operating Temperature                                                                                                                           | 3-23<br>3-23                                 |

| Environmental.  Operating Temperature.  Storage Temperature.                                                                                                  | 3-23<br>3-23<br>3-23                         |

| Environmental. Operating Temperature. Storage Temperature. Humidity.                                                                                          | 3-23<br>3-23<br>3-23                         |

| Environmental. Operating Temperature. Storage Temperature. Humidity. Physical.                                                                                | 3-23<br>3-23<br>3-23<br>3-23                 |

| Environmental. Operating Temperature. Storage Temperature. Humidity. Physical. Mainframe.                                                                     | 3-23<br>3-23<br>3-23<br>3-23<br>3-23         |

| Environmental. Operating Temperature. Storage Temperature. Humidity. Physical. Mainframe. Emulator Pod.                                                       | 3-23<br>3-23<br>3-23<br>3-23<br>3-23         |

| Environmental. Operating Temperature. Storage Temperature. Humidity. Physical. Mainframe. Emulator Pod. Target System Connection (total length including pod) | 3-23<br>3-23<br>3-23<br>3-23<br>3-23<br>3-24 |

### **HARDWARE**

## **Emulator Chassis Assembly**

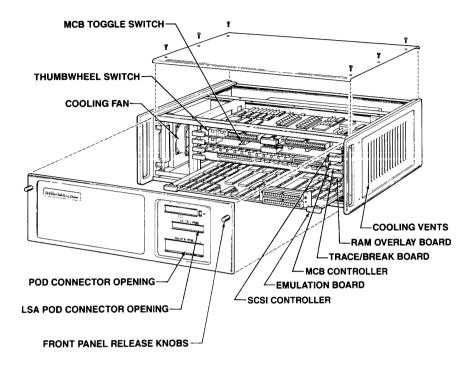

The Emulator chassis is the metal enclosure housing the control boards for your target system. This rack mountable chassis houses up to six boards as shown in the Figure on page 3-4.

The Emulator power supply is also in this chassis. A power switch on the rear panel is the only external panel control.

#### **WARNING!**

A cooling fan and vent for the Emulator are located on the *left* side panel of the chassis. The warm air exhaust vent is in the *RIGHT* side panel. Blocking either of these panels may cause the Emulator to overheat.

#### SYSTEM GROUNDS

The ES1800 Emulator has three grounding systems:

- 1. A CHASSIS ground from the metallic enclosure of the unit to the power filter.

- 2. An AC PROTECTIVE ground from the green ground wire of the AC power cord and the chassis ground at the power filter.

3. A SIGNAL ground connected by a jumper at the power supply terminal strip to the chassis ground. The Emulator has a three-wire power cord with a three-terminal polarized plug. The ground terminal of the plug is connected internally to the metal chassis parts of the Emulator

#### **WARNING!**

Failure to ground the system properly may create a shock hazard.

### **Emulator Control Boards**

Removing the front panel of the Emulator chassis exposes the chassis card cage as shown on page 3-4. This panel is opened by turning two knobs, located in the upper corners of the front panel, counterclockwise.

Main Control Board

The main control board holds the controlling 6809 CPU for the Emulator, the EEPROM, two serial ports, and RAM. The 16-position thumbwheel switch located on this board determines the system variables and serial line baud rates for autoloading on power-up. Refer to page 3-5, for each switch position setup. Switch position 0 autoloads default system variables.

Memory Control Board

The memory control board holds the memory management logic and optional symbolic debug memory. The three-position toggle switch located below the main control board thumbwheel switch must be in the center position. If the toggle switch is in either of the other two positions the Emulator will not work properly.

Trace / Break Board

The trace/break board holds trace memory, the Event Monitor System, and the logic state analyzer (LSA) interface.

Overlay Memory Board(s)

The overlay memory board set is optional and can hold 32K, 64K, 128K, 256K or 512K of memory. 512K of memory requires a slave board.

Emulation Board

There are six different emulation boards depending on the target microprocessor you are using.

Figure 2. Control Boards

#### Emulation Board Thumbwheel Switch Settings

| POSITION | PARAMETERS                           | BAUD RATE                        |

|----------|--------------------------------------|----------------------------------|

| 0<br>1   | Factory Default*<br>User "O" defined | 9,600<br>User defined            |

| i        | oser "o" dermed                      | Terminal control                 |

| 2        | User "1" defined                     | User defined                     |

| 3        | User "0" defined                     | Terminal control<br>User defined |

| ,        | tiene nan de Cienti                  | Computer control                 |

| 4        | User "1" defined                     | User defined<br>Computer control |

| 5        | Factory Default*                     | 110                              |

| 6        | Factory Default*                     | 300                              |

| 7        | Factory Default*                     | 1,200                            |

| 8        | Factory Default*                     | 2,400                            |

| 9        | Factory Default*                     | 4,800                            |

| A        | Factory Default*                     | 7,200                            |

| В        | Factory Default*                     | 19,200                           |

| C,D,E,F  | Reserved for factory us              | se                               |

#### \*Factory Default Parameters

- 8-bit word length - one stop bit

- no parity

full duplex

- Terminal control

- XON and XOFF are recognized

- no echo

- baud rate the same for both terminals

- 8th data bit set to 0 or a space

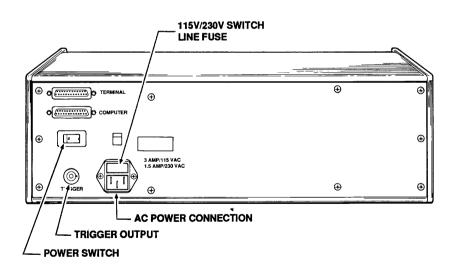

### **Emulator Chassis Rear Panel**

The rear panel of the Emulator mainframe is shown in Figure 3 on page 3-7.

Serial Ports

The two serial ports are RS 232C ports labeled <u>TERMINAL</u> and <u>COMPUTER</u>. Pins are discussed on page 3-12.

System configuration determines which port your peripheral equipment connects to (see page 1-4).

Trigger Output

The ES1800 Emulator provides a TTL trigger strobe output controlled by the Event Monitor System. The trigger output is available at a BNC connector on the rear panel of the chassis and on a clip lead attached to the optional Logic State Analyzer (LSA) pod. Refer to Section 7 (68000/08/10) or Section 8 (68020) for information on Event Monitor System actions.

The trigger can be used for such things as:

- Synchronizing an oscilloscope to the execution of an I/O routine.

- Measuring the duration of a routine by asserting the trigger for its duration and using a timer-counter.

- Cross-coupling two or more Emulators so that an event in one can control events in the others.

### Power Switch

Before powering up, two items should be checked:

- 1. Proper grounding of power cable (see page 3-1).

- 2. Proper power-up sequence of Emulator, target system, and/or peripheral equipment. (See Power-On Sequence, page 2-5.)

Line Fuse

A 3 amp slow-blow fuse for 110V operation or a 1.5 amp slow-blow fuse for 220V operations. Remove the fuse by turning the fuse holder counterclockwise.

Figure 3. Rear Panel

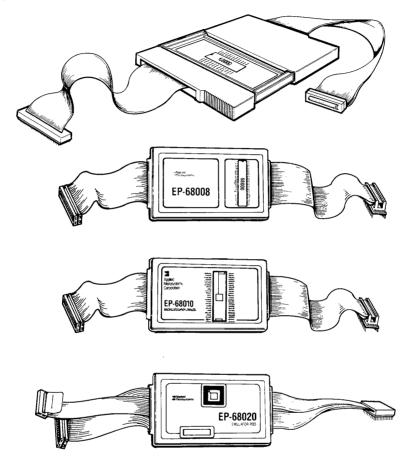

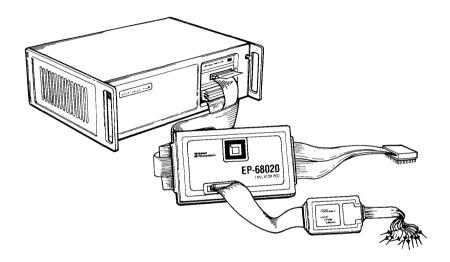

## **Pod Assembly**

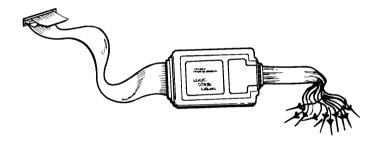

The pod assembly is the communications link between the ES1800 Emulator and your target system. A 40 inch ribbon cable connects the pod assembly to the Emulator board. An 11 inch ribbon cable ends in a probe tip that is normally inserted into the microprocessor socket in your target system.

The proper pod assembly is determined by the microprocessor being emulated.

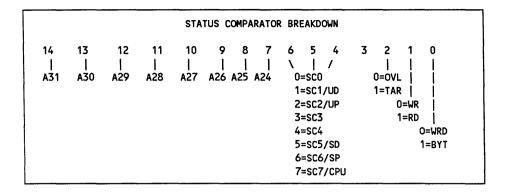

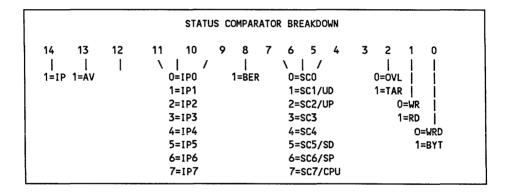

#### 68020:

The 68020 microprocessor has four trace memory modes. Each mode requires a different Emulator/pod assembly configuration.

The 68020 pod has three ribbon cables that connect to the emulator chassis. All three cables are located on the same side of the 68020 pod. The bottom two ribbon cables for all four trace modes, always connect to the Emulator chassis' emulation board. For modes 1, 2, and 3 the top ribbon cable connects to the Emulator chassis trace and break board. For mode 0 this top cable is not used and in its place the LSA pod assembly is connected to the trace and break board. The lower six LSA bits are available in mode 3 if you choose to use them. To do so, the LSA pod assembly connects to the front panel of the 68020 pod.

Refer to page 8-14 for more information on 68020 trace modes.

Figure 4. Pod Assemblies

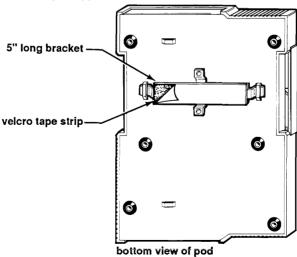

## **Saving Desk Space**

To save limited desk or table space, the ES 1800 68000 16.67 MHz pod can be supported from walls, an overhead hook, or other non-horizontal surfaces either by velcro tape or by a hanging strap.

### **Velcro Tape**

To support the pod using velcro tape, you must first attach the 5" long bracket to the bottom sheet metal of the pod (you may have to bend the bracket slightly). Figure 1-1 shows bracket placement. When the bracket is in place, simply peel off the adhesive backing on the velcro tape strip and firmly press the tape onto the bracket as shown in Figure 1-1. You can now attach the 68000 pod to any surface that adheres to velcro, such as many types of office partitions.

Figure 3-1: Velcro Tape Support

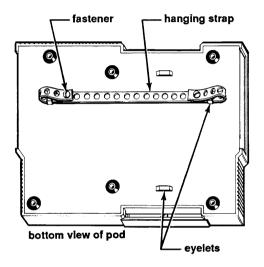

## **Hanging Strap**

The hanging strap can be threaded through either set of eyelets on the bottom sheet metal of the pod. The 5" long bracket is not needed when using the hanging strap. Figure 1-2 shows both of these configurations. After threading the strap through the eyelet, bend the strap back on itself and fasten it with the enclosed fasteners. Make sure the fasteners on both sides are firmly closed before hanging the pod from the strap.

Figure 3-2: Hanging Strap Support

## **Null Target Software Simulation Tool**

The Null Target Software Simulation Tool is a device that is about the size and shape of a microprocessor chip. It is to be plugged onto the end of your pod assembly probe tip adapter. This device allows you to run the ES1800 Emulator without having to be connected to a target system.

## Logic State Analyzer (LSA) Assembly

An optional feature, the Logic State Analyzer (LSA) pod assembly connects directly above the Emulator pod assembly. The LSA assembly includes a pod, cables, and probe clips. The LSA pod provides 16 input lines and one trigger output line.

The one trigger output line behaves the same as the BNC signal on the rear panel of the Emulator and can be used with an oscilloscope.

Figure 5. Logic State Analyzer Pod Assembly

### **Serial Ports**

Both the terminal port (TERMINAL) and the computer port (COMPUTER) end in standard RS232C female connectors. Make sure peripheral hardware is connected to the correct port.

Baud rates and data lengths for each port

are independent. Refer to the SET command (page 5-3) for available baud

rates on each port.

Port Control Only one port can be the controlling port.

Either port can give control to the other

port.

Upload/Download The Emulator accepts commands to begin

uploading/downloading from either port. However, the Emulator will upload/download hex format data files only

through the computer port.

Your system configuration determines which port should be in control. Refer to page 1-4.

#### PIN CONFIGURATIONS

The pin configuration of your equipment (terminal, PC or host) may not match that of the Emulator. It is important to be familiar with the pin configurations of all peripheral equipment you intend to use with the ES1800 Emulator.

The ES1800 Emulator is configured as "Data Terminal Equipment" (DTE). Before powering up, make sure the ES1800 Emulator system and peripheral hardware are compatible. Pins 1, 2, 3 and 7 must be connected to peripheral hardware. Pins 4 and 5 need to be connected if peripherals attached to the Emulator use these pins.

Both Emulator serial ports use the same pin assignment. All pin assignments and voltage levels conform to Electronics Industries Association (EIA) RS232C standards. The following chart lists the signals present on each pin.

| Pin  | Name                     | Description                                                                                                                                                                                  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Protective Ground        | Connected in the Emulator to logic ground.                                                                                                                                                   |

| 2    | Serial Data Out          | This signal is driven to nominal ±12 voltage levels by an RS232C compatible driver.                                                                                                          |

| 3    | Serial Data In           | Data is accepted on this pin if the voltage levels (±12V) are as specified by RS232C specifications.                                                                                         |

| 4    | Request to Send (Output) | This signal is driven to nominal ±12V levels by an RS232C compatible driver. It signals other equipment that the Emulator is ready to accept data at this port.                              |

| 5    | Clear to Send (Input)    | An input signal to the Emulator indicates another piece of equipment in the system is ready to accept data. This signal is terminated so the Emulator operates with the signal disconnected. |

| 6    | Not Used                 |                                                                                                                                                                                              |

| 7    | Signal Ground            | Connected in the Emulator to the system logic ground.                                                                                                                                        |

| 8-25 | Not Used                 | These pins are not used by the ES1800 Emulator but may be required by your peripheral hardware.                                                                                              |

### **DATA REQUIREMENTS**

Stop Bits

The Emulator software transmits and receives 8 bit ASCII characters. The number of stop bits is determined by SET parameter #11 for the TERMINAL port and #21 for the COMPUTER port (see page 5-3).

Parity

The Emulator sends and checks parity according to system SET parameter #12 for the terminal port and #22 for the computer port. These two SET parameters are listed in the SET MENU (page 5-3).

Each character consists of a start bit followed by 8 data bits. When no data is being transmitted, the serial data out pin (pin #2) will be at the 12 volt level.

Hardware Handshake

When the Emulator is ready to receive data, it asserts the Request To Send line (pin #4). When a receive buffer is nearly full, the Emulator will deassert the Request To Send line.

When the Emulator is ready to transmit data, it checks the status of the Clear To Send line (pin #5). Data will only be transmitted when Clear To Send is high.

Software Handshake XON XOFF The ES1800 uses normal flow control codes to control software handshaking. The default values are XON CTRL Q and XOFF CTRL S. These values can be changed by the user (see page 5-4).

The ES1800 serial I/0 system contains internal buffers to smooth the transmission of data via the serial ports. If an input buffer becomes nearly full, the system

immediately transmits an XOFF character. When the software empties the input buffer, an XON character is transmitted.

Although the user will never overfill the input buffer from a controlling terminal, a controlling computer is quite capable of doing so. The input buffer for the computer port is 64 characters deep. When eight characters have been placed in the computer input buffer, the XOFF character is transmitted. Allowing two character times for skew, the computer must transmit no more than 54 characters until the next XON from the ES1800.

The RTS hardware handshake follows the software handshake described above. When an XOFF is transmitted, RTS is dropped on that I/O port; when an XON is transmitted, RTS is reasserted.

### Maintenance

Maintenance of the ES1800 Emulator has been minimized by the extensive use of solid-state components throughout the instrument. There are three areas where you need be concerned.

#### **CABLES**

The interconnect cables are the most vulnerable part of the instrument, due to constant flexing during insertion and extraction. First, inspect the cables for any obvious damage, such as cuts, breaks, or tears. Even if you have thoroughly inspected the cables and cannot find any damage, there may be broken wires within the cables (usually located close to the ends). A broken wire within the cable will cause the instrument to run erratically or intermittently if the cables are flexed during emulation mode. By swapping the cables in question with a known good set of cables, you can easily isolate the faulty cable.

#### PROBE TIP ASSEMBLY

The probe tip assembly is the small header assembly that plugs into the target system microprocessor socket. The most obvious area to inspect is the adapter, as the pins can be broken during insertion or extraction.

The adapter can be protected by installing a microprocessor socket (male-female) onto the adapter. If a pin is then broken on the socket, it is easier to replace because of its common usage.

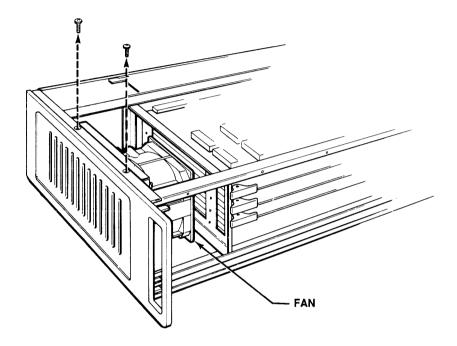

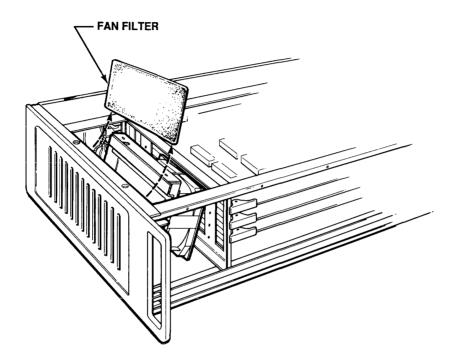

#### **CLEANING THE FAN FILTER**

The fan filter should be cleaned regularly. The recommended interval is every 90 days. If you are working in a dusty environment, you may need to clean the filter more frequently.

1. Unplug the ES 1800.

#### **WARNING!**

Electrical shock and moving fan parts are dangerous. Make sure you unplug the unit before proceeding.

- 2. Remove the front cover of the ES 1800. (Loosen the two captive fasteners.)

- 3. Remove the top cover of the ES 1800. (Unscrew six screws and lift the cover off.)

4. Unscrew the two screws at the top of the chassis which hold the fan in place.

ES 1800 Fan Mounting

5. Tilt the fan towards the boards in the chassis.

ES 1800 With Fan Titled for Easy Access to Filter

- 6. Remove the fan filter.

- 7. Rinse the fan filter in cold water. Thoroughly shake out the excess water.

- 8. Replace the fan filter.

- 9. Tilt the fan back into the correct position.

- 10. Replace the screws connecting the top of the chassis to the fan.

- 11. Replace the top and front covers.

### **PARTS**

The following parts are available for you to order:

48 pin adapter (68008 chip) 64 pin adapter (68000/68010 chips) 114 pin grid adapter (68020 chip) Short cable set Long cable set

## **Troubleshooting**

Check that the interconnect cables are installed properly in a compatible target system, with power applied to both the target system and the Emulator before starting troubleshooting procedures.

The most common problems encountered are listed below. We recommend that you contact Customer Service at Applied Microsystems Corporation (1-800-426-3925) if you experience any problems that do not fall within this range of items. Before you call our service department, display your software revision number by typing REV (page 5-135). You will be asked for this when you call.

We do not recommend a component-level repair in the field, unless performed by a qualified service engineer.

|                   | Troubleshooting                                                                                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMPTOM           | POSSIBLE CAUSES                                                                                                                                                                                |

| Target system     | 1. Faulty interconnect cables                                                                                                                                                                  |

| rano di racioaccy | 2. Broken pin on adapter                                                                                                                                                                       |

|                   | 3. Emulator and target system not compatible                                                                                                                                                   |

|                   | 4. LDV not executed before RUN (vector not loaded).                                                                                                                                            |

| Emulator will     | 1. Baud rate set incorrectly.                                                                                                                                                                  |

| over RS232        | <ol><li>Target system requires "null" modem<br/>cable (pin 2 and pin 3 of RS232 connector<br/>reversed).</li></ol>                                                                             |

|                   | 3. For terminal operation, thumbwheel switch located<br>on the top card is not in the "O" position or<br>the cable is not properly attached to the<br>terminal port in the back of the ES1800. |

|                   | <ol><li>Cable not going to correct port of the terminal<br/>or PC.</li></ol>                                                                                                                   |

|                   | <ol><li>Toggle switch located on the second card from the<br/>top in the ES1800 not in the middle position.</li></ol>                                                                          |

|                   | 6. Power LED not on.                                                                                                                                                                           |

|                   | 7. Cards not seated properly.                                                                                                                                                                  |

## **ES1800 Emulator Specifications**

#### **INPUT POWER**

Standard 90 to 130 VAC

47 to 60 Hz

consumption less than 130W

Optional 180 to 260 VAC

47 to 50 Hz

consumption less than 130W

**ENVIRONMENTAL**

Operating Temperature 0 °C to 40 °C (32 °F to 104 °F)

Storage Temperature -40 °C to 70 °C (-40 °F to 158 °F)

Humidity 5% to 95% relative humidity, non-

condensing

**PHYSICAL**

Mainframe 13.2 cm x 43.18 cm. x 34.29 cm.

(6.2 in. x 17 in. x 13.5 in)

Emulator Pod 22.6 cm. x 12.9 cm. x 4.1 cm.

(8.9 in. x 5.1 in. x 1.6 in.)

## ES 1800 Emulator Reference Manual for 68000 Series Microprocessors

Target System 1.5 m (60 inches)

Connection (total length including pod)

LSA Pod 12.4 cm. x 7.9 cm. x 2.3 cm.

(4.9 in. x 3.1 in. x .9 in.)

Total Weight 9.1 kg. (20 lbs.)

Shipping 10.9 kg. (24 lbs.)

## **SECTION 4**

### **Table of Contents**

# **ES Language**

|                                        | Page |

|----------------------------------------|------|

| STRUCTURE OF THE ES LANGUAGE           | 4-1  |

| NOTES ON ESL                           | 4-6  |

| Command Line                           | 4-6  |

| Repeat                                 | 4-6  |

| Command Statement                      | 4-6  |

| Single Character Instant Commands      | 4-7  |

| Command Mnemonics                      | 4-8  |

| Expression.                            | 4-8  |

| Symbols                                | 4-10 |

| Numbers                                | 4-10 |

| Base                                   | 4-11 |

| Expression List                        | 4-12 |

| Assignment Command                     | 4-12 |

| Event Monitor System Control Statement | 4-14 |

| Group                                  | 4-15 |

| Event                                  | 4-15 |

| Disjunctive                            | 4-15 |

| Conjunctive                            | 4-16 |

| Unary Operator                         | 4-16 |

| Operator                               | 4-17 |

| Modulo (MOD)                           | 4 17 |

| Page                                      |   |

|-------------------------------------------|---|

| HELP4-20                                  |   |

| Software Switches 4-20                    |   |

| Communications Set-up. 4-20               |   |

| Special Diagnostic Functions4-20          |   |

| Special Diagnostic Functions4-20          |   |

| <b>LOG IN BANNER</b> 4-25                 |   |

| <b>PROMPTS</b> 4-27                       |   |

| > 4-27                                    |   |

| R>4-27                                    |   |

| SPECIAL MODES4-28                         |   |

| Byte Mode/ Word Mode/ Long Word Mode 4-28 |   |

| Line Assembler                            |   |

| Memory Disassembler4-29                   |   |

| Memory Mode                               |   |

| Transparent Mode                          |   |

| Special Functions. 4-29                   |   |

| Repeating Command Lines                   |   |

| SPECIAL CHARACTERS 4-31                   |   |

| DELETE 4-31                               |   |

| BACKSPACE4-31                             |   |

| CTRL X                                    |   |

| CTRL R                                    |   |

| CTRL Z                                    |   |

| ESC ESC. 4-31                             |   |

| CTRL S                                    |   |

| CTRL Q                                    |   |

| <b>ERRORS</b> 4-32                        | 2 |

| ES LANGUAGE ERROR MESSAGES 4-33           | 3 |

### **ES LANGUAGE**

## Structure of the ES Language

The command language used to control the ES1800 Emulator is a formal language. Once you understand the basic concepts of this language, you can apply the full debugging power of the Emulator. An overview of the structure of the ES language is presented in the accompanying table. A more detailed description of the language elements, the help menus, prompts, special operating modes, and ES language error messages are also included in this section. Items in angle brackets ( ) are mandatory and must be entered as part of the command.

Items shown in square brackets ([1]) are optional. Do not type the angle or square brackets when typing a command.

If the ESL command interpreter detects an illegal statement, it beeps and places a question mark under the command line at the position the error was detected. Entering a ? following an error will cause the appropriate error message to be displayed.

## ES Language Syntax

| Language Element                                                                             | Example               |

|----------------------------------------------------------------------------------------------|-----------------------|

| Command Line [Repeat] Command Statement [;Command Statement Single Character Instant Command | nt] <return></return> |

| Repeat                                                                                       |                       |

| <*>                                                                                          | *STP;DT               |

| <*> <repeat limit=""></repeat>                                                               | *9 STP;DT             |

| Repeat Limit:                                                                                |                       |

| Decimal number only $(1 \text{ to } 2^{32}-1)$                                               | 87651234              |

| Command Statement                                                                            |                       |

| Command Mnemonic                                                                             | DTB                   |

| Command Mnemonic < Expression >                                                              | MM PC + 4             |

| Command Mnemonic < Expression List>                                                          | SET #20,#14           |

| Assignment Command                                                                           | DO = 0FA9             |

| Expression                                                                                   | 2 * GR5               |

| Event Monitor System Control Statement                                                       | WHEN AC1 THEN BRK     |

| Single Character Instant Command                                                             |                       |

|                                                                                              |                       |

| <,>                                                                                          |                       |

| <.>                                                                                          |                       |

|                                                                                              |                       |

| Command Mnemonic                                                                             |                       |

| <1 or more alpha characters>[1 or more decimal ch                                            | aracters]             |

| Expression                                                                                   |                       |

| [Unary Operator] Ivalue                                                                      | -2473                 |

| Ivalue <operator> Expression</operator>                                                      | 2 - 3F6C90            |

| <@> Expression                                                                               | a240;aaA7             |

| <(> Expression <)>                                                                           | 2 * (-2 + 3)          |

|                                                                                              |                       |

## ES Language Syntax (cont)

| Language Element                             | Example                                    |

|----------------------------------------------|--------------------------------------------|

| Ivalue:                                      |                                            |

| Symbol                                       | 'main                                      |

| Nvalue                                       |                                            |

| Symbol:                                      |                                            |

| <'><1 or more printable characters>          | <pre><space or="" return=""></space></pre> |

| Nvalue:                                      |                                            |

| Number                                       | 7fA36                                      |

| Register Name                                | AO                                         |

| Register Name:                               |                                            |

| <1 - 3 Alpha characters>[0 - 2 decim         | al digits]                                 |

| Number:                                      |                                            |

| [Base]<1 or more digits>                     | %0101001                                   |

| Base:                                        |                                            |

| <%> (binary)                                 |                                            |

| <\> (octal)                                  |                                            |

| <#> (decimal)                                |                                            |

| <\$> (hexadecimal)                           |                                            |

| Expression List                              |                                            |

| Expression <,> Expression [,Expression list] | 1,PC,2+2,-6                                |

| Assignment Command                           |                                            |

| Svalue <=> Expression                        | A6 = @OFFFFO                               |

| <@> Expression <=> Expression                | a(A6 + 5) = GD3                            |

| Svalue:                                      |                                            |

| Symbol                                       | 'Test_result                               |

| Register Name                                | MMP                                        |

### ES Language Syntax (cont)

| Language Element                                                                   | Example           |

|------------------------------------------------------------------------------------|-------------------|

| Event Monitor System Control Statement                                             |                   |

| $[Group] < \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | WHEN AC1 THEN BRK |

| Group:                                                                             |                   |

| <1>                                                                                |                   |

| <2>                                                                                | 2 WHE AC1 THE BRK |

| <3>                                                                                |                   |

| <4>                                                                                |                   |

| Event:                                                                             |                   |