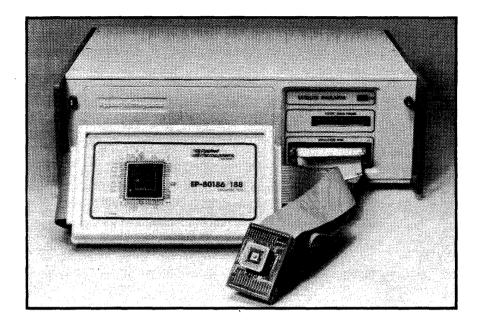

# ES 1800 SATELLITE EMULATOR OPERATOR'S MANUAL

FOR 80186/88 MICROPROCESSORS

CORPORATION

5020 148th Avenue N.E. P.O. Box 97002 Redmond, WA 98073-9702 (206) 882-2000 1-800-426-3925

920-11437-01 December 1985

# SET-UP CHECKLIST 80186/88

Please read this checklist completely before using your new Applied Microsystems' Satellite Emulator.

- 1. Have you reviewed the specifications for the serial interface port? See Sections 2.3.3 and 2.3.4.

- 2. If using communications without a modem, you may need a null modem cable. Example:

\*Check the specifications in your terminal manual before reversing the pins.

3. At a minimum, you should review sections applicable to the steps listed here, plus "Getting Started With The 80186 or 80188."

If you experience difficulty in setting up your Satellite Emulator, call Customer Services for ES products at 1-800-426-3925.

PLACE CHECKLIST INSIDE FRONT COVER FOR FUTURE REFERENCE

5020 148th Avenue N.E. Redmond, WA 98052 or Box C-1002 Redmond, WA 98073-1002 Toll Free Service: 1-800-426-3925

## GETTING STARTED WITH THE 80186 or 80188

The 8Ø186 or 8Ø188 microprocessors include on-chip peripheral circuits which offer many benefits to the user. The addition of these on-chip peripheral circuits adds a degree of complexity to development workstations not previously encountered with either the 8Ø86 or 8Ø88 microprocessors. As you might expect, this adds greatly to the complexity of emulation, particularly in the area of setting up an emulator to run with the target system.

This document should help identify obstacles to the installation and operation of the emulator/target workstation. To help ensure a successful and speedy start up, please follow these step-bystep instructions.

#### STEP 1: SET UP THE EMULATOR/TARGET WORKSTATION

Connect the emulator to your target. Refer to section 2 of the Operator's Manual.

Apply power to your emulator then to your target system.

STEP 2: SET UP THE PCB RELOCATION REGISTER

Note: If you do not relocate the Peripheral Control Block from  $FF\emptyset\emptyset$  in I/O space, then go to Step 3.

ENTER: REL = register-value <Return>\*

\*Refer to an Intel  $8\emptyset 186$  User's Guide for the proper way to set up the register.

- STEP 3: SET UP THE ON-CHIP CHIP SELECT PERIPHERAL Note: If you do not use on-chip chip selects, then go to Step 4.

- ENTER: ON RCS <Return> With RCS set to ON, the following will be true:

PAUSE-TO-RUN transitions will write the emulator chip select PCB values into the target PCB. RUN-TO-PAUSE transitions will read the emulator chip select PCB values from the target PCB.

ENTER: Values needed for UMCS, LMCS, MPCS, MMCS and PACS registers, as: UMCS = register value <Return>.\*

> \*Refer to an Intel 80186 User's Guide for the proper way to set up the register.

- STEP 4: SET UP THE ON-CHIP DMA PERIPHERAL

- Note: If on-chip DMA circuitry is not used, then go on to Step 5.

ENTER: Values needed for USRCO, SRCO, UDSTO, DSTO, XCO and CWO registers, as: USRCO = register\_value <Return>.\*

\*Refer to the intel 80186 User's Guide for the proper set up.

- Note: If you do not need DMA active while paused, then go on to Step 5.

- ENTER: ON DME <Return>

## STEP 5: SET UP THE ON-CHIP TIMER PERIPHERAL

- Note: If on-chip timer circuitry is not used, then go on to Step 6.

- ENTER: Values needed for TCØ, TC1, TC2, MAØ, MA1, MA2, MBØ, MB1, MB2, MCWØ, MCW1 and MCW2 registers, as: TCØ = register value  $\langle \text{Return} \rangle$ .\*

\*Refer to the Intel 80186 User's Guide for the proper set up.

Note: If you need a timer circuit active while paused, then turn on the appropriate emulator software switch, as: ON TEØ <Return> for timer zero, and/or ON TE1 <Return> for timer one, and/or ON TE2 <Return> for timer three.

## STEP 6: SET UP THE ON-CHIP INTERRUPT CONTROL PERIPHERAL

- Note: If on-chip Interrupt Control circuitry is not used, then proceed to Step 7.

- ENTER: Values needed for INTØ, INT1, INT3, EOI, POL, POS, MSK, PLM, ISV, IRQ, IST, TCR, DMAØ, DMA1, and DMA2 registers, as: INTØ = register\_value <Return>\*

\*Refer to the Intel 80186 User's Guide for the proper set up.

## STEP 7: SET UP OVERLAY AND A MINIMAL PROGRAM

- Note: This step assumes you have neither target memory nor a valid program located at the startup location (\*FFFFØ). If you have target memory and a valid program then go on to Step 8.

- ENTER: MAP \$FF800;DM <Return> This will map in overlay from \$FF800 to \$FFFFF and display the memory map.

- ENTER: ON RDY <Return> This will ensure that Reads and Writes to overlay use the emulator's internal ready signal.

- ENTER: ASM <Return> This will invoke the single-line assembler to enter a sequence of NOP instructions.

- ENTER: CSEG =  $\emptyset$ FFFF <Return> This will set the assembler to an absolute address of \$FFFF $\emptyset$ .

- ENTER: NOP <Return> (repeat several times) This throw-away program is used to initialize the on-chip peripheral circuitry.

- ENTER: X <Return> This will exit the assembler.

## STEP 8: ACTIVATE THE ON-CHIP PERIPHERALS

- Note: The following tasks should have been accomplished before reaching this point:

- 1) The state of all on-chip peripherals should have been set up via the PCB registers.

1 og 1 18

س في

- The emulator's ON or OFF software switches have been properly set up.

- 3) A program resides at the start up location ( $FFFF\emptyset$ ).

- ENTER: ACl = stopping\_point <Return> This will define the stopping point of the program which should follow the initialize section.

- Note: The on-chip peripherals are activated by either a Read from, or Write to appropriate registers. The setting of the emulator's switches to ON guarantees the chosen peripheral registers will be written and read following the execution of at least one instruction cycle. Therefore, set up AC1, as either:

- ACl = \$FFFF2 (if manually initializing and using the NOP program in Step 7),

- or,

- ACl = stopping\_point (if using your own PCB initialization program).

- ENTER: WHEN AC1 THEN BRK This will allow a breakpoint when AC1 is recognized during emulation.

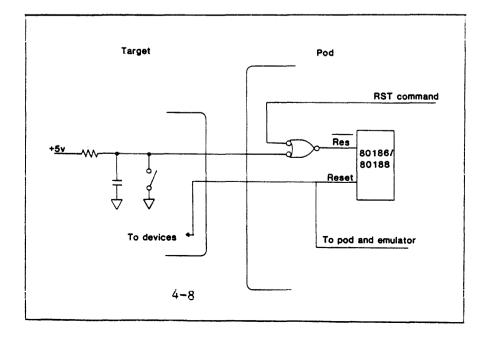

ENTER: RST; RBV <Return>

RST sends a reset signal to the target system via the RESET OUT line.

RBV sets CS: IP registers to the absolute address of  $FFFF\emptyset$ , activates the event monitor system, and initiates a real-time run.

This concludes the initial startup procedure. At this point, the PCB has been initialized and the emulator set up for further use. You should be able to perform normal emulator functions.

Applied Microsystems Corporation has made every effort to document this product accurately and completely. However, Applied Microsystems assumes no liability for errors or for any damages that result from use of this manual or the equipment it accompanies. Applied Microsystems reserves the right to make changes to this manual without notice at any time.

Because this configuration of the ES1800 Satellite Emulator is intended for use in developing, debugging, and testing Intel 80186/88 microprocessor-based systems, it is presumed that the user is familiar with the terminology of the 80186/88 microprocessors.

WARNING - This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

| QUIC | K-INDEX TO COMMANDS                                | vi   |

|------|----------------------------------------------------|------|

|      | OF FIGURES                                         | x    |

|      | OF TABLES                                          | xi   |

| LIST | OF EXAMPLES                                        | xii  |

| SECT | ION 1. INTRODUCTION                                |      |

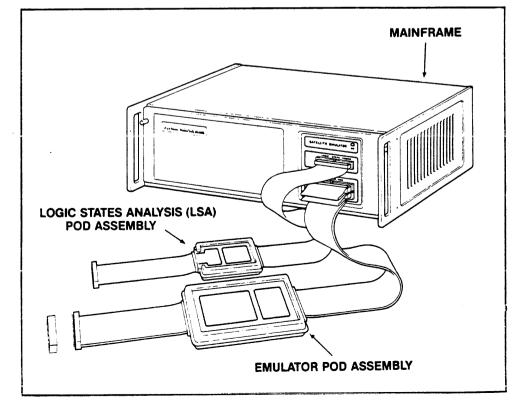

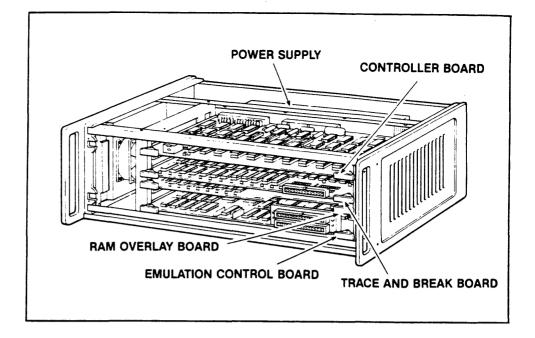

| 1.1  | SYSTEM CONCEPT                                     | 1-2  |

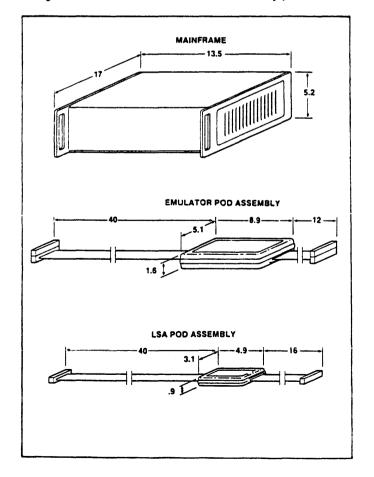

|      | 1.1.1 Components                                   | 1-2  |

|      | 1.1.2 The Target System                            | 1-3  |

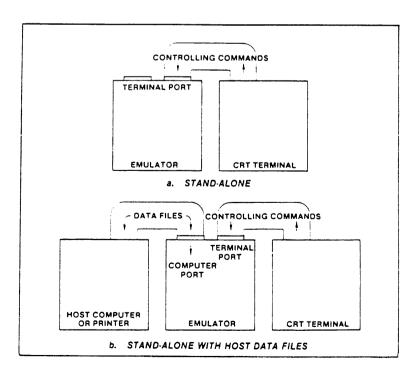

|      | 1.1.3 The Host System                              | 1-4  |

|      | 1.1.4 System Configurations                        | 1-4  |

|      | 1.1.5 System Features                              | 1-5  |

| 1.2  | DOCUMENTATION                                      | 1-7  |

| 1.3  | 8086 APPLICATIONS                                  | 1-8  |

| 1.4  | OPTIONS                                            | 1-8  |

| 1.5  | SPECIFICATIONS                                     | 1-9  |

| 1.6  | LIMITED WARRANTY                                   | 1-10 |

| 1.7  | SERVICE                                            | 1-10 |

|      |                                                    |      |

| SECT | ION 2. INSTALLATION AND SET UP                     |      |

| 2.1  | UNPACKING AND INSPECTION                           | 2-2  |

| 2.2  | OPERATING VOLTAGE AND GROUNDING                    | 2-2  |

| 2.3  | SYSTEM INTERFACING                                 | 2-3  |

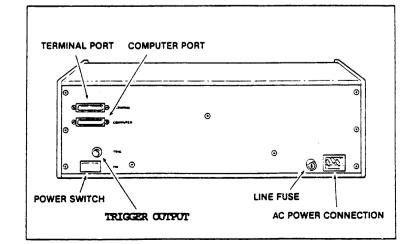

|      | 2.3.1 The Rear Panel                               | 2-3  |

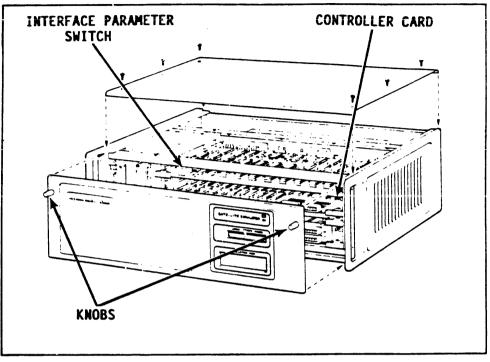

|      | 2.3.2 The Side Panel                               | 2-4  |

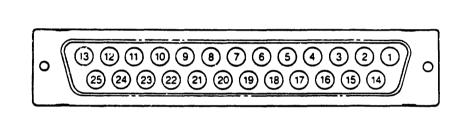

|      | 2.3.3 Serial Port Connector Pin Assignment         | 2-4  |

|      | 2.3.4 Setting Interface Parameters                 | 2-6  |

| 2.4  | PHYSICAL CONNECTION                                | 2-7  |

|      | 2.4.1 Connection to a CRT Terminal                 | 2-7  |

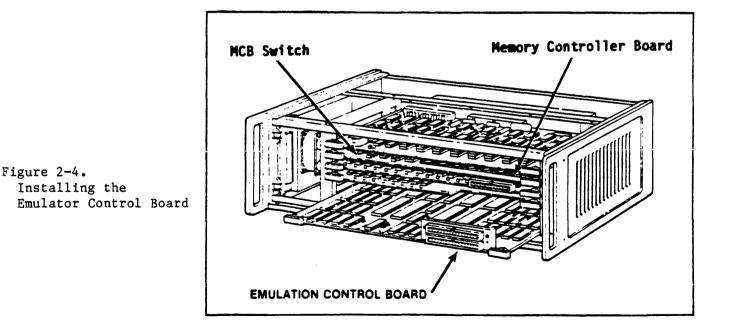

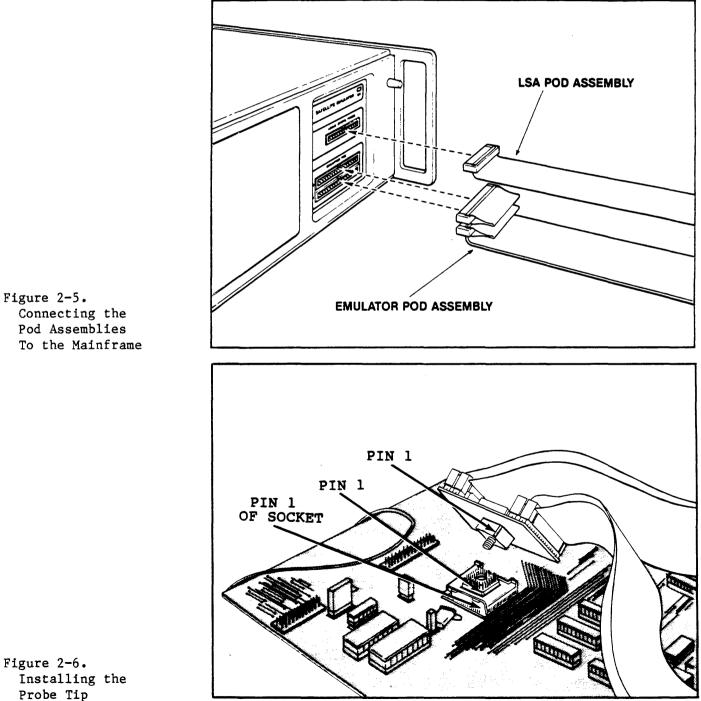

|      | 2.4.2 Connection to a Target System                | 2-8  |

| 2.5  | SYSTEM POWER-UP AND CHECKOUT                       | 2-10 |

|      | PRE-EMULATION CHECKLIST AND THE HELP MENU          | 2-11 |

|      | 2.6.1 Parameter Set-Up and EEPROM Storage Overview | 2-13 |

| SECT | ION 3. SYSTEM SYNTAX AND PARAMETERS                |      |

|      |                                                    |      |

| 3.1 | INTRODUCTION                                 | 3-2  |

|-----|----------------------------------------------|------|

| 3.2 | STANDARD CHARACTERS                          | 3-2  |

|     | 3.2.1 The Prompt Character                   | 3-2  |

|     | 3.2.2 The Run Prompt                         | 3-2  |

|     | 3.2.3 Spacing                                | 3-3  |

|     | 3.2.4 Utility Operators                      | 3-3  |

| 3.3 | NUMBERS AND BASE VALUES                      | 3-3  |

|     | 3.3.1 Hexadecimal, Decimal, Binary and Octal | 3-4  |

|     | 3.3.2 Default Base                           | 3-4  |

|     | 3.3.3 Display Base                           | 3-5  |

| 3.4 | ARITHMETIC OPERATORS                         | 3-6  |

|     | 3.4.1 Assignment Operators                   | 3-7  |

|     | 3.4.2 Two-Argument Operators                 | 3-9  |

|     | 3.4.3 Single-Argument Operators              | 3-12 |

| 3.5 | PARAMETER SET-UP AND EEPROM STORAGE          | 3-13 |

# SECTION 4. OPERATION

|      | INTRODUCTION                                      | 4-2   |

|------|---------------------------------------------------|-------|

| 4.2  | REGISTER OPERATORS                                | 4-2   |

|      | 4.2.1 Loading a Register                          | 4-4   |

|      | 4.2.2 General Registers                           | 4-4   |

| 4.3  |                                                   | 4-4   |

|      | 4.3.1 Run                                         | 4-5   |

|      | 4.3.2 Step and Stop                               | 4-5   |

|      | 4.3.3 Run With Breakpoints                        | 4-5   |

|      | 4.3.4 Vector Loading and Running With Vectors     | 4-6   |

|      | 4.3.5 Reset                                       | 4-6   |

|      | 4.3.6 Wait                                        | 4-6   |

| 4.4  | MEMORY MODE                                       | 4-6   |

|      | 4.4.1 Entering and Exiting Memory                 | 4-7   |

|      | 4.4.2 Memory Mode and Pointers                    | 4-7   |

|      | 4.4.3 Scrolling                                   | 4-8   |

|      | 4.4.4 Word and Byte                               | 4-8   |

|      | 4.4.5 Examining and Changing Values               | 4-8   |

|      | 4.4.6 Memory Mode Status                          | 4-9   |

|      | 4.4.7 Displaying a Block of Memory and            | 4-9   |

|      | Finding a Memory Pattern                          |       |

| 4.5  | MEMORY MAPPING AND THE OVERLAY MEMORY             | 4-10  |

|      | 4.5.1 Memory Block Attributes                     | 4-10  |

|      | 4.5.2 Memory Mapping Operators                    | 4-11  |

|      | 4.5.3 Overlay Memory Operators                    | 4-12  |

| 4.6  | SOFTWARE DEBUGGING WITHOUT TARGET SYSTEM HARDWARE | 4-14  |

| 4.7  | ERROR HANDLING AND CODES                          | 4-15  |

| 4.8  | THE TRACE MEMORY AND DISASSEMBLER                 | 4-15  |

|      | 4.8.1 Display Raw Trace                           | 4-15  |

|      | 4.8.2 Disassemble Trace                           | 4-16  |

|      | 4.8.3 Disassemble Previous and Following Trace    | 4-17  |

| 4.9  | THE MEMORY DISASSEMBLER                           | 4-22  |

|      | 4.9.1 Disassembled Memory                         | 4-22  |

| 4.10 | THE LINE ASSEMBLER                                | 4-22  |

|      | 4.10.1 Standard Mnemonics                         | 4-23  |

|      | 4.10.2 Assembler Directives                       | 4-2*3 |

|      | 4.10.3 Usage Notes                                | 4-25  |

|      | 4.10.4 Assemble Line to Memory                    | 4-25  |

| 4.11 | REPEAT AND MACROS                                 | 4-31  |

# SECTION 5. PROGRAMMING THE EVENT MONITOR SYSTEM

| 5.1 | INTRODUCTION                                     | 5-2  |

|-----|--------------------------------------------------|------|

| 5.2 | DISPLAYING AND CLEARING THE EVENT MONITOR SYSTEM | 5-4  |

| 5.3 | EVENT COMPARATORS                                | 5-4  |

|     | 5.3.1 Address Comparators                        | 5-5  |

|     | 5.3.2 Count Limit                                | 5-6  |

|     | 5.3.3 Data Comparators                           | 5-7  |

|     | 5.3.4 Status Comparators                         | 5-7  |

|     | 5.3.5 Don't Cares                                | 5-11 |

| 5.4 | EVENT MONITOR SYSTEM ACTIONS                     | 5-12 |

|     | 5.4.1 Force Special Interrupt                    | 5-14 |

| 5.5 | EVENT GROUPS                                     | 5-16 |

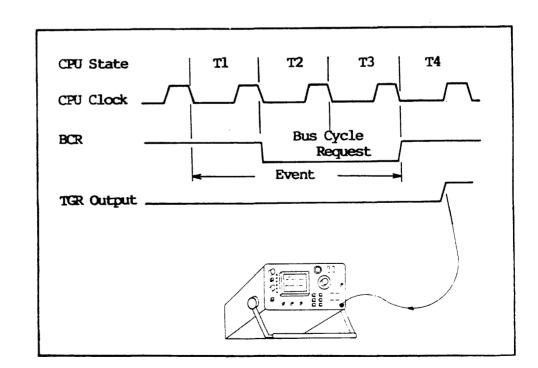

| 5.6 | OPTIONAL LOGIC STATE ANALYZER                    | 5-21 |

|     | 5.6.1 LSA Functions                              | 5-21 |

|     | 5.6.2 Timing Strobe                              | 5-22 |

|     |                                                  |      |

iii

4

# SECTION 6. INTERFACING AND COMMUNICATIONS

| 6.1 | INTRODUCTION                   | 6-2 |

|-----|--------------------------------|-----|

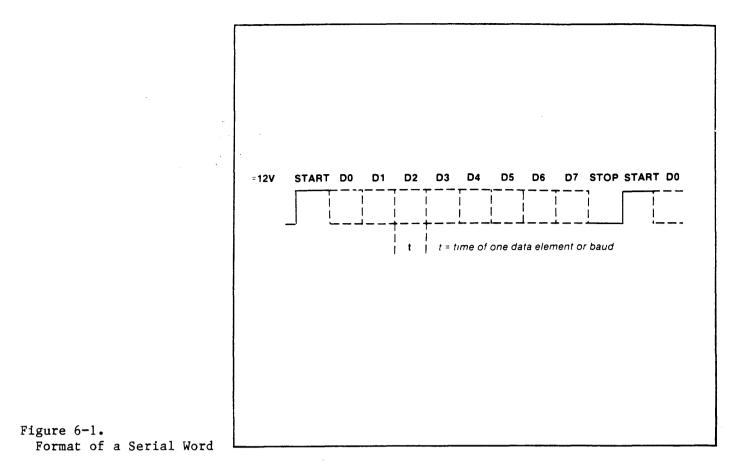

| 6.2 | SERIAL DATA REQUIREMENTS       | 6-2 |

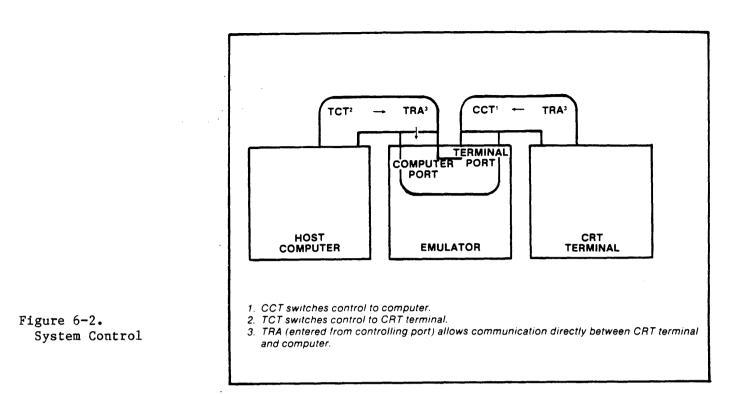

| 6.3 | SETTING SYSTEM CONTROL         | 6-3 |

|     | 6.3.1 Terminal Control         | 6-3 |

|     | 6.3.2 Computer Control         | 6-3 |

|     | 6.3.3 Transparent Mode         | 6-4 |

| 6.4 | DATA TRANSFER AND MANIPULATION | 6-5 |

|     | 6.4.1 Upload and Download      | 6-5 |

|     | 6.4.2 Verify                   | 6-7 |

# SECTION 7. DIAGNOSTIC FUNCTIONS

| 7.1 | INTRODUCTION                                                | 7-2 |

|-----|-------------------------------------------------------------|-----|

| 7.2 | RAM DIAGNOSTICS                                             | 7-2 |

|     | 7.2.1 SF #0, <range></range>                                | 7-2 |

|     | 7.2.2 SF #1, <range></range>                                | 7-2 |

|     | 7.2.3 SF #2, <range></range>                                | 7-2 |

|     | 7.2.4 SF #3, <range></range>                                | 7-2 |

| 7.3 | SCOPE LOOPS                                                 | 7-2 |

|     | 7.3.1 SF #4, <addr><data></data></addr>                     | 7-3 |

|     | 7.3.2 SF #5, <addr></addr>                                  | 7-3 |

|     | 7.3.3 SF #6, <addr> <data></data></addr>                    | 7-3 |

|     | 7.3.4 SF #7, <addr>, <pat-1> <pat-2></pat-2></pat-1></addr> | 7-3 |

|     | 7.3.5 SF #8, <addr>, <pat></pat></addr>                     | 7-3 |

|     | 7.3.6 SF #9, <addr>, <data></data></addr>                   | 7-3 |

|     | 7.3.7 SF #10, <range></range>                               | 7-3 |

|     | 7.3.8 SF #11, <addr>, <data></data></addr>                  | 7-3 |

|     | 7.3.9 SF #12, <range></range>                               | 7-3 |

| 7.4 | MISCELLANEOUS                                               | 7-3 |

| 7.5 | BUS                                                         | 7-4 |

| 7.6 | COM AND DIA                                                 | 7-5 |

## SECTION 8. MAINTENANCE AND TROUBLESHOOTING

| 8.1 | MAINTENANCE              | 8-2 |

|-----|--------------------------|-----|

|     | 8.1.1 Cables             | 8-2 |

|     | 8.1.2 Probe Tip Assembly | 8-2 |

| 8.2 | TROUBLESHOOTING          | 8-2 |

| 8.3 | PARTS LIST               | 8-4 |

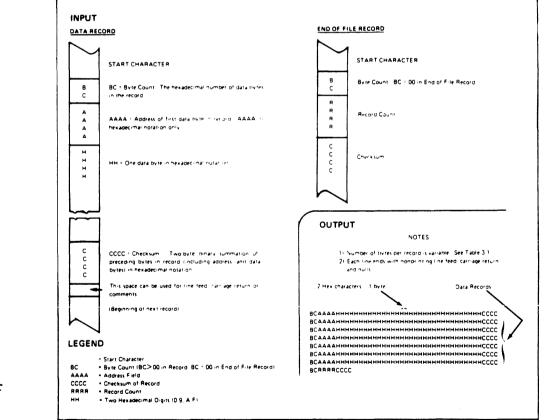

# APPENDIX A. SERIAL DATA FORMATS

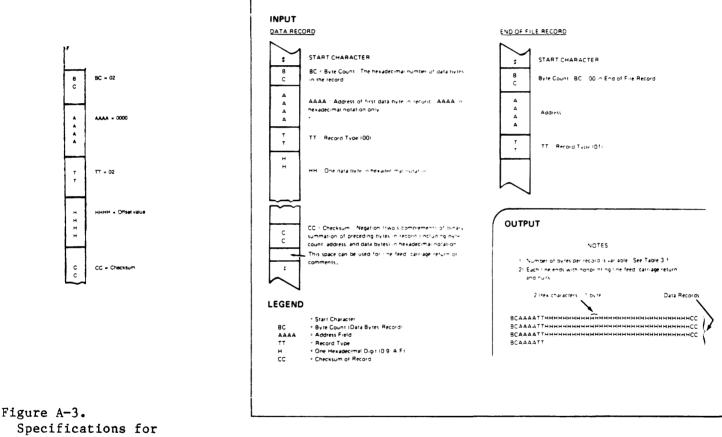

| A.1 | MOS TECHNOLOGY FORMAT             | A-2 |

|-----|-----------------------------------|-----|

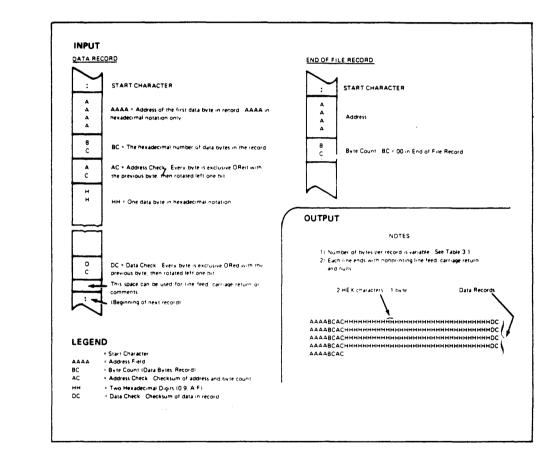

| A.2 | MOTOROLA EXORCISER FORMAT         | A-3 |

| A.3 | INTEL INTELLEC 8/MDS FORMAT       | A-4 |

| A.4 | SIGNETICS ABSOLUTE OBJECT FORMAT  | A-5 |

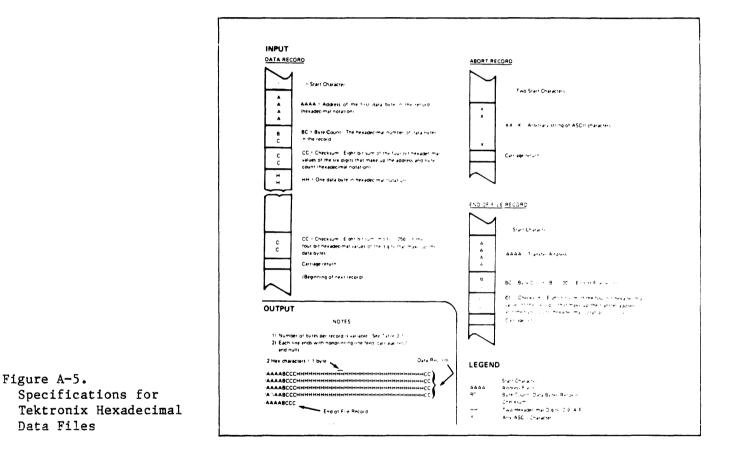

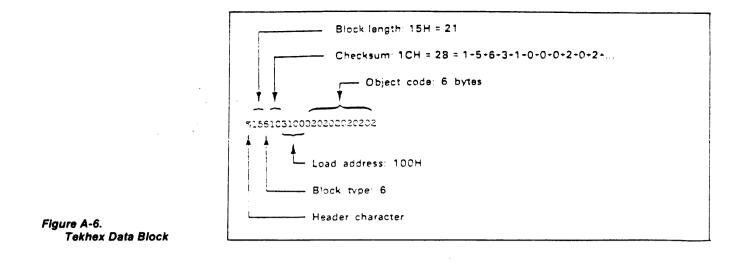

| A.5 | TEKTRONIX HEXADECIMAL FORMAT      | A-6 |

| A.6 | EXTENDED TEKHEX FORMAT            | A-7 |

|     | A.6.1 Variable-Length Fields      | A-8 |

|     | A.6.2 Data and Termination Blocks | A-8 |

|     | A.6.3 Symbol Blocks               | A-9 |

| APPENDIX B. GLOSSARY AND REFERENCE MATERIAL                                                  | B-1               |

|----------------------------------------------------------------------------------------------|-------------------|

| B.1 Glossary B.2 Reference Material                                                          | B-1<br>B-3        |

| APPENDIX C. SYMBOLIC DEBUG                                                                   | C-1               |

| C.1 COMMANDS<br>C.2 USAGE NOTE FOR USERS WITH SYMBOLIC FORMATS<br>OTHER THAN EXTENDED TEKHEX | C-2<br>C-5        |

| APPENDIX D. S-RECORD OUTPUT FORMAT                                                           |                   |

| D.1 S-RECORD OUTPUT FORMAT<br>D.1.1 S-Record Content<br>D.1.2 S-Record Types                 | D-2<br>D-2<br>D-2 |

| D.2 CREATION OF S-RECORDS                                                                    | D-3               |

# INDEX TO TOPICS I-1

# QUICK INDEX TO OPERATORS

| OPERATOR              | NAME                                                                | PAGE        | SECTION<br>NUMBER |

|-----------------------|---------------------------------------------------------------------|-------------|-------------------|

| ABS                   | absolute value                                                      | 3-12        | 3.4.2             |

| AC1, AC2              | address comparators 1 and 2                                         | 5-4         | 5.3.1             |

| ALT                   | alternate data access                                               | 5-8         | 5.3.4             |

| AND                   | logical event AND                                                   | 5-13        | 5.6               |

| AX, AL, AH            | accumulator (low and high)                                          | 4-2         | 4.2               |

| BAS<br>BKX            | display base value<br>break on instruction execution (not prefetch) | 3-4         | 3.3.3             |

| BMO                   | block move                                                          | 4-12        | 4.5.3             |

| BP                    | base pointer                                                        | 4-2         | 4.2               |

| BRK                   | break                                                               | 5-10        | 5.4               |

| BUS                   | display status of lines                                             | 7-4         | 7.5               |

| BX, BL, BH            | base register (low and high)                                        | 4-2         | 4.2               |

| BYM                   | byte mode                                                           | 4-6         | 4.4.4             |

| BYT                   | byte status                                                         | 5-11        | 5.5.5             |

| CCT                   | Computer Control                                                    | 6-3         | 6.3.2             |

| CD                    | overlay enable for code access                                      | 4-11        | 4.5.3             |

| CES                   | clear Event Monitor System When/Then statements                     | 5-3         | 5.2               |

| СК                    | select internal clock                                               | 3-13        | 3.5               |

| CLK                   | measure target system clock                                         | 7-3         | 7.4               |

| CLM                   | clear memory map                                                    | 4-10        | 4.5.2             |

| CNT                   | count event                                                         | 5-10        | 5.4               |

| CPY                   | copy switch                                                         | 3-15        | 3.5               |

| CRC                   | calculate cyclic redundancy check in target system                  | 7-3         | 7.4               |

| CS                    | code segment                                                        | 4-2         | 4.2               |

| COD                   | code status                                                         | 5-8         | 5.3.4             |

| COM                   | communicate with program running in system                          | 7-5         | 7.6               |

| CTL                   | count limit                                                         | , J<br>5-9  | 5.5.2             |

| CWØ, CW1              | dma control words $\emptyset$ and 1                                 | 4-2         | 4.2               |

|                       |                                                                     |             |                   |

| CX, CL, CH            | count register (low and high)                                       | 4-2         | 4.2               |

| DAT                   | data access status                                                  | 4.8         | 4.4.6             |

| DB                    | display memory block                                                | 4-8         | 4.4.7             |

| DC                    | Don't Care                                                          | 5-9         | 5.3.5             |

| DC1,DC2               | data comparators 1 and 2                                            | 5-6         | 5.5.3             |

| DEL                   | delete symbol                                                       | 6-3         | 6.1               |

| DES                   | display Event Monitor System When/Then statements                   | 5-3         | 5.2               |

| DFB                   | default base value                                                  | 3-4         | 3.3.2             |

| DI                    | destination index                                                   | 4-2         | 4.2               |

| DIS                   | display disassembled memory                                         | 4-2         | 4.9.1             |

| DIS                   |                                                                     | 4-21<br>4-9 |                   |

| DM<br>DMA             | display memory map                                                  | 4-9<br>5-8  | 4.5.2<br>5.3.4    |

|                       | DMA cycle status                                                    |             |                   |

| DMAØ, l<br>DMAØ (iRMX | dma interrupt control regisers ( $\emptyset$ .1)                    | 4-3         | 4.2               |

| mode)<br>DMAl (iRMX   | level 2 control register (DMA $\emptyset$ )                         | 4-3         | 4.2               |

| mode)                 | level 3 control register (DMA 1)                                    | 4-3         | 4.2               |

| DME                   | enable DMA timer during pause                                       | 3-14        | 3.5               |

|                       | endere bini ermer durring pudde                                     | 5 14        | J # J             |

| D147                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| DNL                                                                                                                                                                                                                                                      | download                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.4.1                                                                                                                                                  |

| DR                                                                                                                                                                                                                                                       | display CPU registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |

| DRT                                                                                                                                                                                                                                                      | display raw Trace Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.6.1                                                                                                                                                  |

| DS                                                                                                                                                                                                                                                       | data segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |

| DSTØ, 1                                                                                                                                                                                                                                                  | dma lower 16 bits of destination address ( $\emptyset$ , 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |

| DT                                                                                                                                                                                                                                                       | disassemble Trace Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.6.2                                                                                                                                                  |

| DTA                                                                                                                                                                                                                                                      | overlay enable for data access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.5.3                                                                                                                                                  |

| DTB                                                                                                                                                                                                                                                      | disassemble Trace Memory backward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.6.3                                                                                                                                                  |

| DTF                                                                                                                                                                                                                                                      | disassemble Trace Memory forward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.6.3                                                                                                                                                  |

| DX,DL, DH                                                                                                                                                                                                                                                | data register (low and high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |

|                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |

| EDI                                                                                                                                                                                                                                                      | end of interrupt register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |

| EDI (iRMX                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |

| mode)                                                                                                                                                                                                                                                    | specific end of interrupt register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |

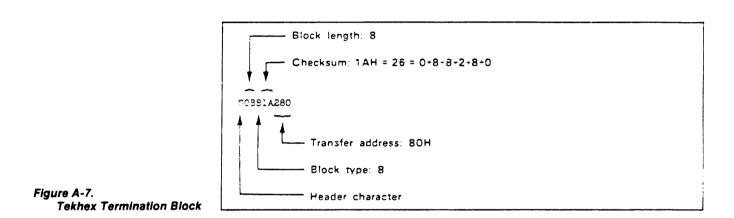

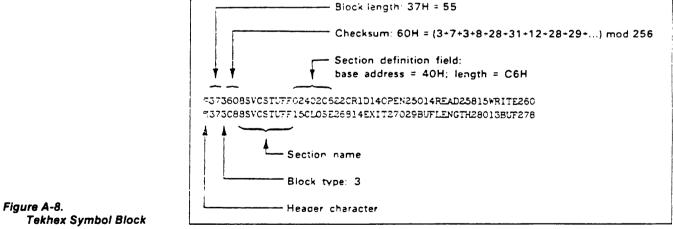

| ES                                                                                                                                                                                                                                                       | extra data segment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2                                                                                                                                                    |