# System MAINTENANCE MANUAL

# TABLE OF CONTENTS

| SECTI | <u>ION</u>                                                                                                                                                                                                                                                | PAGE                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.0   | INTRODUCTION 1.1 PRINCIPLES OF OPERATION 1.2 OPERATIONAL FEATURES 1.3 GENERAL DESCRIPTION 1.4 SELF-TESTS                                                                                                                                                  | 1-1<br>1-1<br>1-3<br>1-5<br>1-8                    |

| 2.0   | CHASSIS, MOTHERBOARDS, AND POWER SUPPLY 2.1 CHASSIS 2.1.1 INTRODUCTION 2.1.2 FUNCIONAL DESCRIPTION 2.1.3 DRAWINGS, DIAGRAMS, & PARTS LIST 2.2 MOTHERBOARDS                                                                                                | 2-1<br>2.1-1<br>2.1-1<br>2.1-1<br>2.1-3<br>2.2-1   |

|       | 2.2.1 INTRODUCTION 2.2.2 FUNCTIONAL DESCRIPTION 2.2.2.1 MICROCOMPUTER MOTHERBOARD 2.2.2.2 FUNCTION MOTHERBOARD                                                                                                                                            | 2.2-1<br>2.2-1<br>2.2-1<br>2.2-2                   |

|       | 2.2.3 SCHEMATICS, BOARD LAYOUTS, & PARTS LISTS 2.3 POWER SUPPLY 2.3.1 INTRODUCTION 2.3.2 FUNCTIONAL DESCRIPTION 2.3.2.1 TEST SETUP 2.3.2.2 HIGH VOLTAGE SECTION 2.3.2.3 CONTROL SECTION 2.3.2.4 OUTPUT SECTION 2.3.3 SCHEMATIC, BOARD LAYOUT, & PART LIST | 2.3-1<br>2.3-1<br>2.3-1<br>2.3-1<br>2.3-3<br>2.3-4 |

| 3.0   | KEYBOARD 3.1 INTRODUCTION 3.2 PHYSICAL DESCRIPTION 3.3 SELF-TEST 3.4 DISASSEMBLY 3.5 FUNCTIONAL DESCRIPTION 3.6 SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                                     | 3-1<br>3-1<br>3-1<br>3-2<br>3-3<br>3-6<br>3-8      |

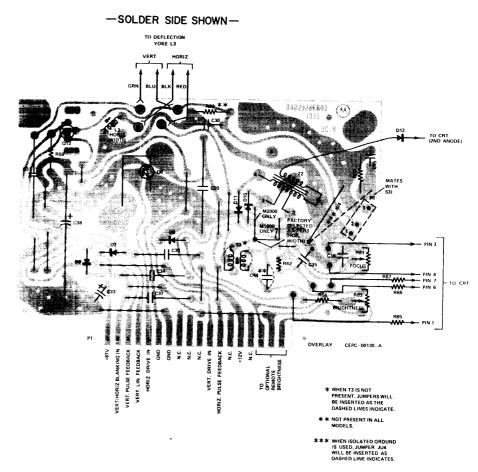

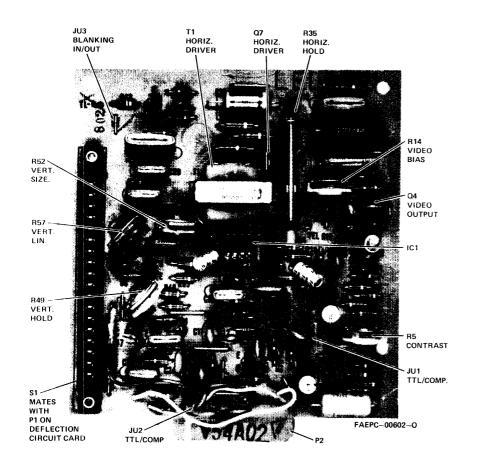

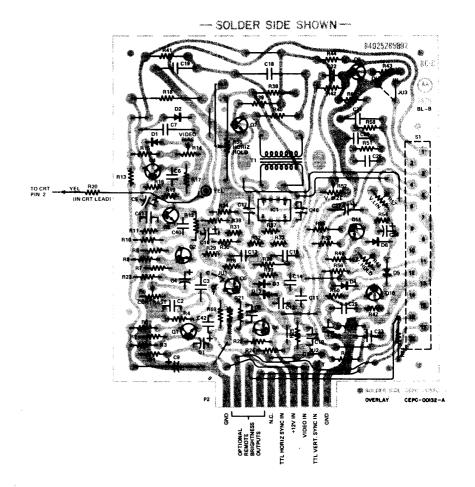

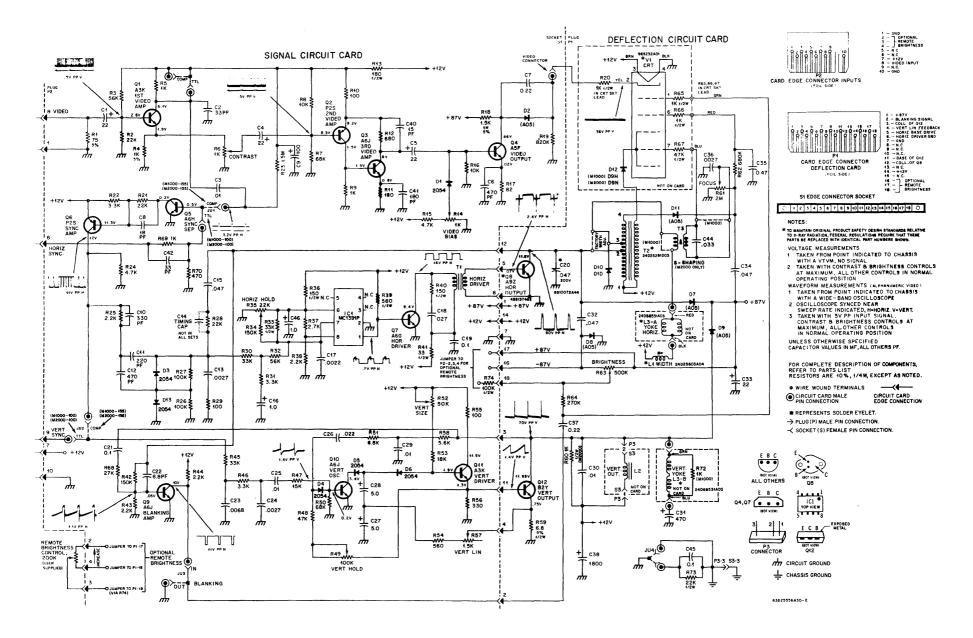

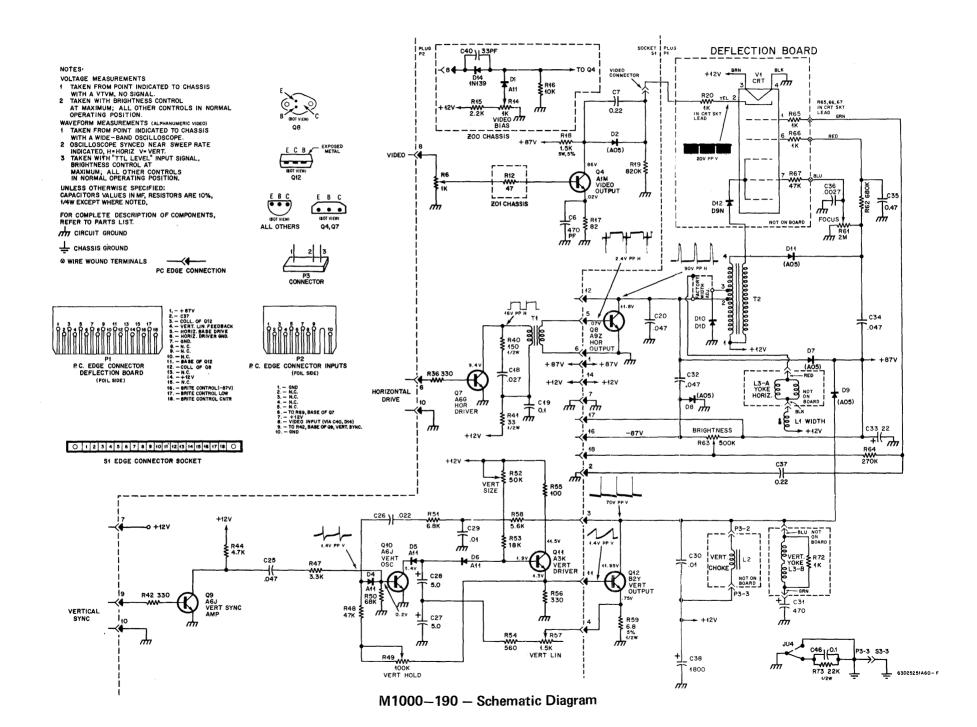

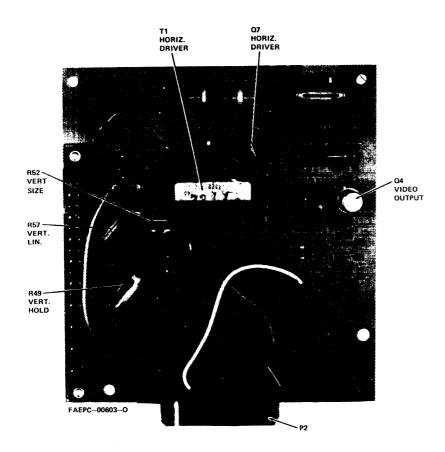

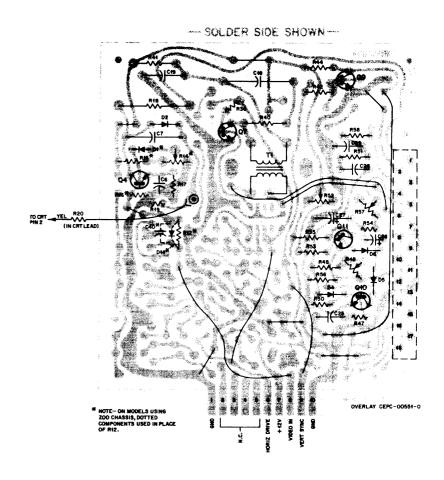

| 4.0   | DISPLAY MODULE 4.1 INTRODUCTION 4.2 FUNCTIONAL DESCRIPTION 4.2.1 AC MAINS FREQUENCY 4.2.2 SELF TEST 4.2.3 CRT ADJUSTMENT PROCEDURE 4.3 SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                              | 4-1<br>4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-4      |

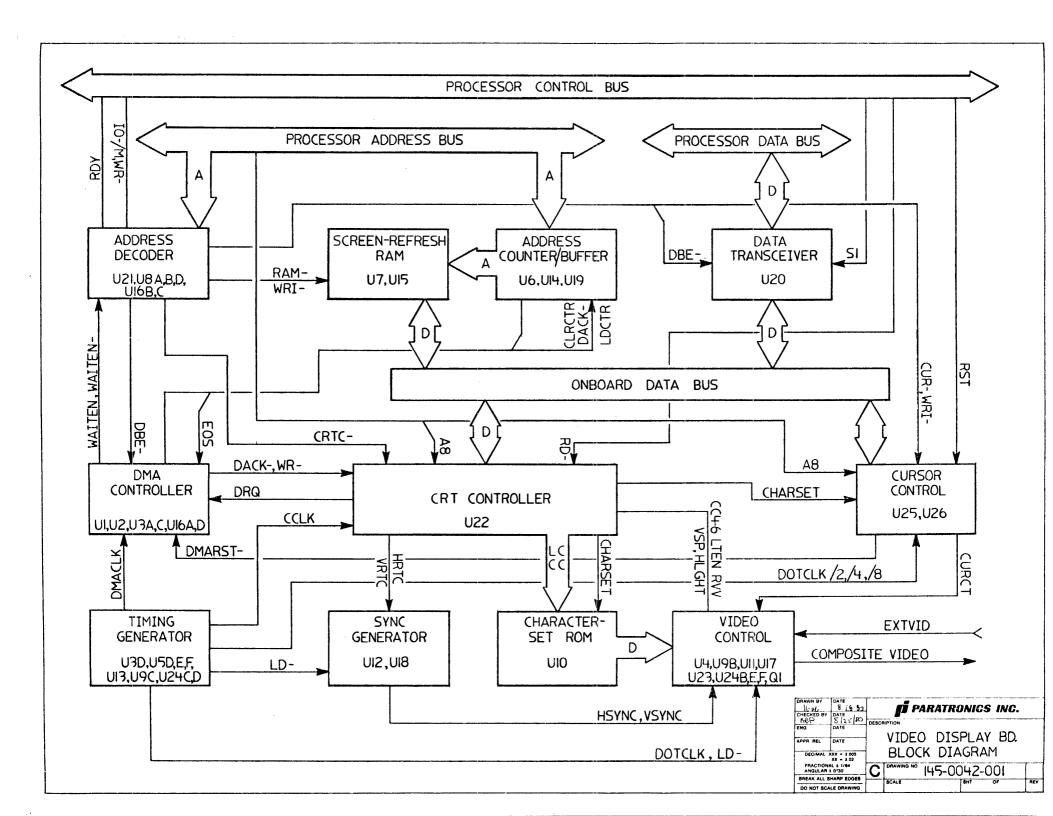

| 5.0   | VIDEO DISPLAY BOARD 5.1 INTRODUCTION 5.2 FUNCTIONAL DESCRIPTION 5.2.1 CRT CONTROLLER 5.2.2 TIMING GENERATOR 5.2.3 DATA TRANSCEIVER 5.2.4 ADDRESS COUNTER 5.2.5 SCREEN-REFRESH RAM                                                                         | 5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3      |

| SECTI | ON                  |                                                                                                                                                                                                                                                                             | PAGE                                                        |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

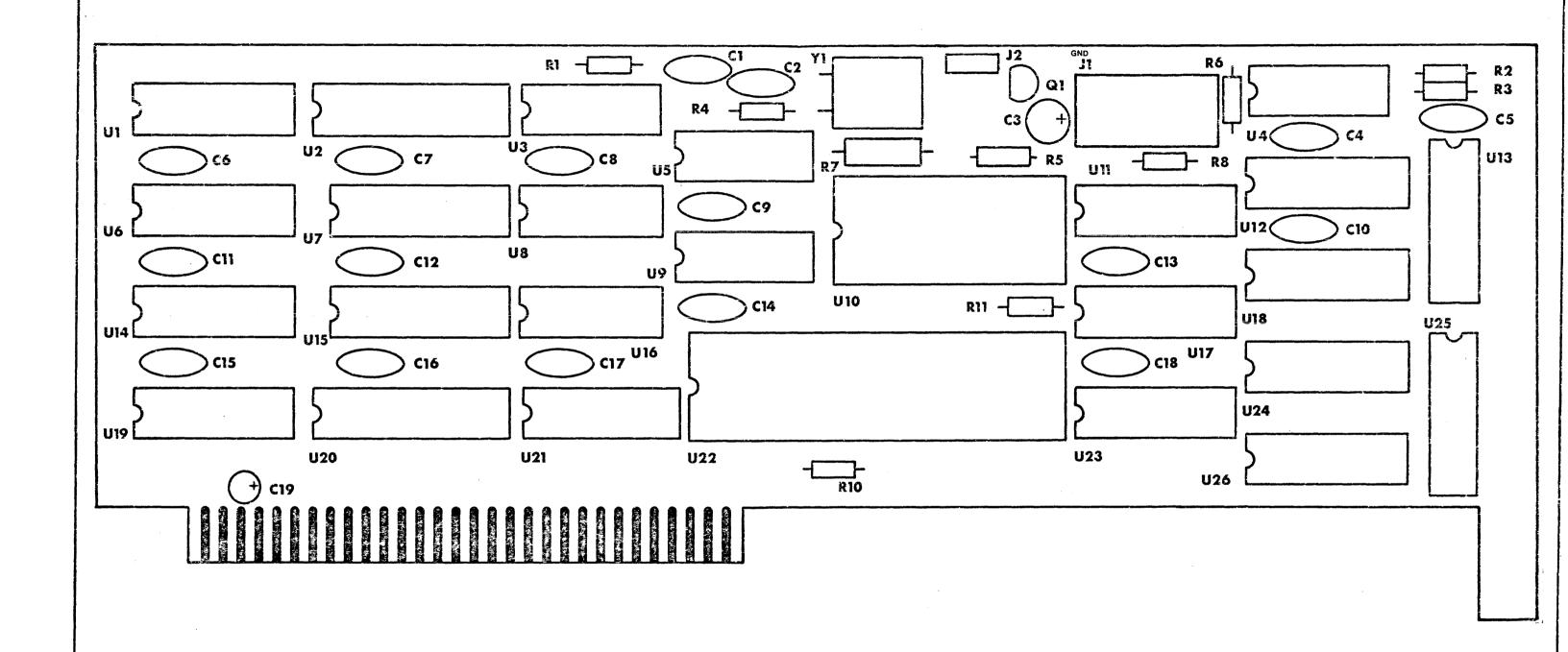

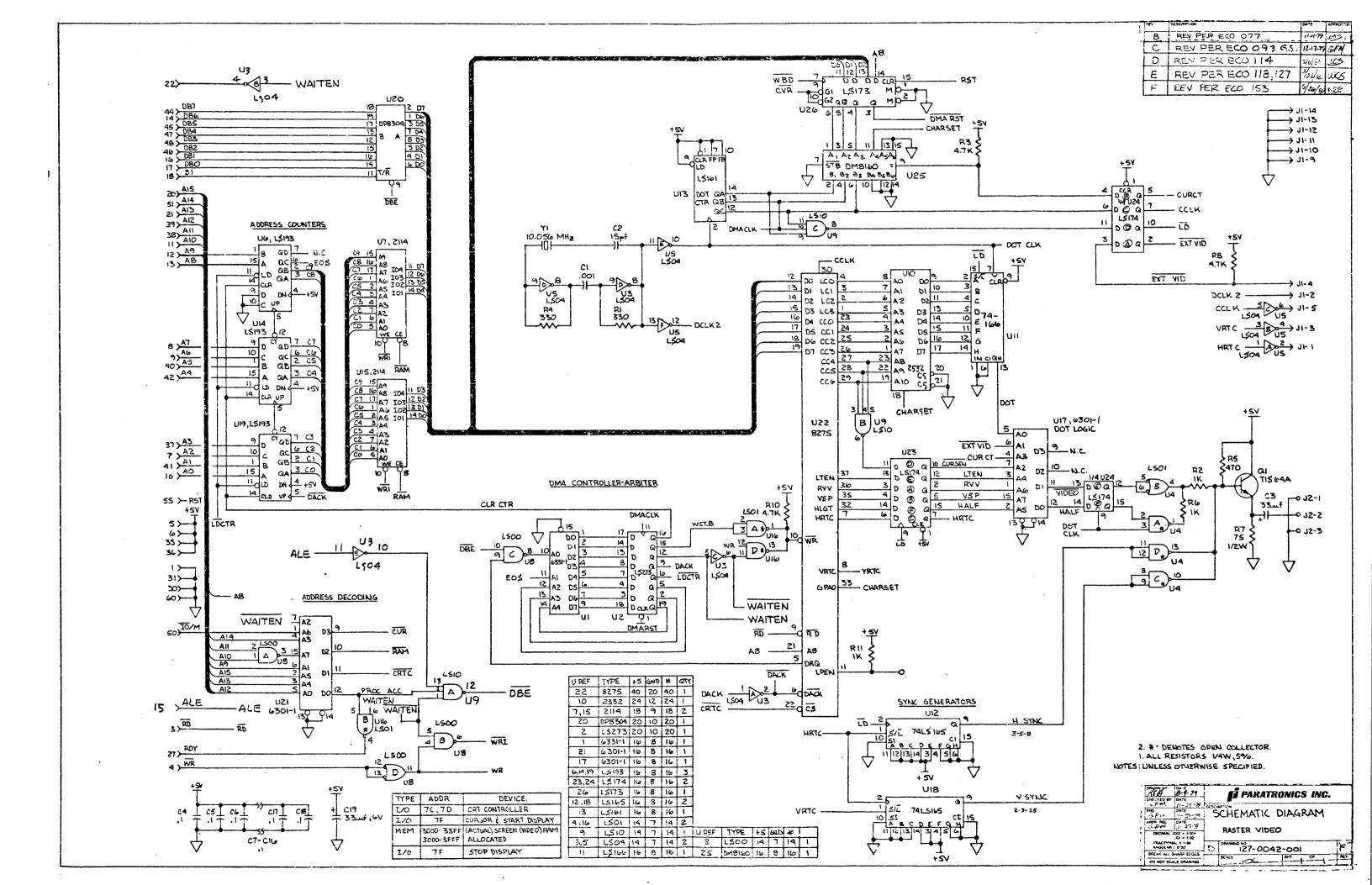

|       |                     | 5.2.6 CHARACTER-SET ROM 5.2.7 VIDEO CONTROL 5.2.8 CURSOR CONTROL 5.2.9 SYNC GENERATOR 5.2.10 ADDRESS DECODER 5.2.11 DMA CONTROLLER SELF-TEST SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                          | 5-4<br>5-4<br>5-5<br>5-6<br>5-6<br>5-7<br>5-8<br>5-8        |

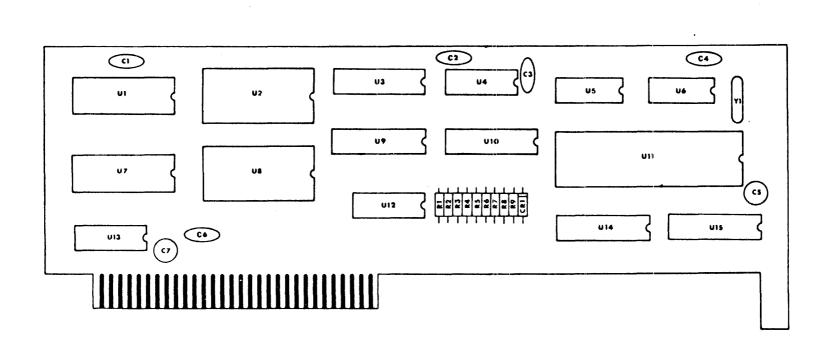

| 6.0   | 6.1<br>6.2          | SSOR BOARD INTRODUCTION FUNCTIONAL DESCRIPTION SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                                                                                                                        | 6-1<br>6-1<br>6-1<br>6-2                                    |

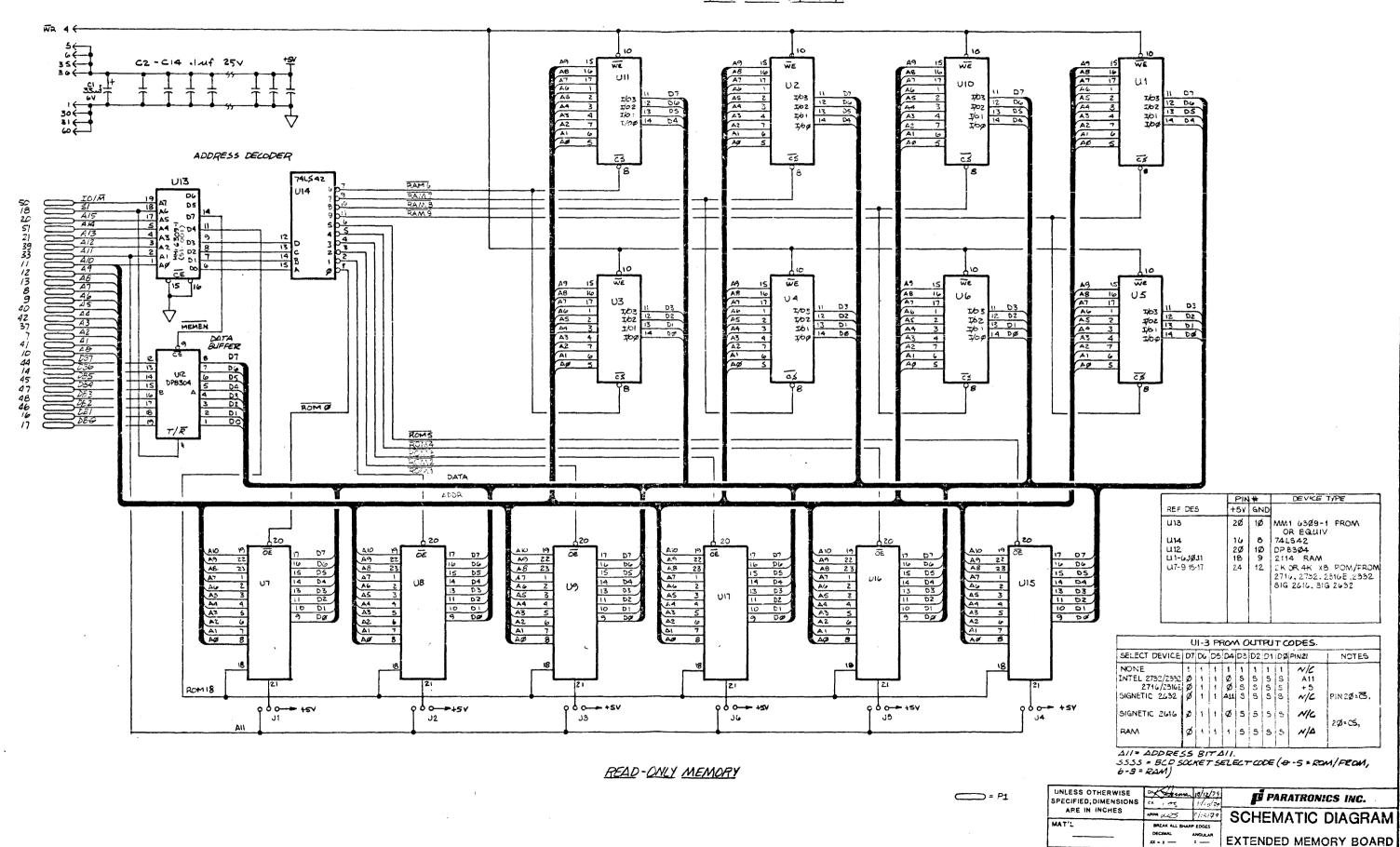

| 7.0   | 7.1<br>7.2          | DED MEMORY BOARDS #1 AND #2 INTRODUCTION FUNCTIONAL DESCRIPTION 7.2.1 DATA BUFFER 7.2.2 READ-ONLY MEMORY 7.2.3 READ/WRITE MEMORY 7.2.4 ADDRESS DECODER SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                | 7-1<br>7-1<br>7-1<br>7-1<br>7-1<br>7-2<br>7-2<br>7-3        |

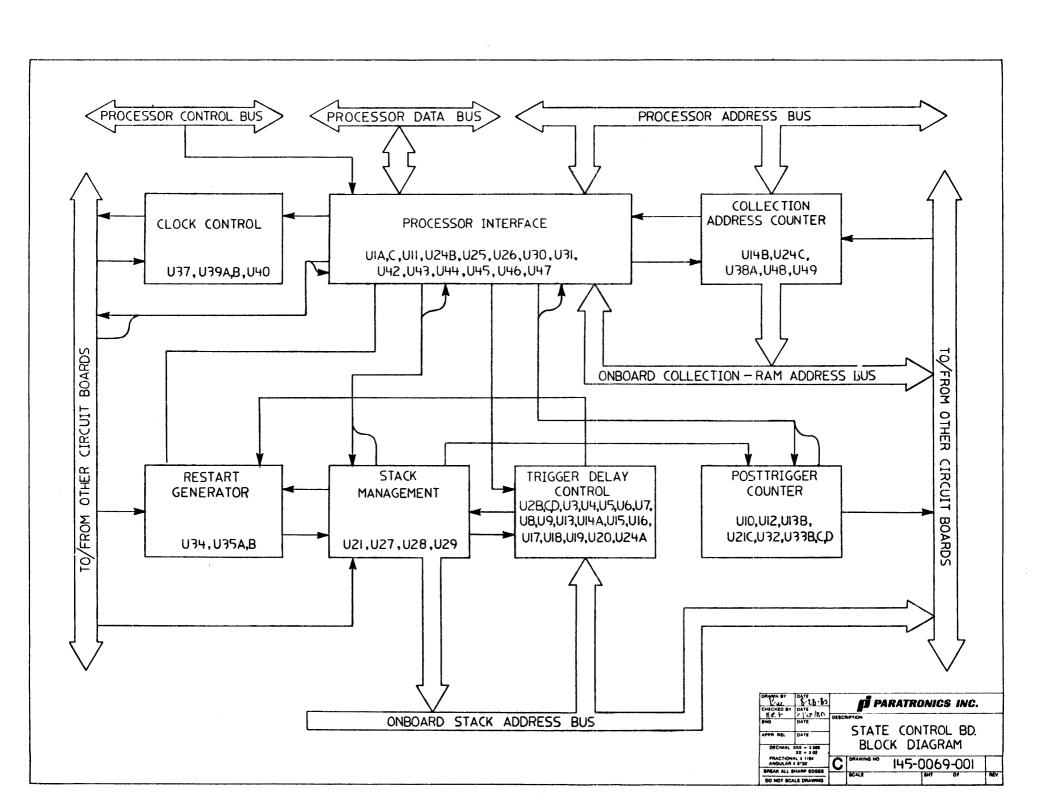

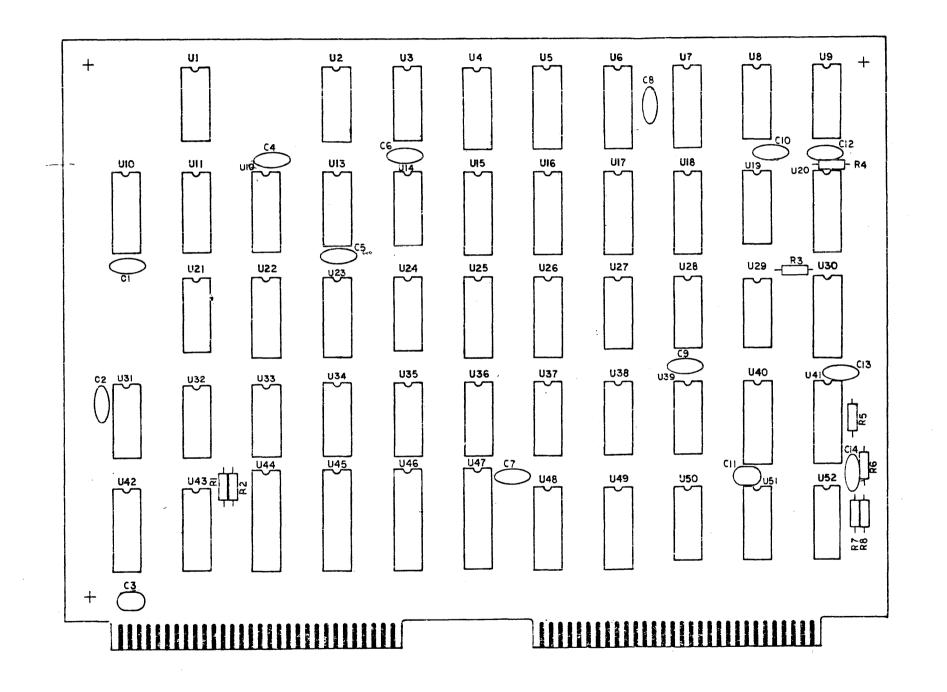

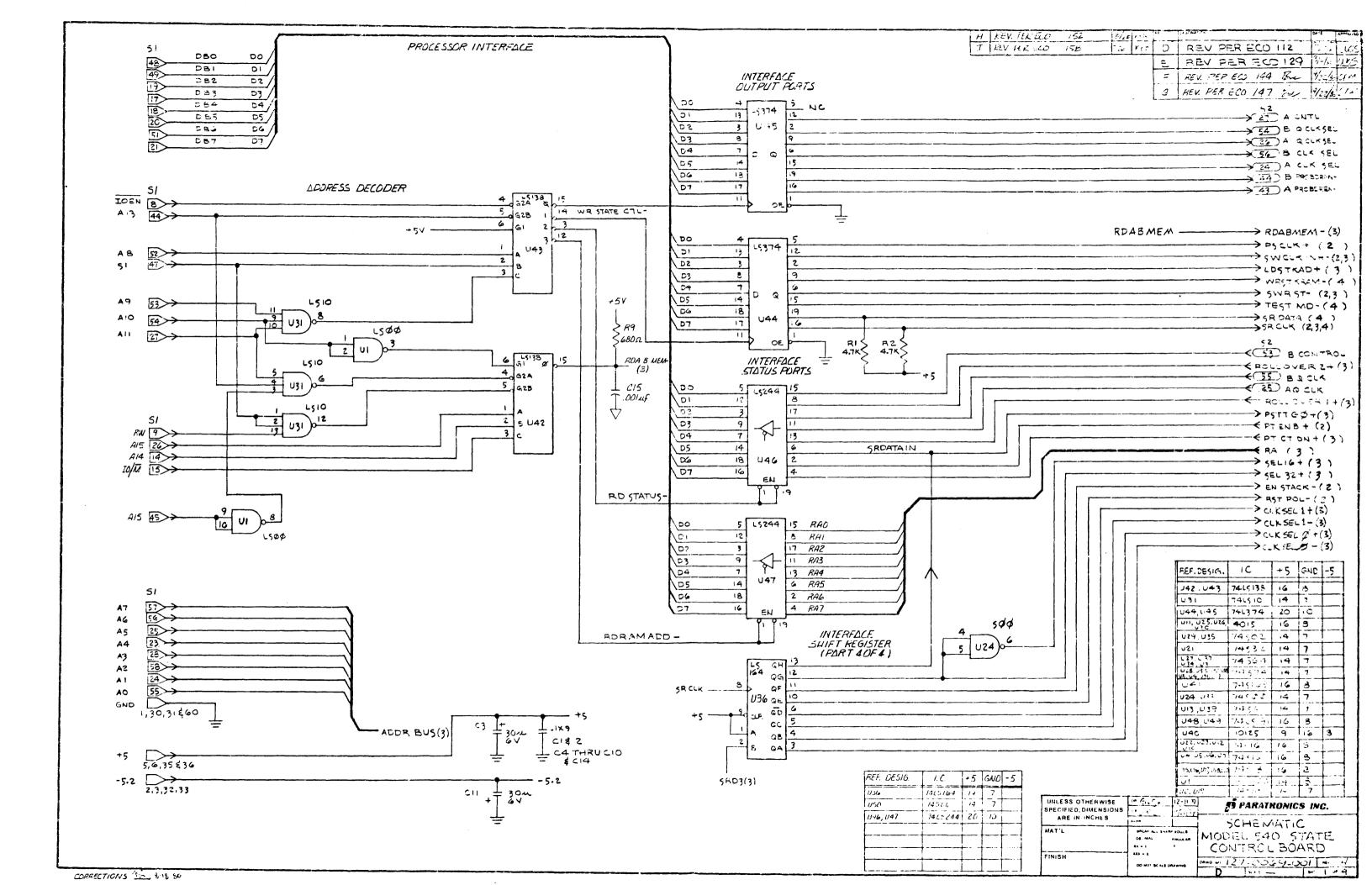

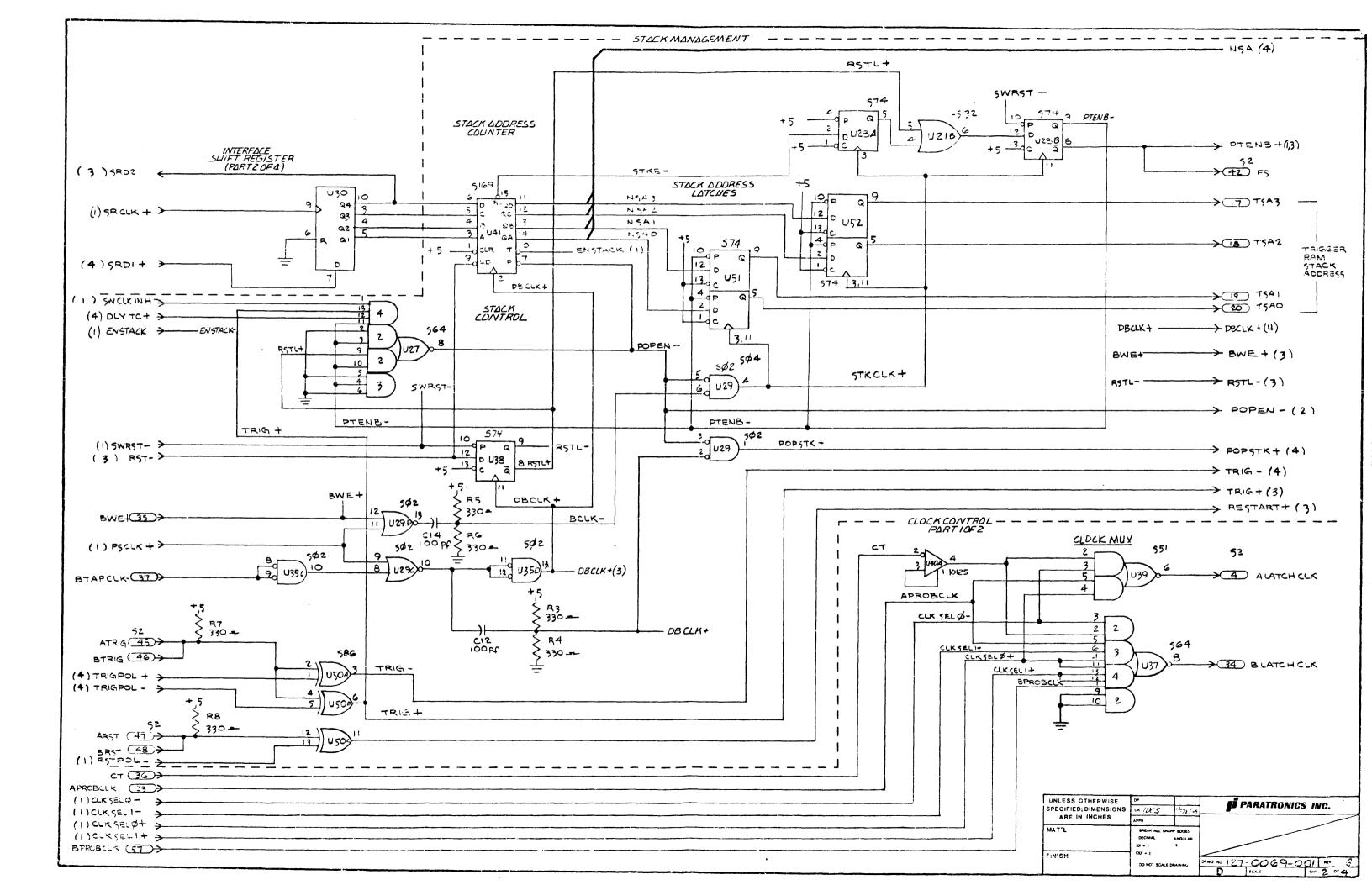

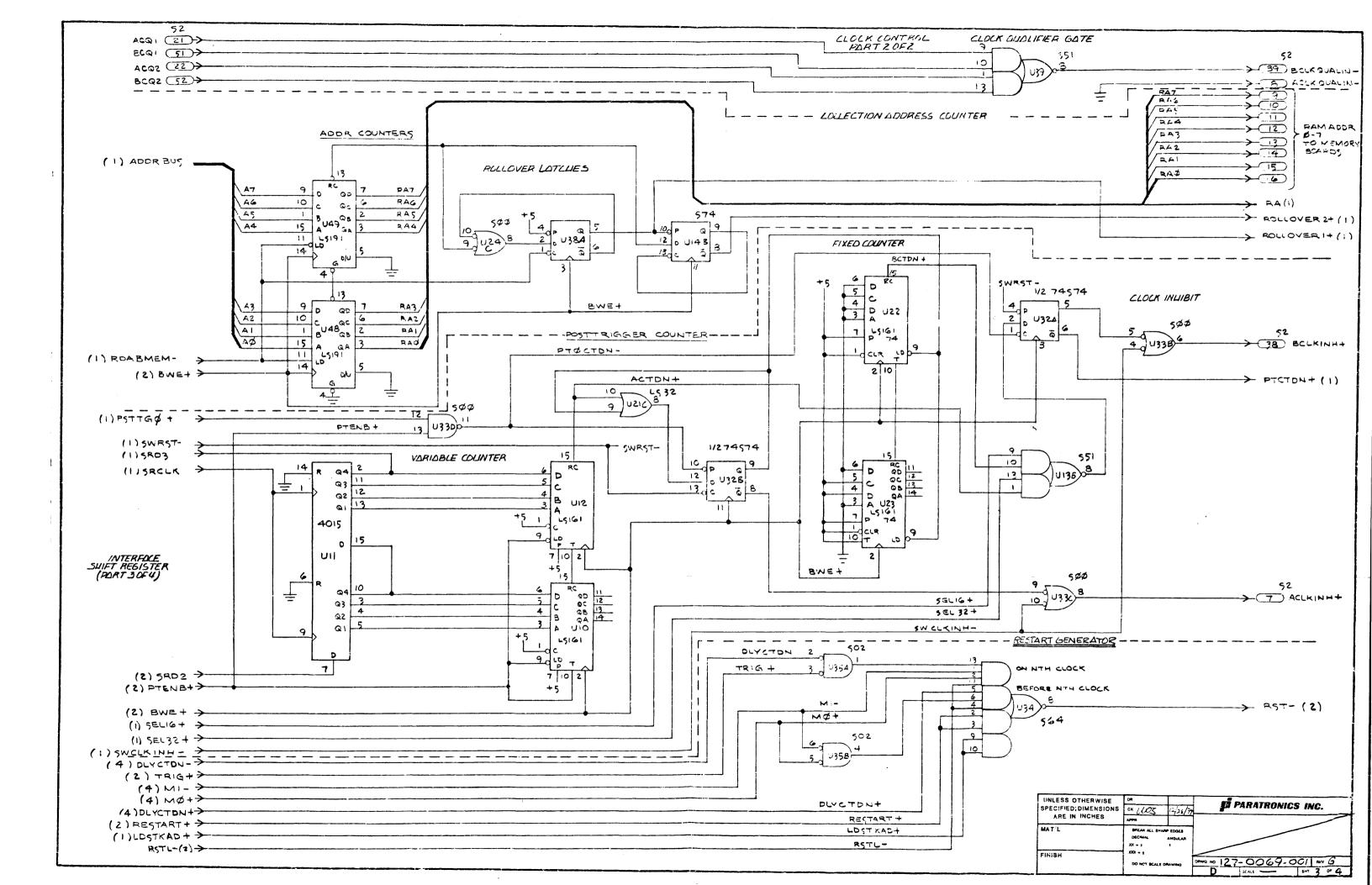

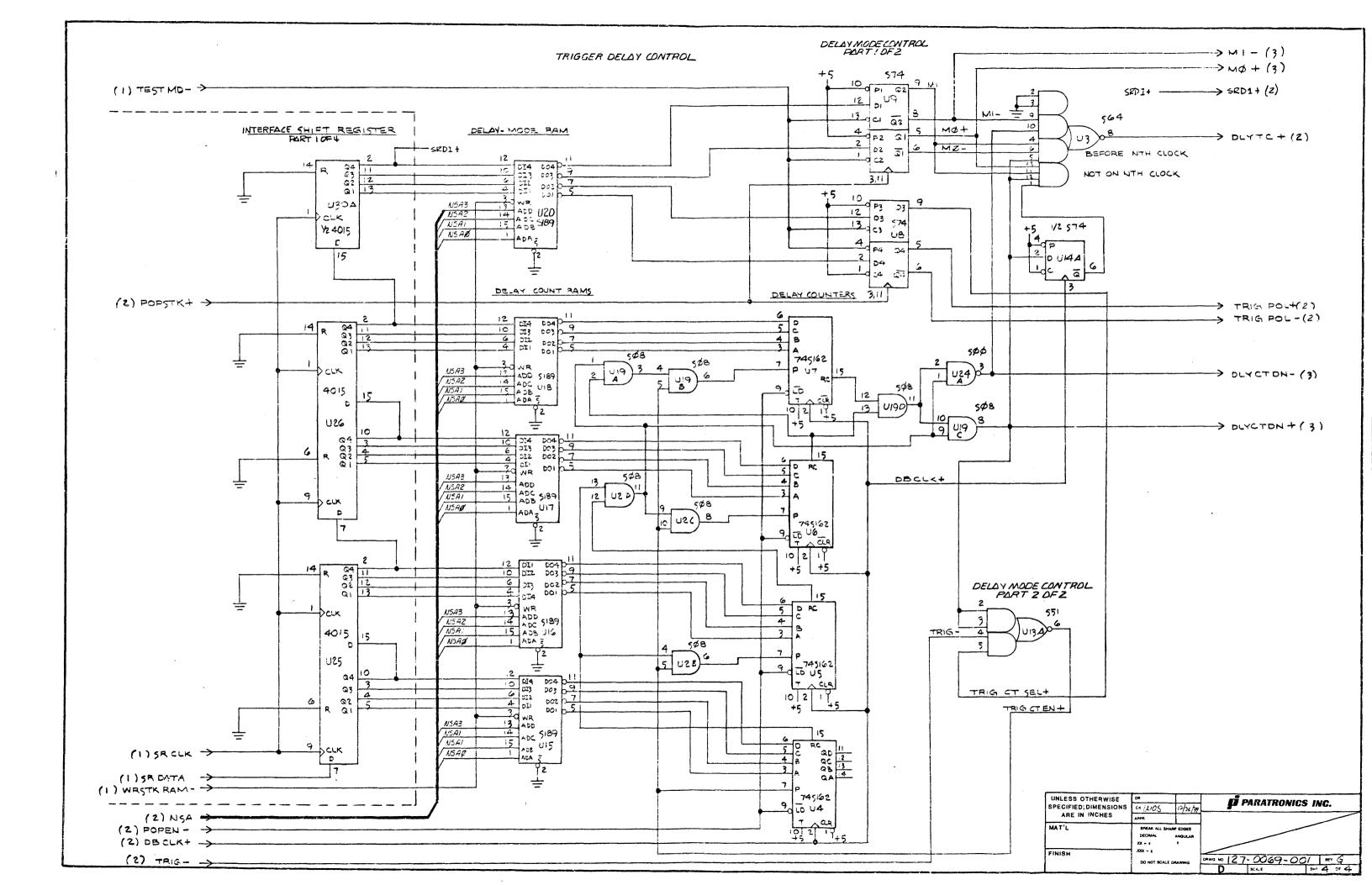

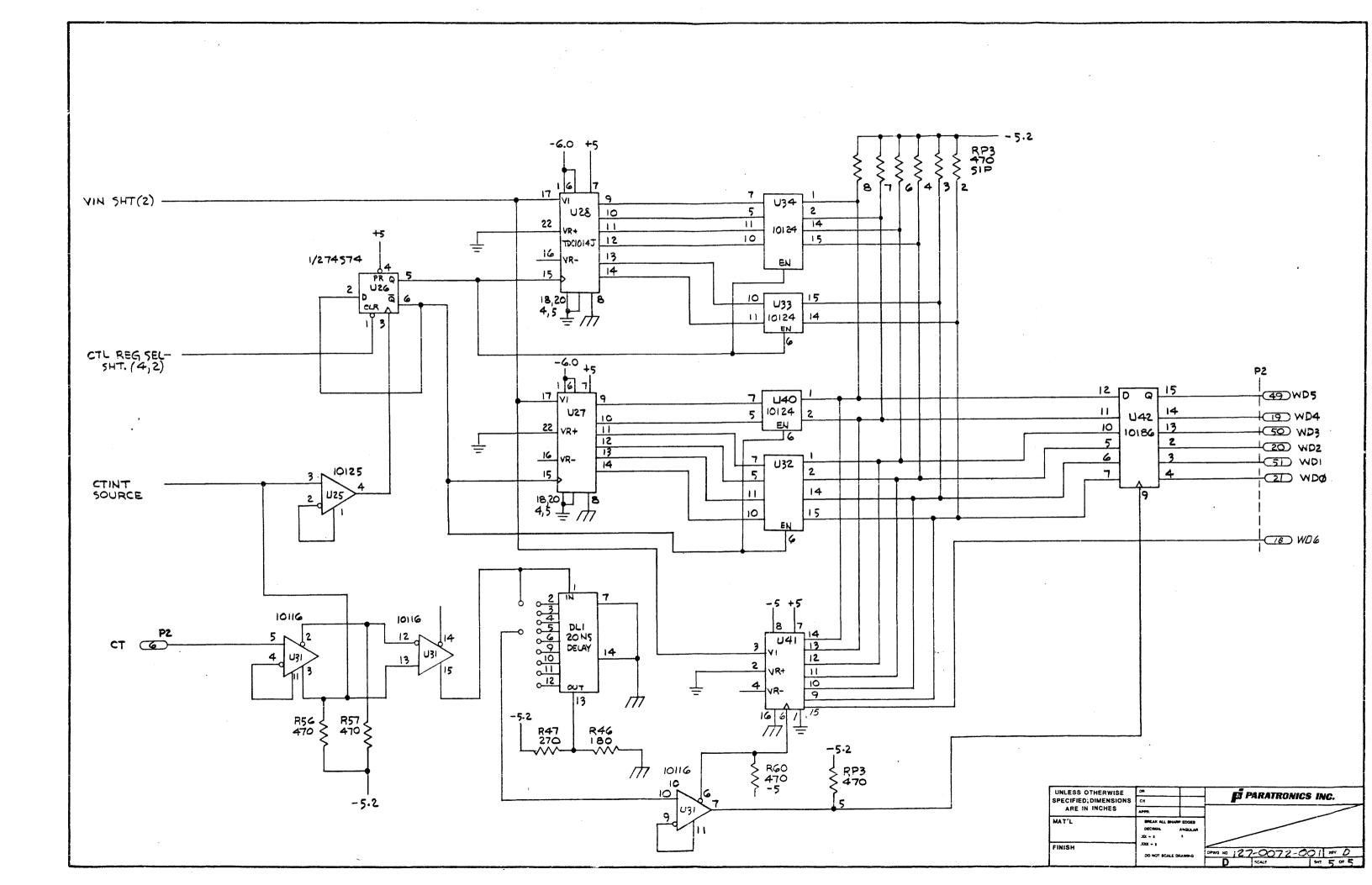

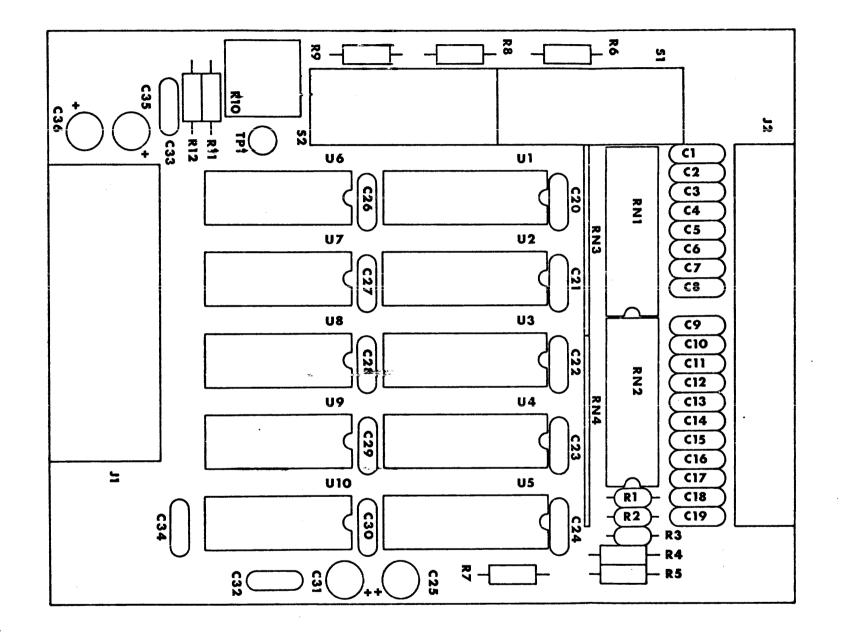

| 8.0   | 8.1<br>8.2          | CONTROL BOARD INTRODUCTION FUNCTIONAL DESCRIPTION 8.2.1 PROCESSOR INTERFACE 8.2.2 STACK MANAGEMENT 8.2.3 CLOCK CONTROL 8.2.4 COLLECTION ADDRESS COUNTER 8.2.5 POSTTRIGGER COUNTER 8.2.6 RESTART GENERATOR 8.2.7 TRIGGER DELAY CONTROL SCHEMATIC, BOARD LAYOUT, & PARTS LIST | 8-1<br>8-1<br>8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7 |

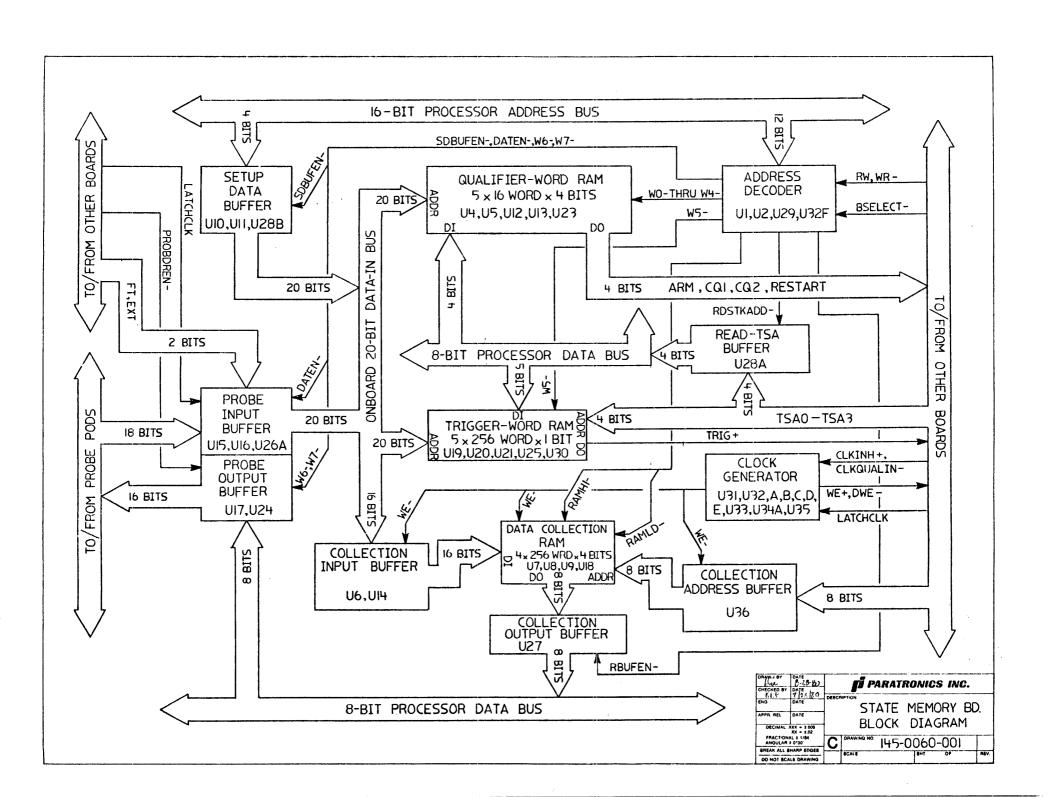

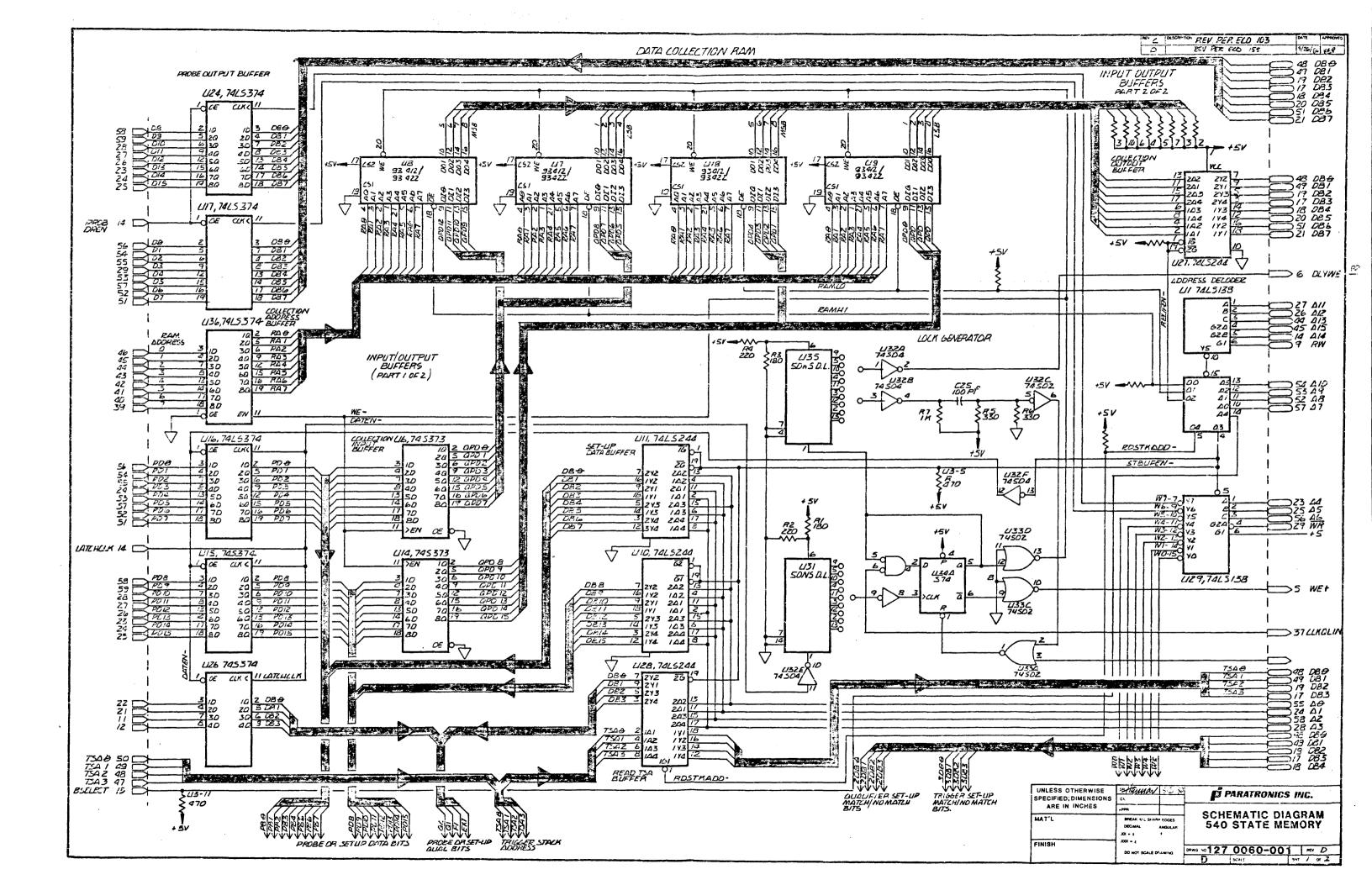

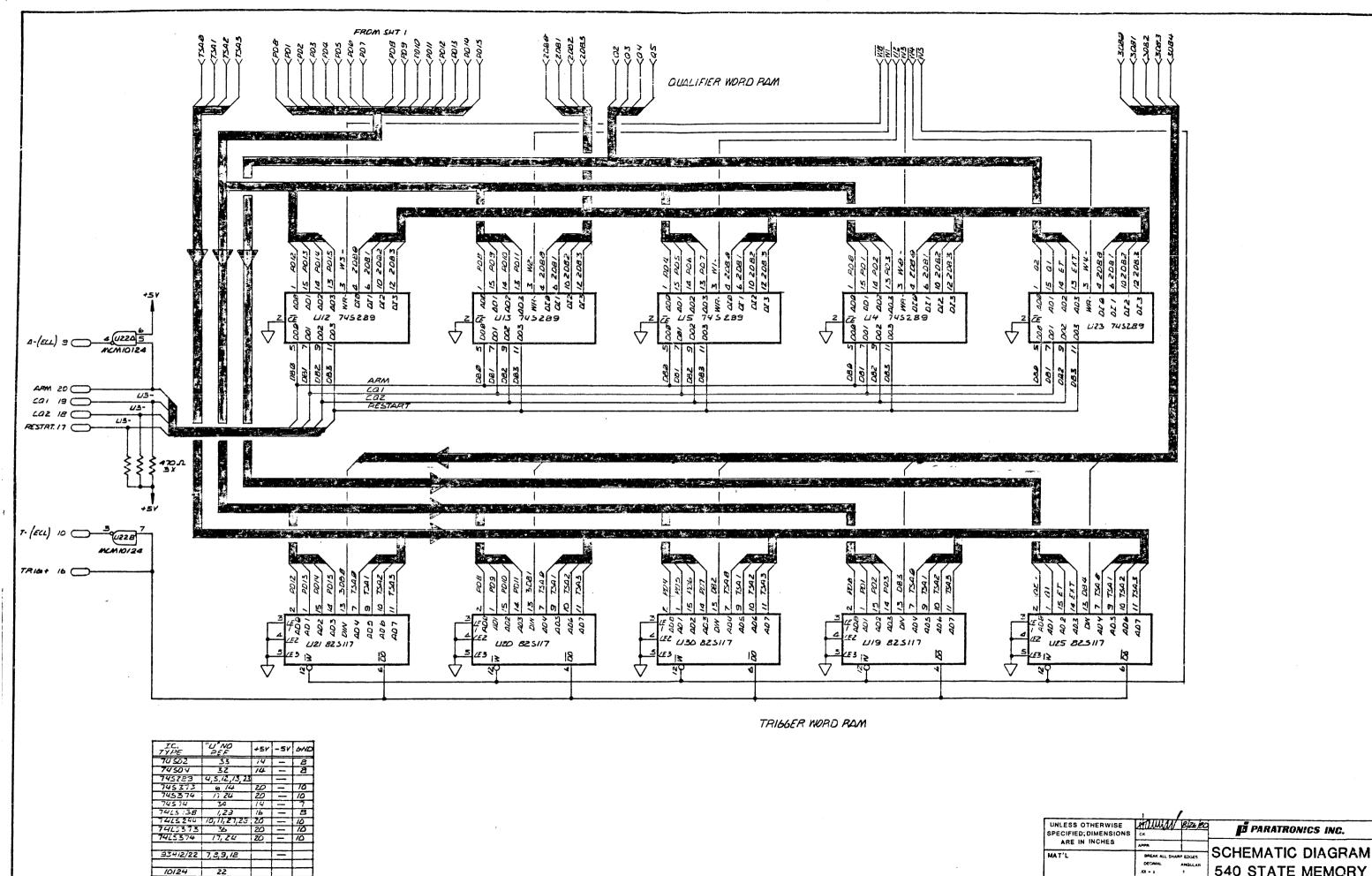

| 9.0   | STATE<br>9.1<br>9.2 | MEMORY BOARD INTRODUCTION FUNCTIONAL DESCRIPTION 9.2.1 INPUT/OUTPUT BUFFERS 9.2.2 QUALIFIER-WORD RAM 9.2.3 TRIGGER-WORD RAM 9.2.4 CLOCK GENERATOR 9.2.5 ADDRESS DECODER 9.2.6 DATA COLLECTION RAM                                                                           | 9-1<br>9-1<br>9-1<br>9-2<br>9-4<br>9-5<br>9-7<br>9-7        |

|       | 9.3                 |                                                                                                                                                                                                                                                                             | 9-9<br>9-9<br>9-10<br>9-11<br>9-11                          |

| SECTI | ON           |                                                                                                                                                                                                                                                                                                         | PAGE                                                                                                                         |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

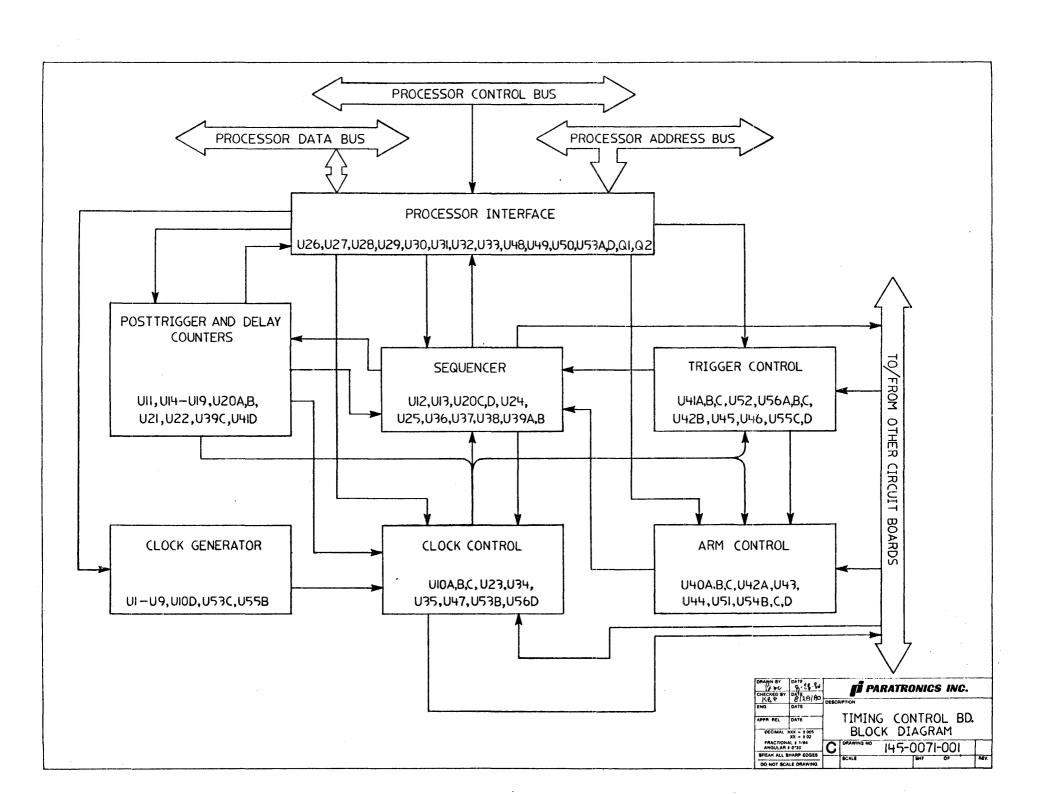

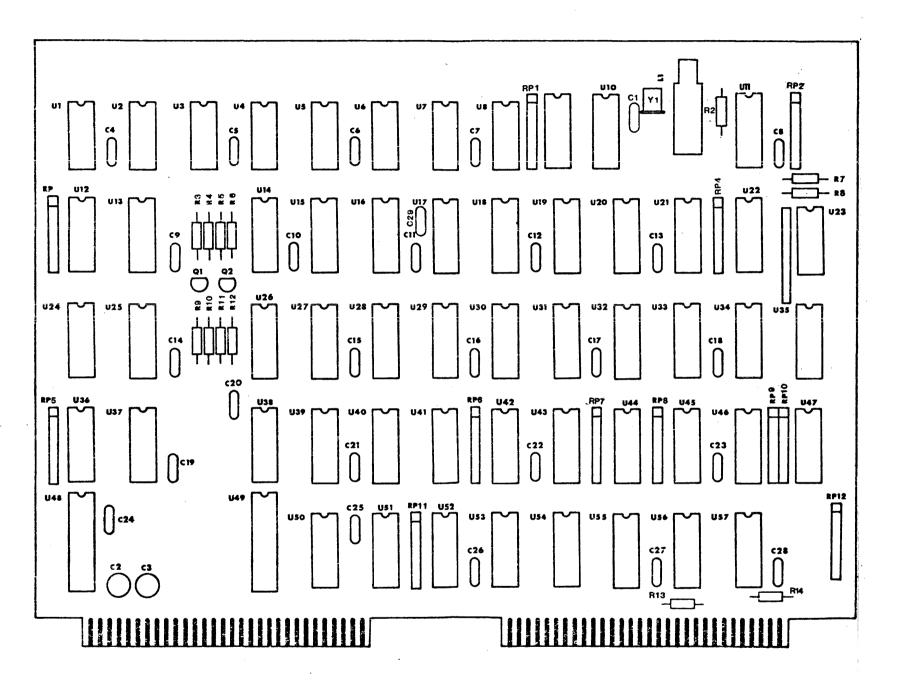

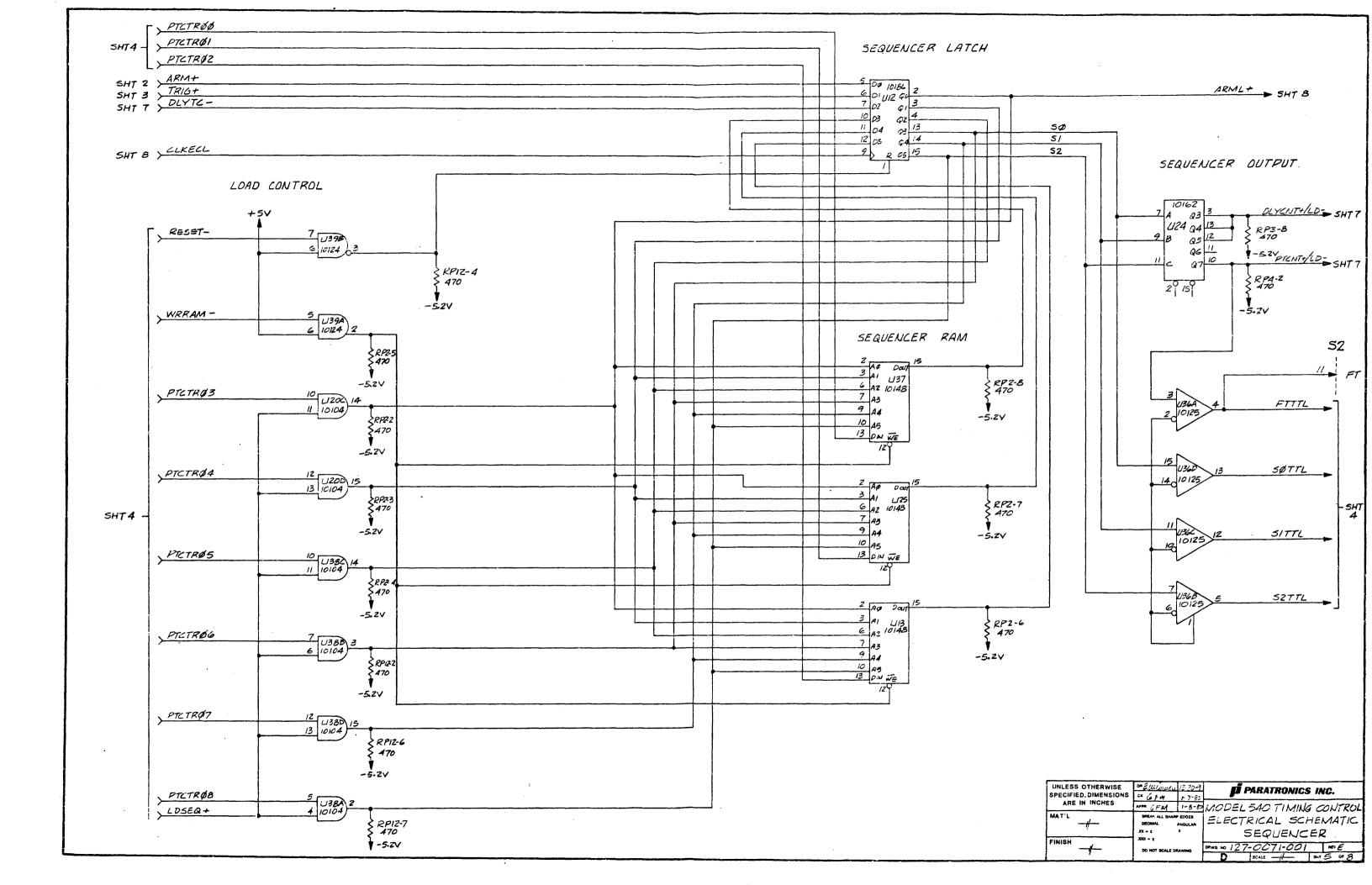

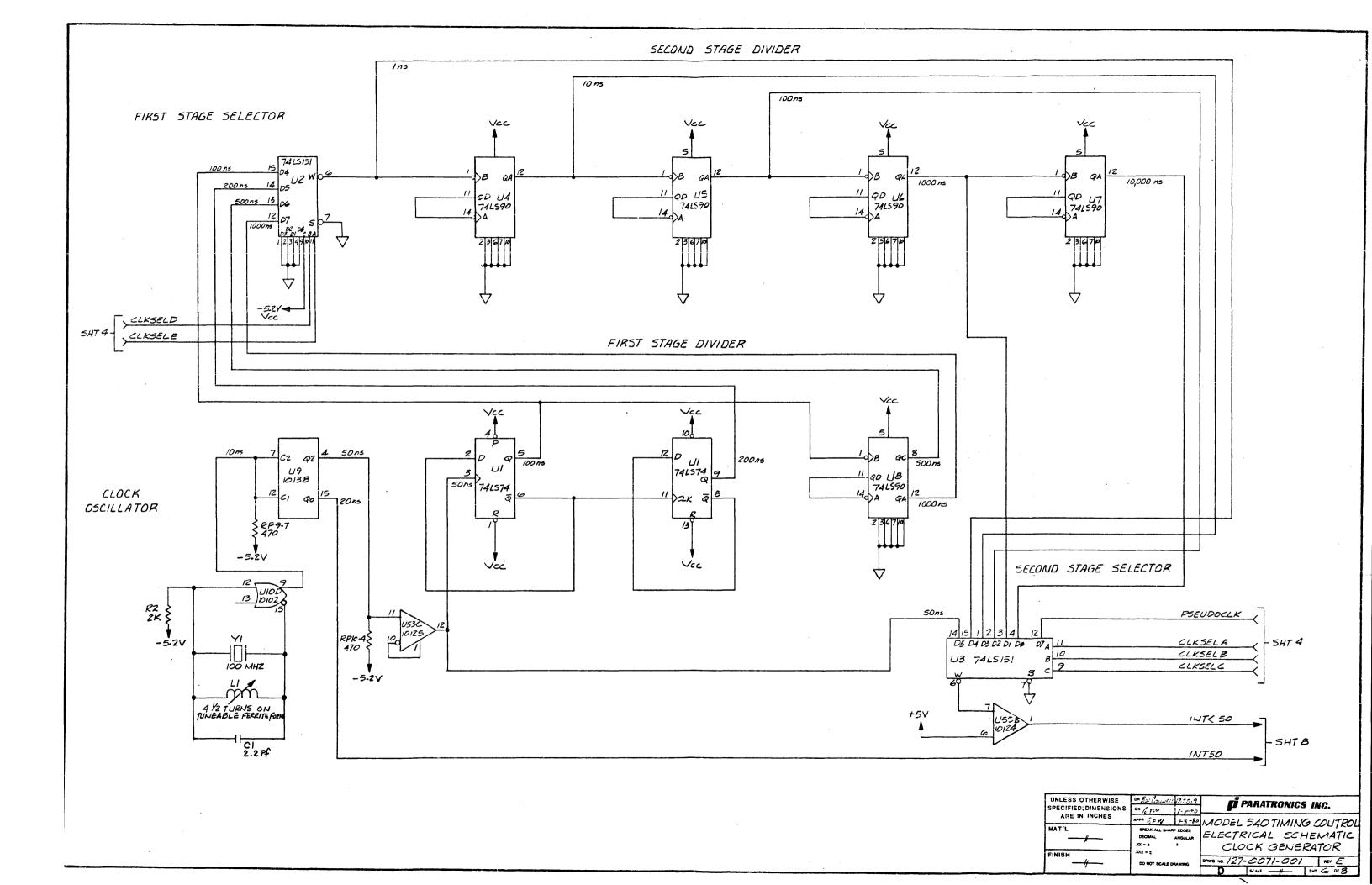

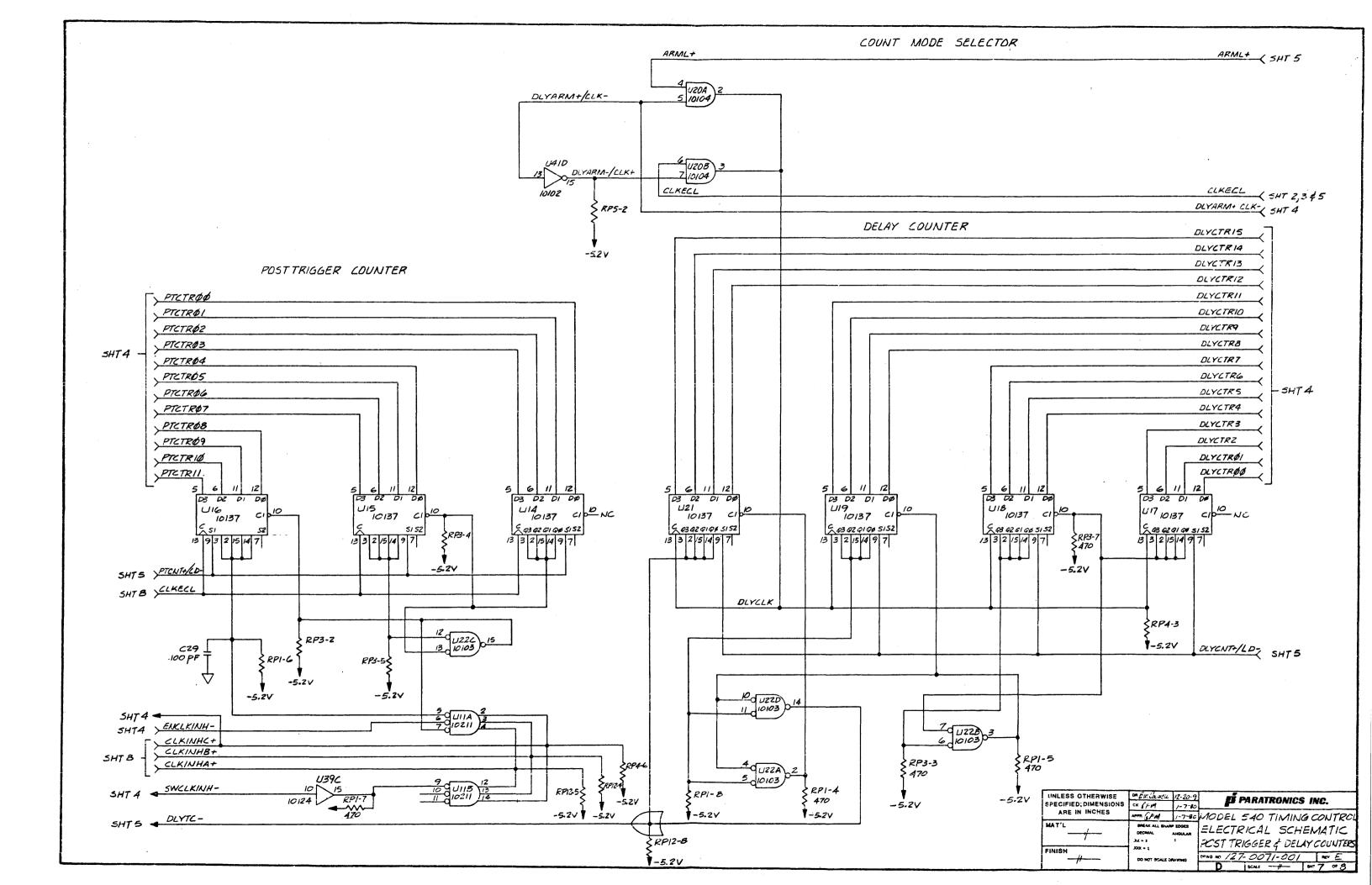

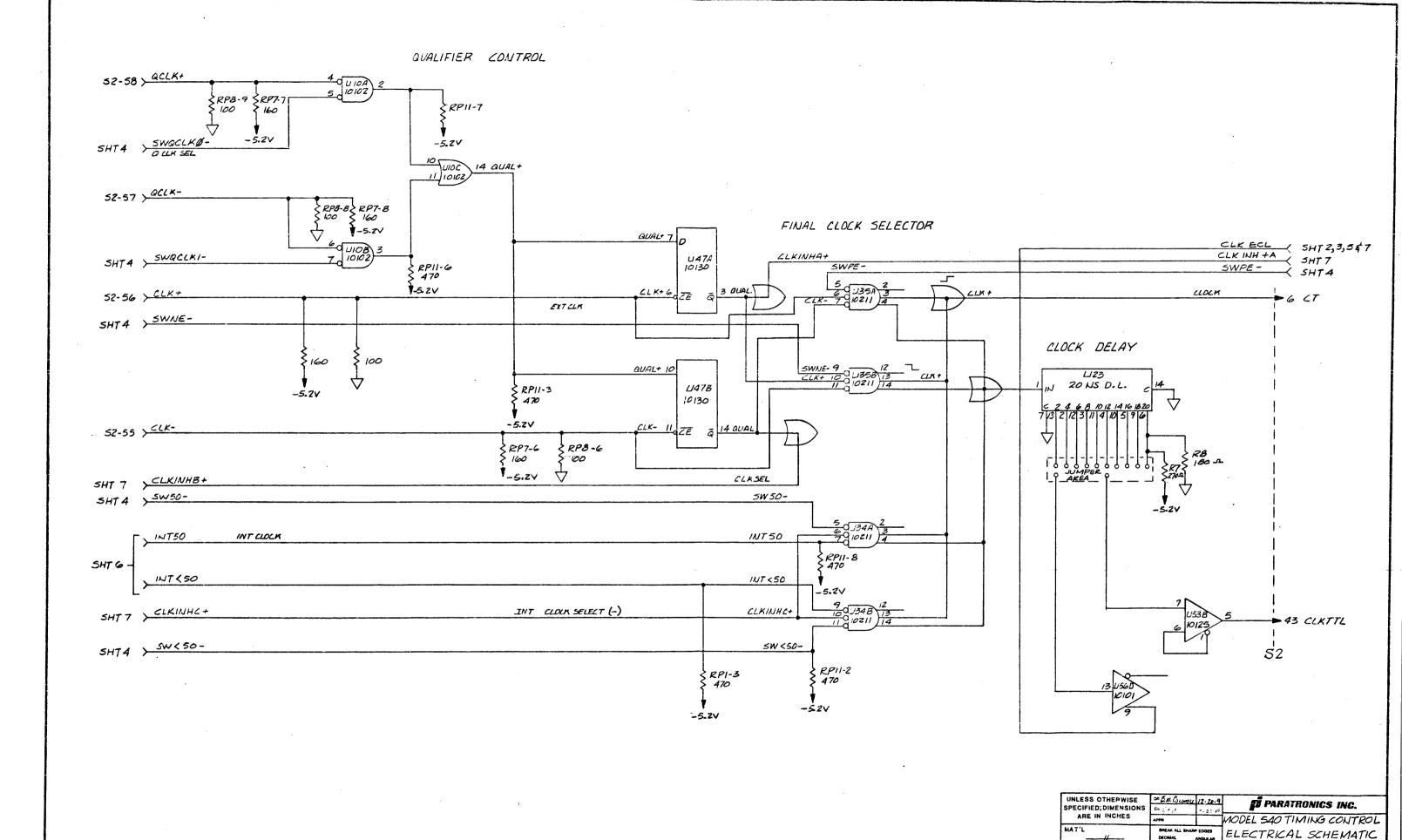

| 10.0  | 10.1         | CONTROL BOARD INTRODUCTION FUNCTIONAL DESCRIPTION 10.2.1 PROCESSOR INTERFACE 10.2.2 CLOCK GENERATOR 10.2.3 CLOCK CONTROL 10.2.4 TRIGGER CONTROL 10.2.5 ARM CONTROL 10.2.6 SEQUENCER 10.2.7 POSTTRIGGER AND DELAY COUNTERS SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                         | 10-1<br>10-1<br>10-1<br>10-2<br>10-3<br>10-6<br>10-7<br>10-8<br>10-9                                                         |

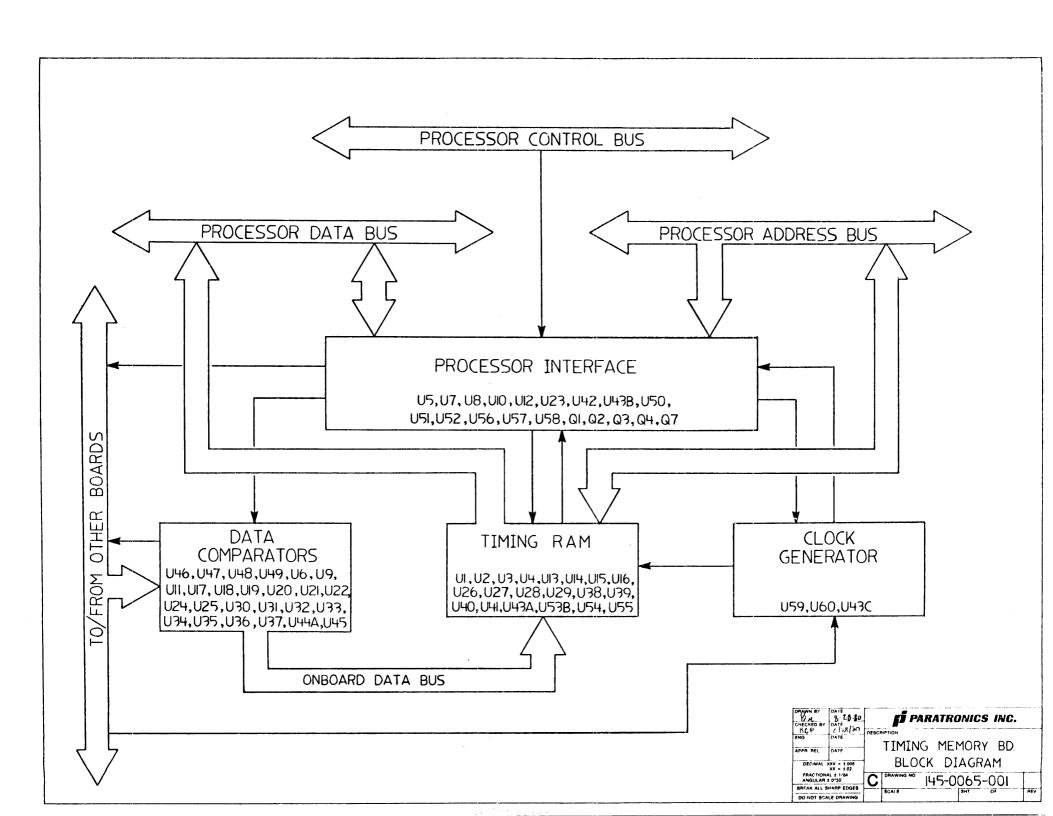

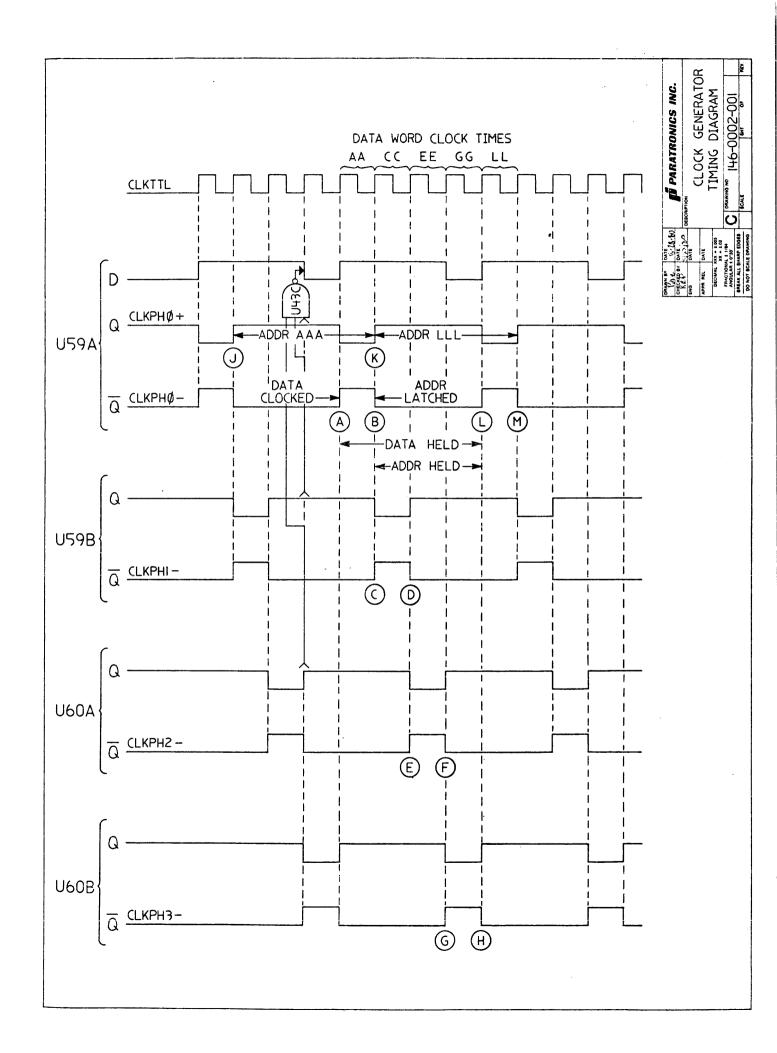

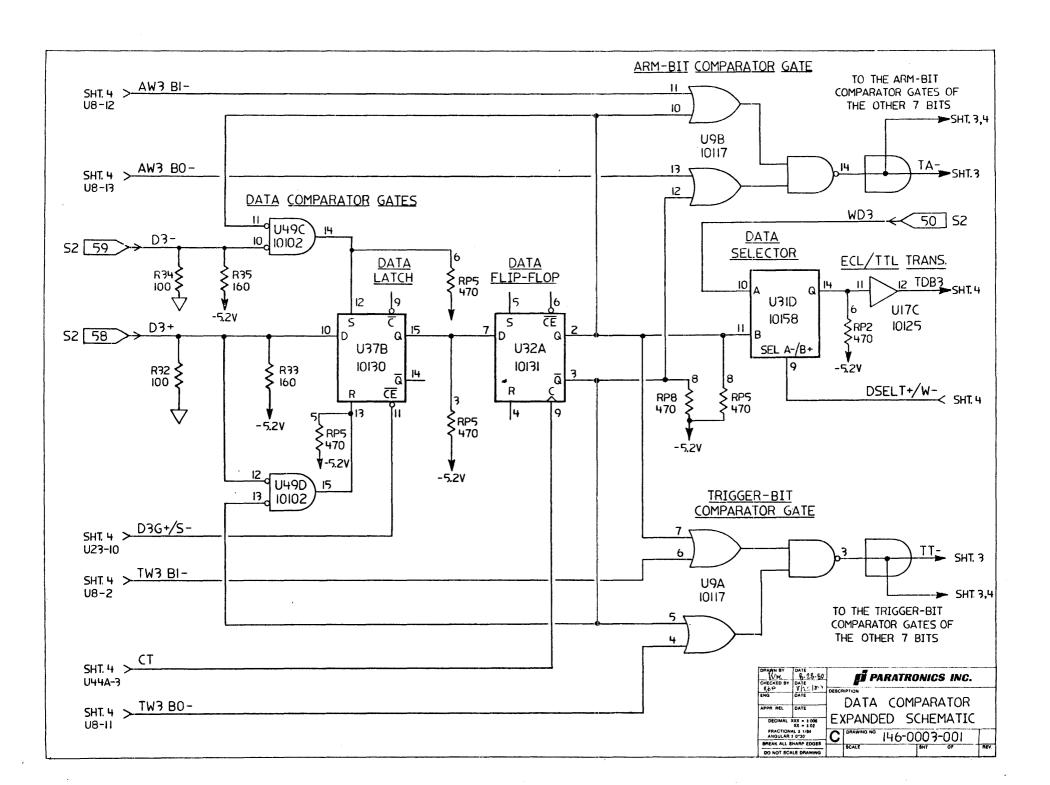

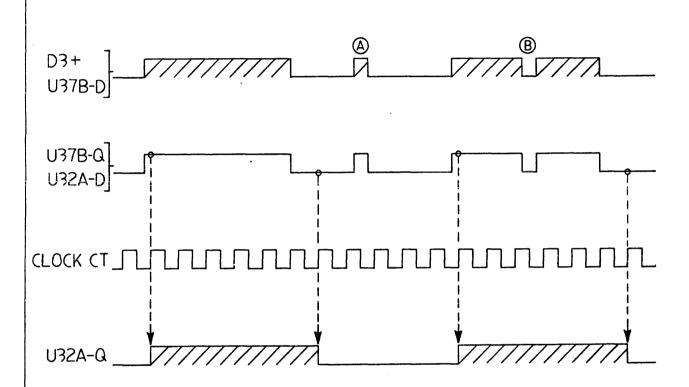

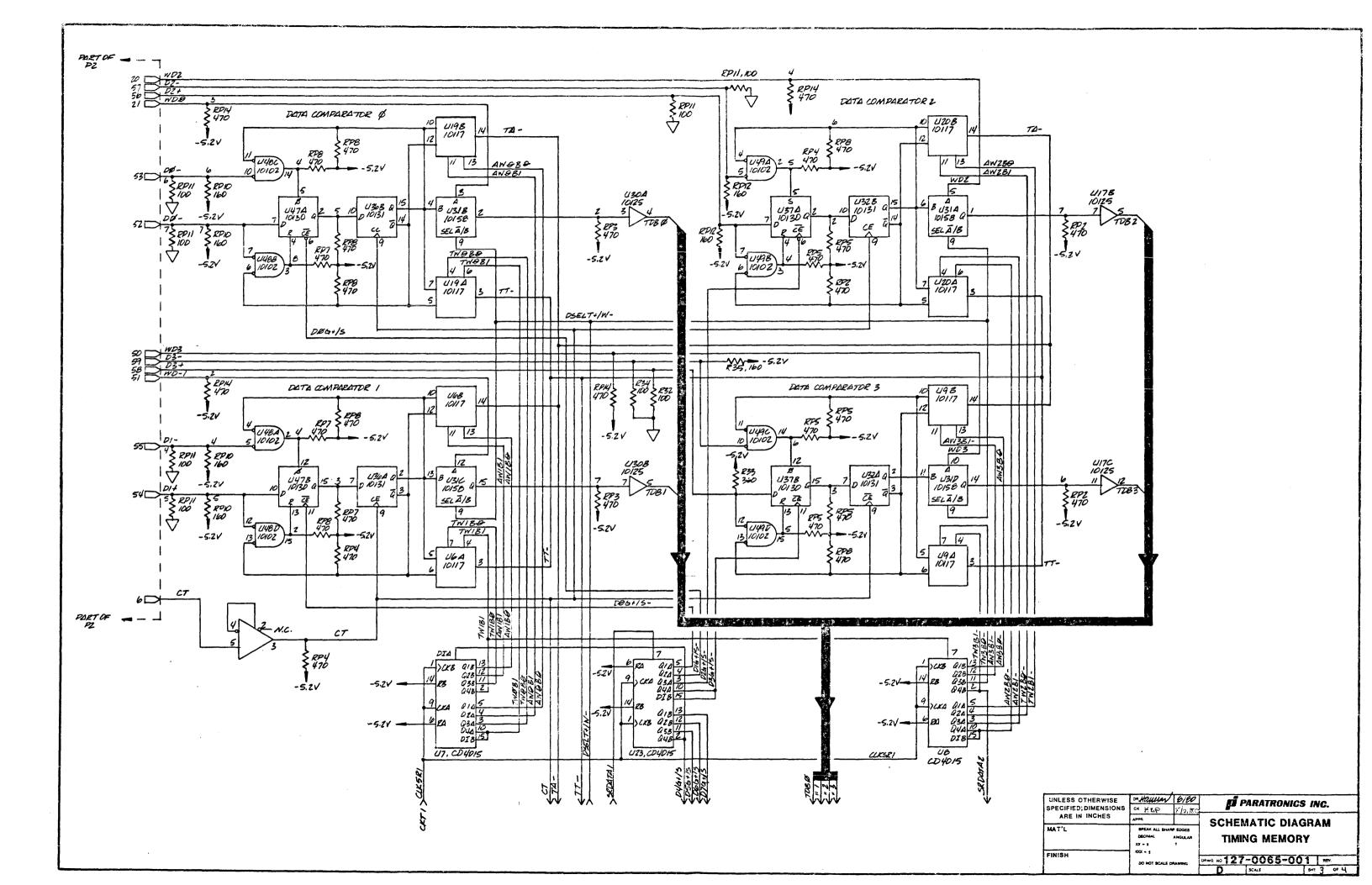

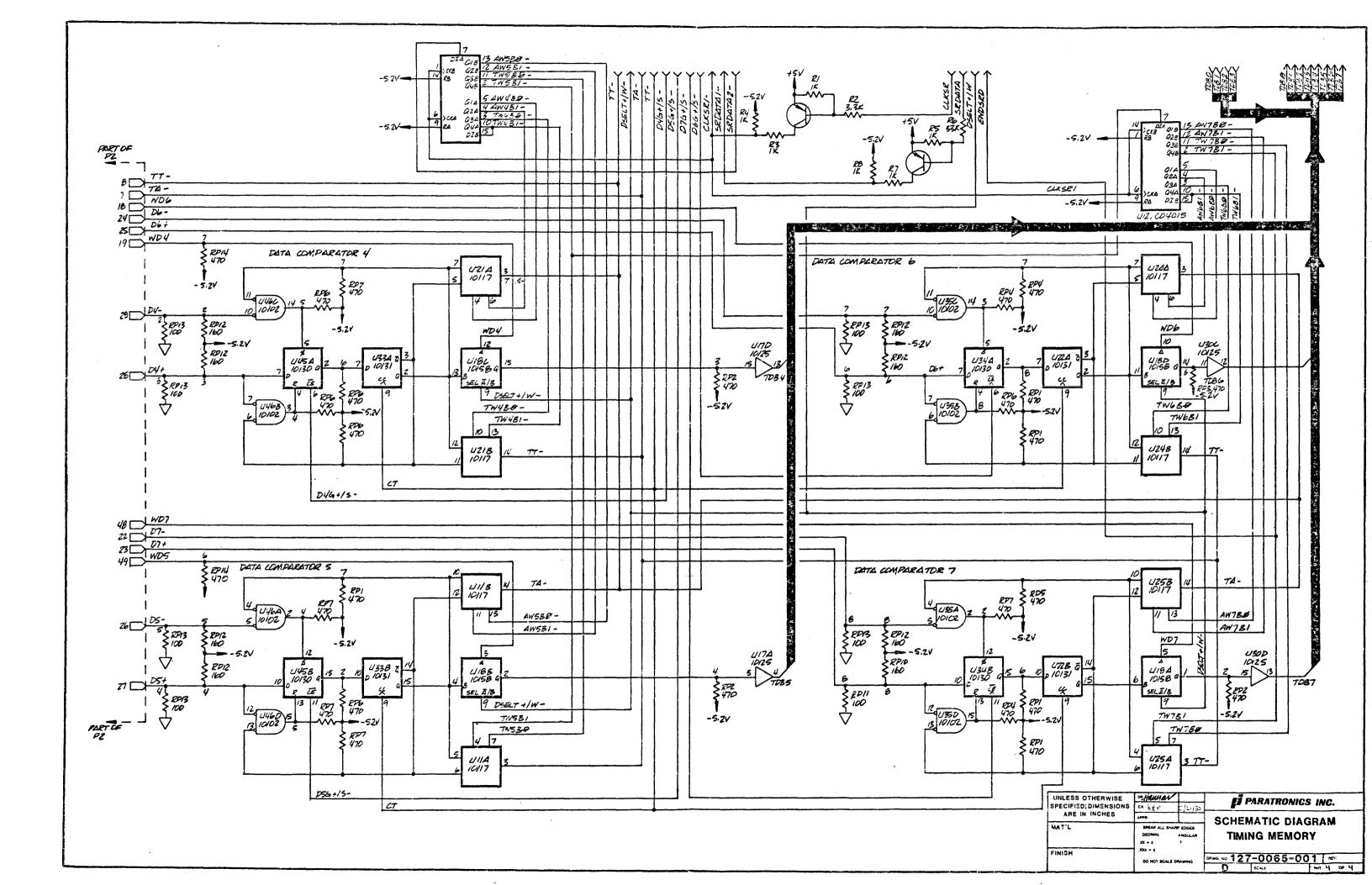

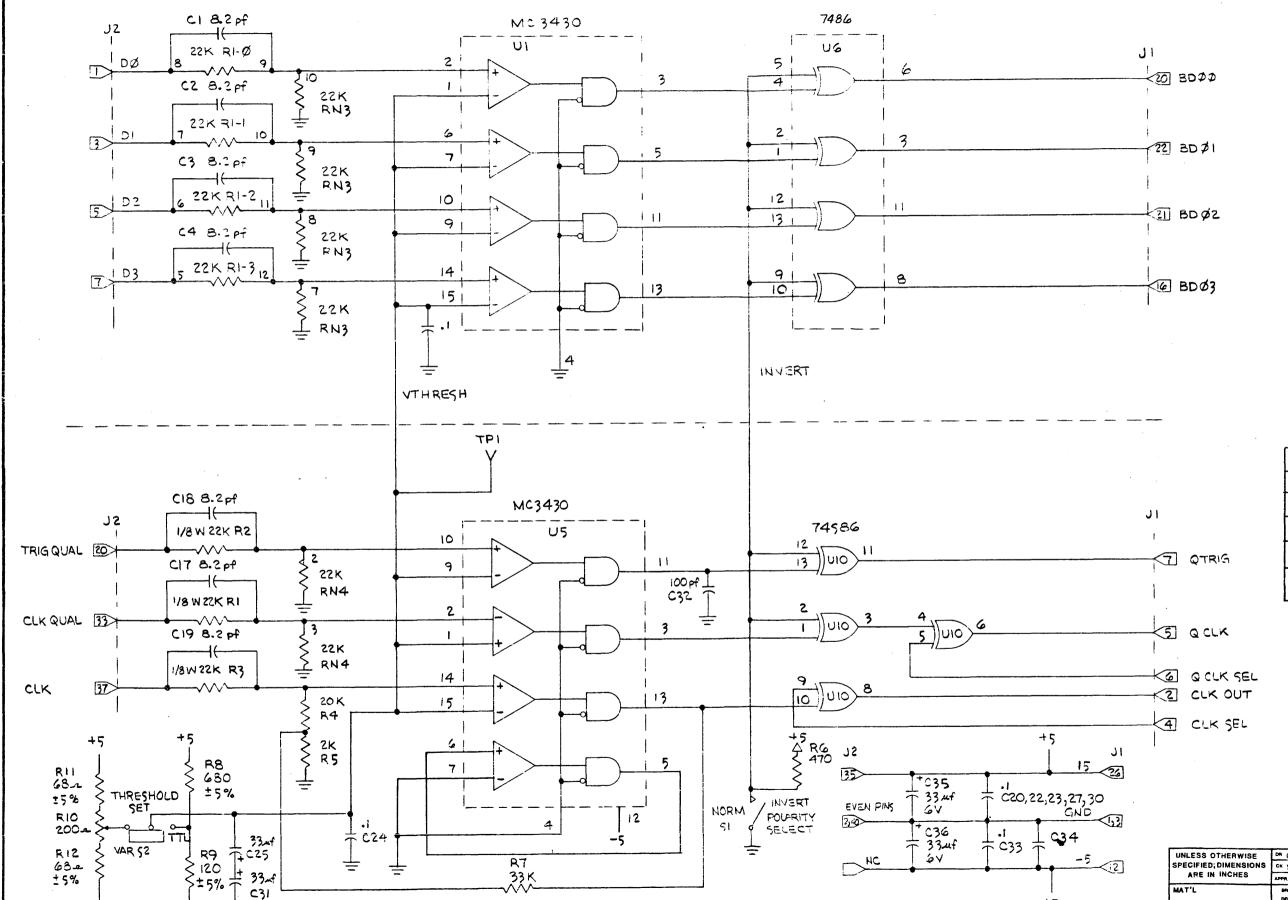

| 11.0  | 11.1<br>11.2 | MEMORY BOARD INTRODUCTION FUNCTIONAL DESCRIPTION 11.2.1 PROCESSOR INTERFACE 11.2.2 CLOCK GENERATOR 11.2.3 TIMING RAM 11.2.4 DATA COMPARATORS SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                                                      | 11-1<br>11-1<br>11-1<br>11-3<br>11-4<br>11-7                                                                                 |

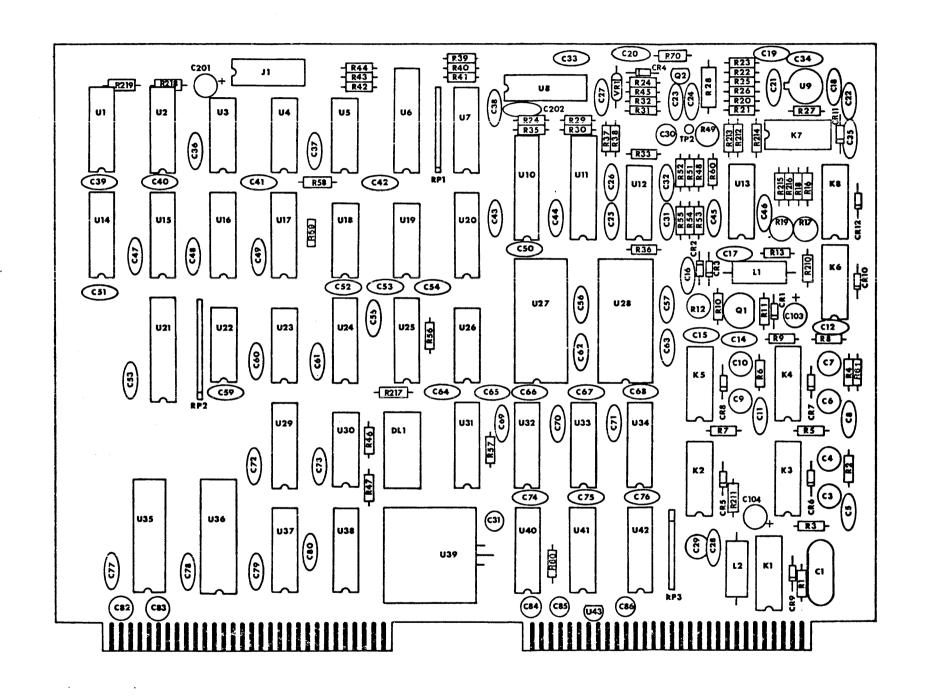

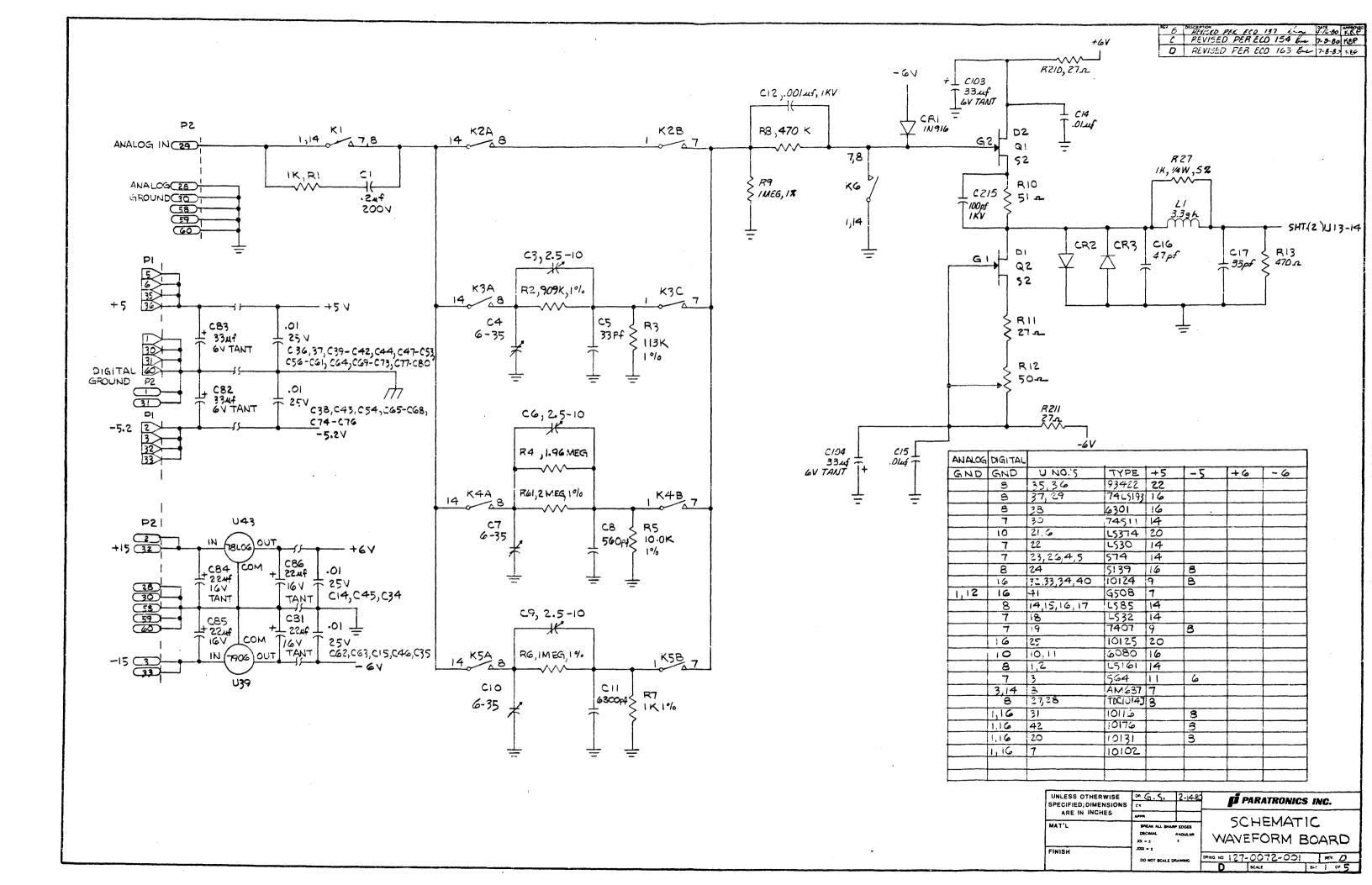

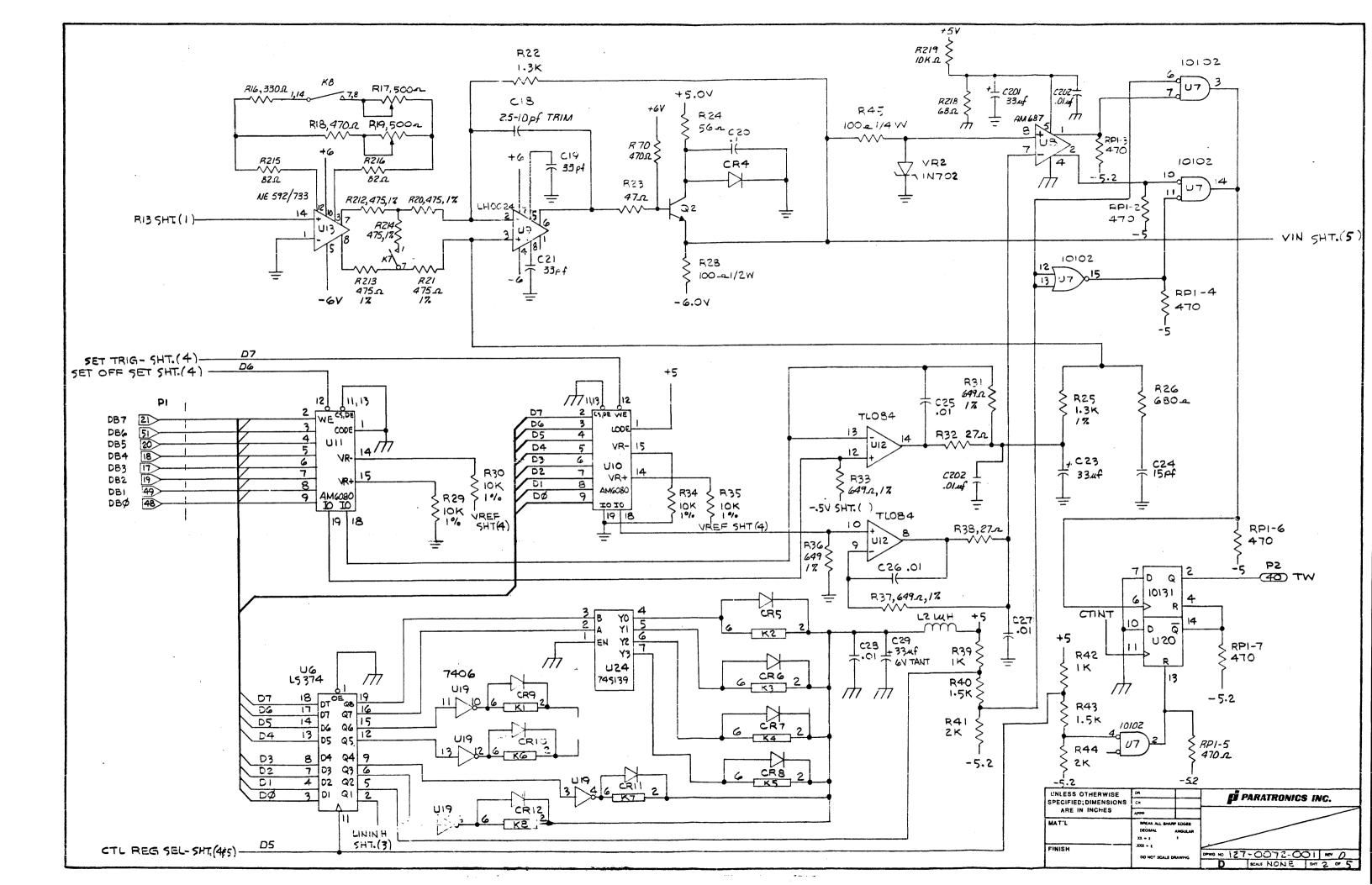

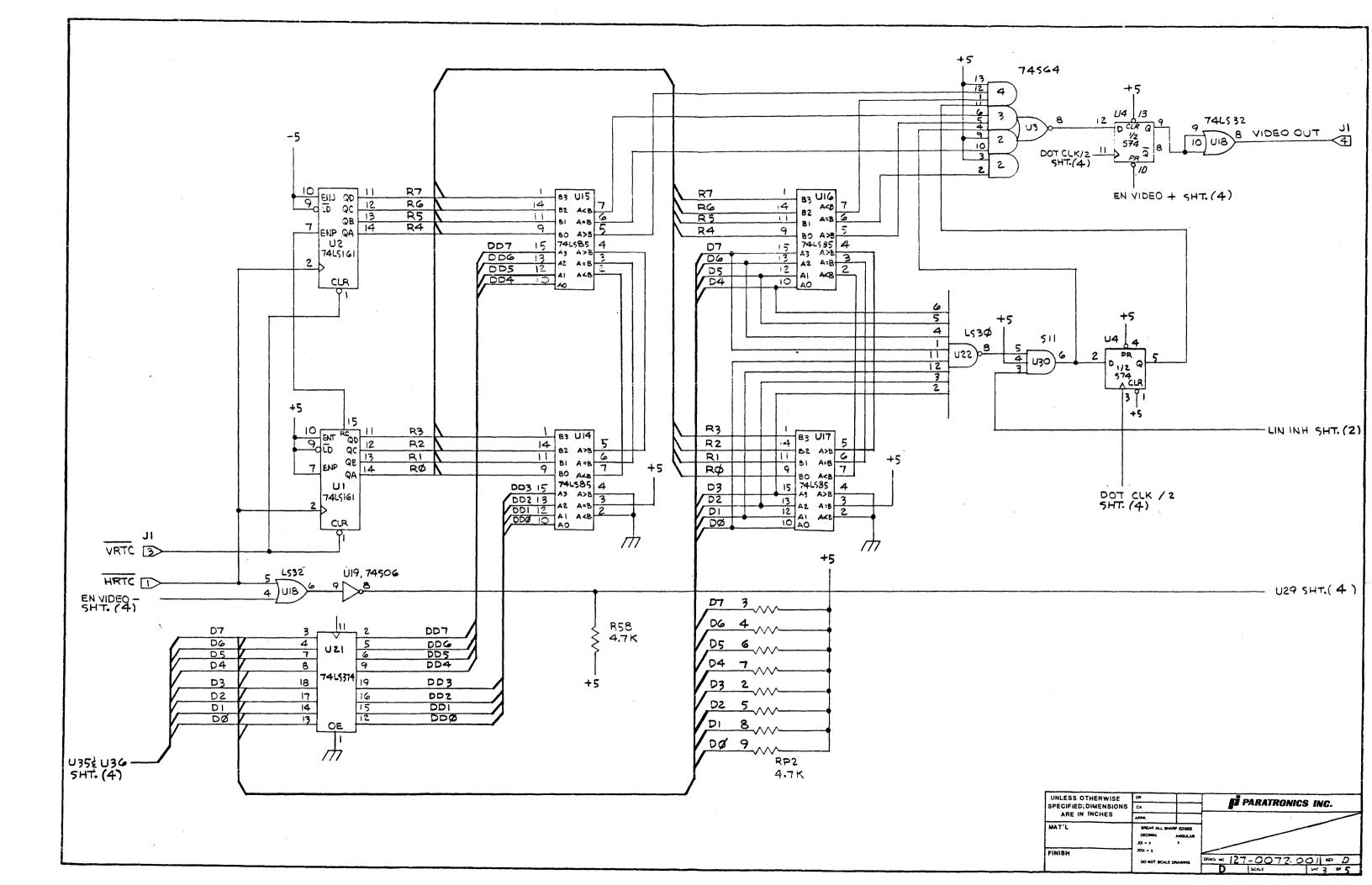

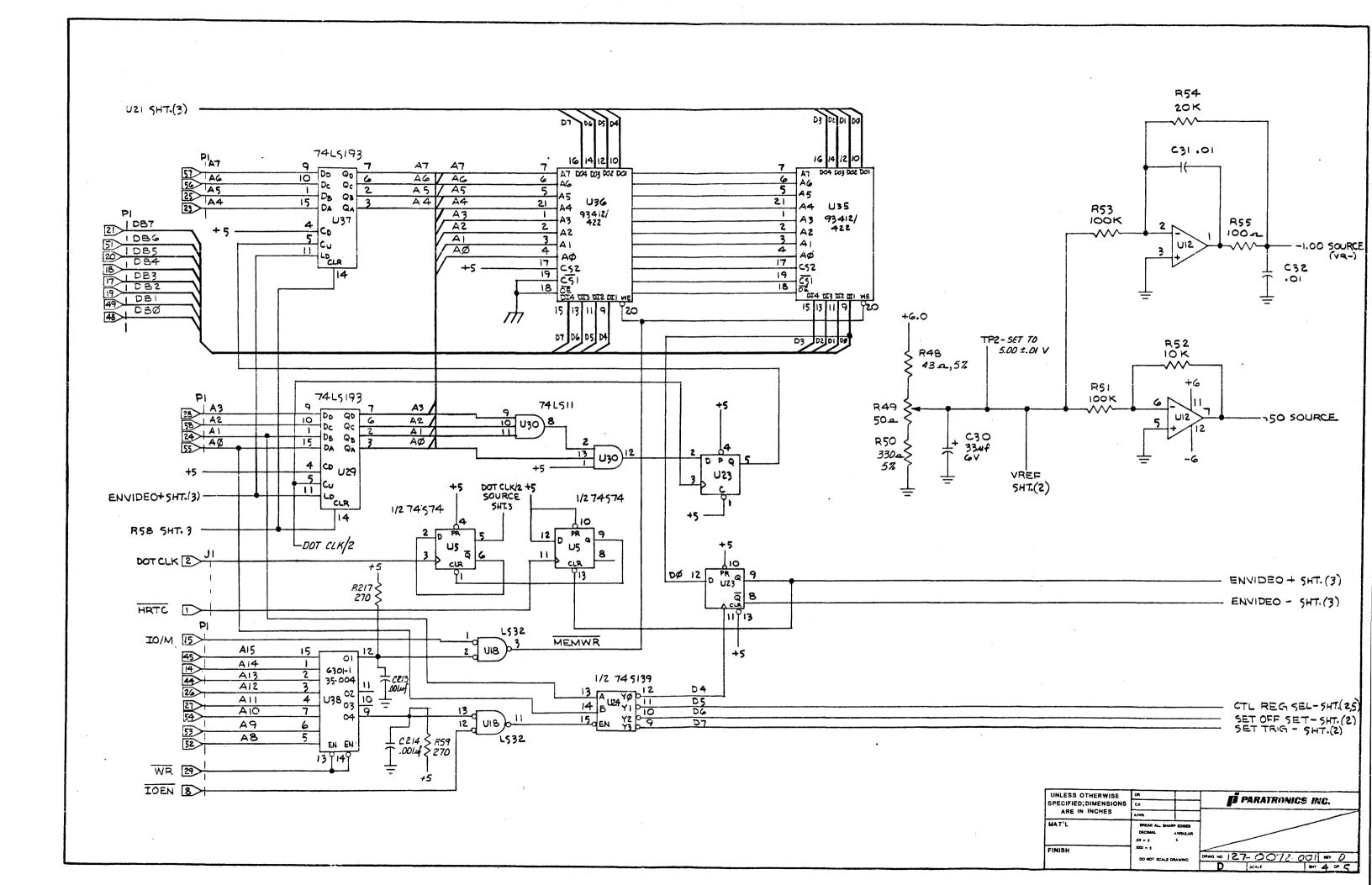

| 12.0  | 12.2         | RM BOARD INTRODUCTION FUNCTIONAL DESCRIPTION SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                                                                                                                                                      | 12-1<br>12-1<br>12-1<br>12-2                                                                                                 |

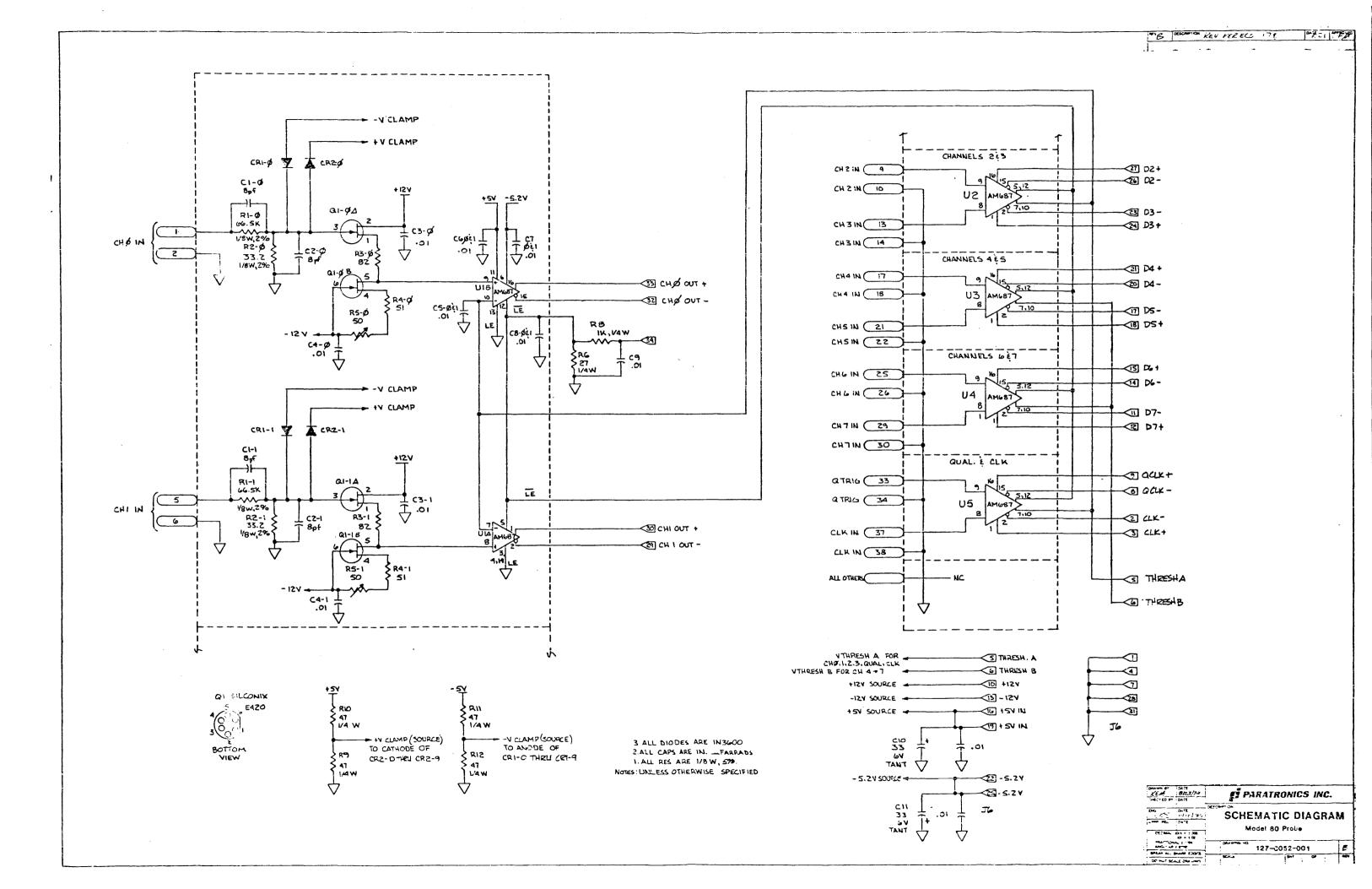

| 13.0  |              | MODEL 51A PROBE  13.1.1 INTRODUCTION  13.1.2 FUNCTIONAL DESCRIPTION  13.1.3 SCHEMATIC, BOARD LAYOUT, & PARTS LIST  MODEL 80 PROBE  13.2.1 INTRODUCTION  13.2.2 FUNCTIONAL DESCRIPTION  13.2.2.1 INPUT BUFFERS  13.2.2.2 COMPARATORS  13.2.2.3 APPLICATION  13.2.3 SCHEMATIC, BOARD LAYOUT, & PARTS LIST | 13-1<br>13.1-1<br>13.1-1<br>13.1-1<br>13.2-1<br>13.2-1<br>13.2-1<br>13.2-2<br>13.2-2<br>13.2-3<br>13.2-4<br>13.3-1<br>13.3-1 |

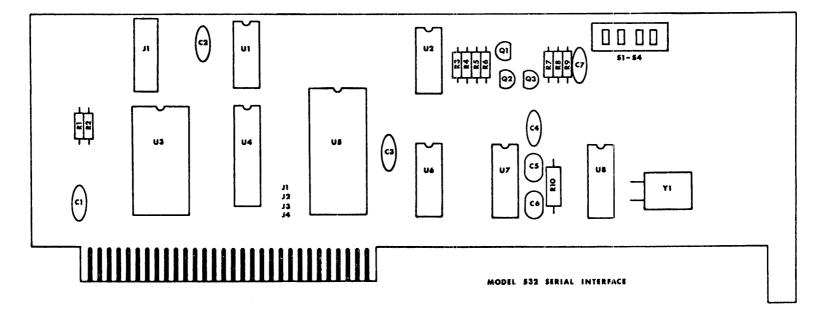

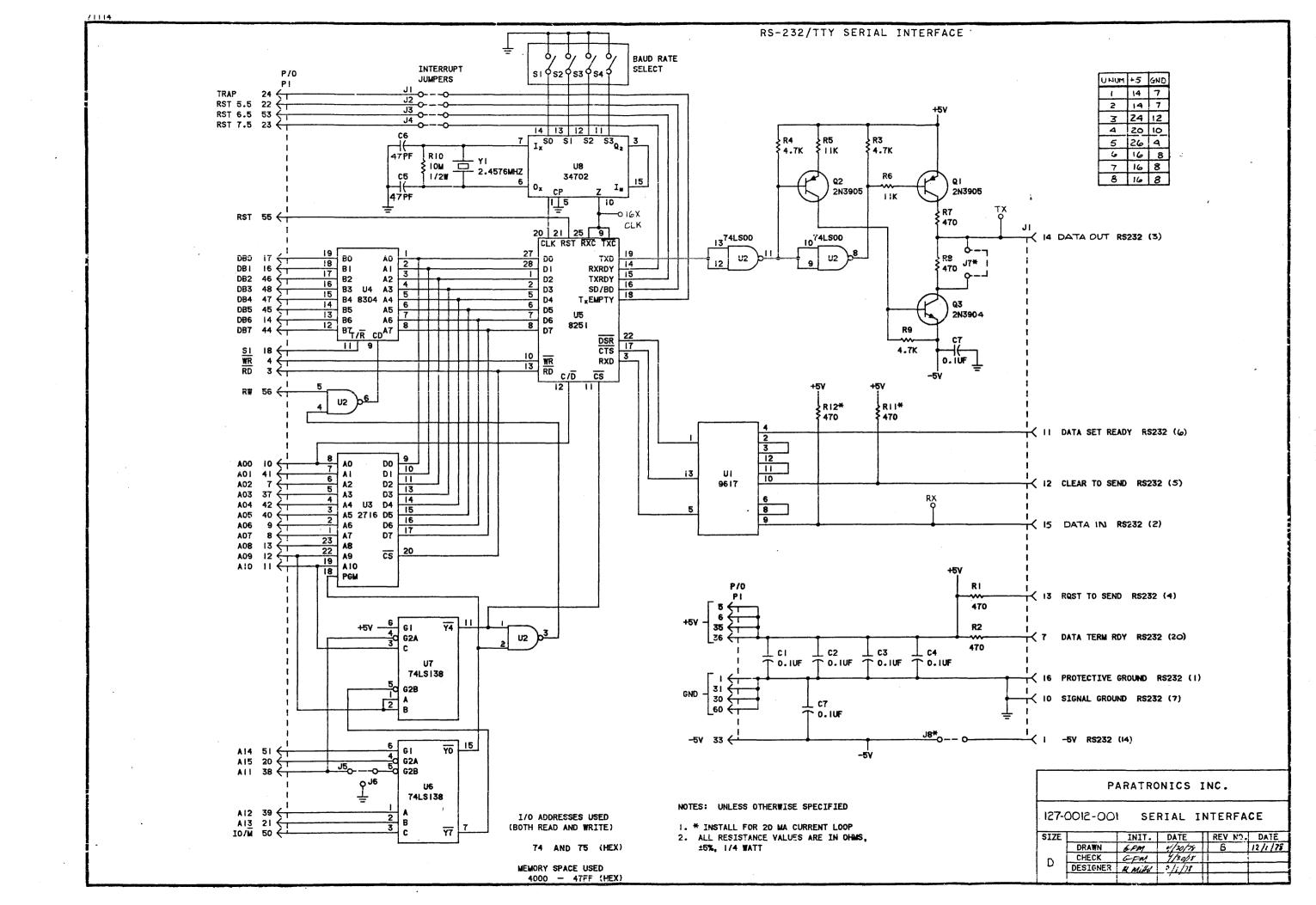

| 14.0  |              | S SERIAL INTERFACE BOARD (RS-232-C, 20 mA) 14.1.1 INTRODUCTION 14.1.2 FUNCTIONAL DESCRIPTION 14.1.3 ALTERNATE CONFIGURATIONS 14.1.4 SCHEMATIC, BOARD LAYOUT, & PARTS LIST                                                                                                                               | 14-1<br>14.1-1<br>14.1-1<br>14.1-1<br>14.1-1<br>14.1-2                                                                       |

| SECTI | <u>ON</u>                                                                                                                                                          | PAGE                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

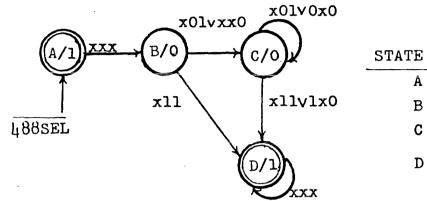

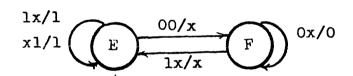

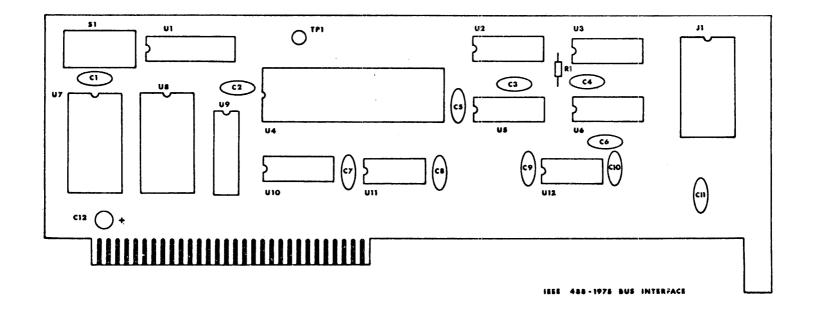

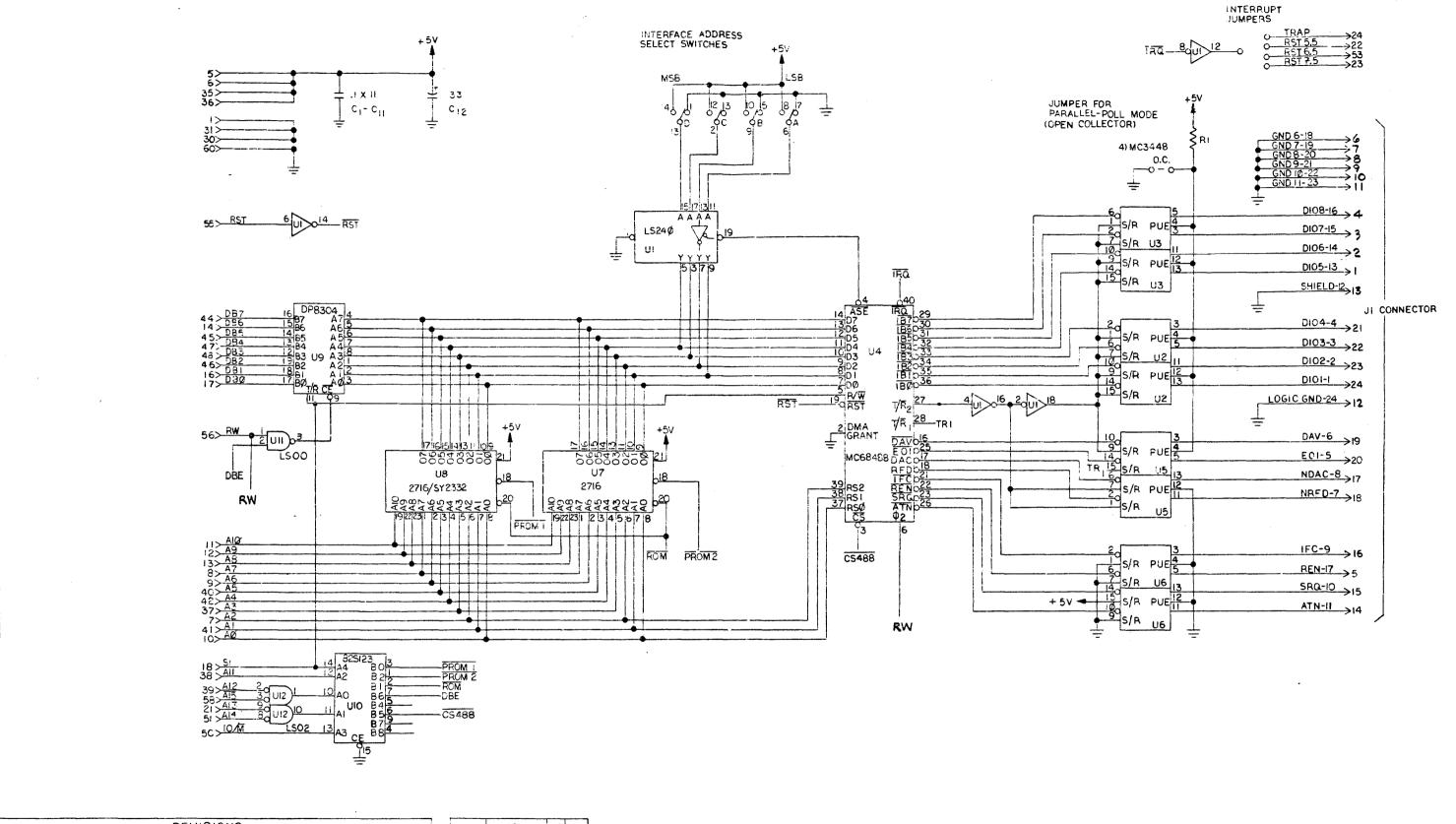

|       | 14.2 GPIB INTERFACE BOARD (IEEE-488) 14.2.1 INTRODUCTION 14.2.2 FUNCTIONAL DESCRIPTION 14.2.3 ALTERNATE CONFIGURATION 14.2.4 SCHEMATIC, BOARD LAYOUT, & PARTS LIST | 14.2-1<br>14.2-1<br>14.2-1<br>14.2-1<br>14.2-2 |

| 15.0  | SIGNAL & INTERCONNECTION TABLES                                                                                                                                    | 15-1                                           |

| 16.0  | GLOSSARY                                                                                                                                                           | 16-1                                           |

# 1.0 INTRODUCTION

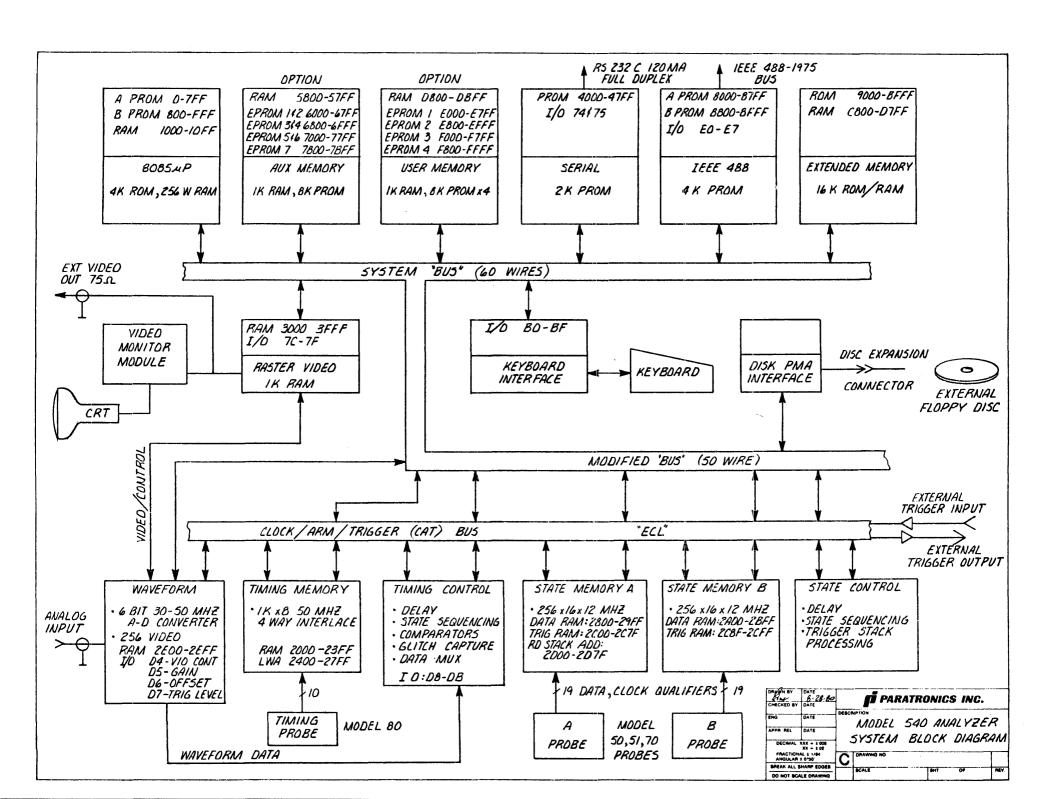

The Paratronics PI 540 Logic Analysis System combines, in a single package, facilities for logic analysis of state, timing, and waveform information. Inputs are provided for 32 state channels, 8 timing (or additional state) channels, and 1 waveform channel. The state, timing, and waveform sections can be used independently as separate analyzers, or linked one to the other for interdependent triggering.

# 1.1 PRINCIPLES OF OPERATION

All three types of analyzers represented in the PI 540 are basically devices for collecting data under specified conditions and storing the data in memory for detailed examination. Data is stored in memory starting at the lowest address. If the memory is filled before data collection is terminated, storage starts at the beginning of memory again, writing over the data already there. Thus the memory always contains, at any given moment, the most recent memoryful of data. When data collection stops, in this overflow case the last address filled is treated as the "end" of memory, and the next address is treated as the "beginning" of memory for purposes of analysis.

To start data collection, the RESET key on the keyboard is pressed. When and if certain preestablished conditions (the trigger conditions) are met, the data collection is automatically halted by the analyzer. Or, it may be stipulated that the data collection continue for a brief period after the trigger event until a specified amount of posttrigger data has been collected. Once data collection has stopped, the data can be displayed in various ways for convenient analysis.

In the PI 540, each input channel (incoming data line) is, in effect, assigned its own strip of memory that is one bit wide and as long as the memory is deep (250 bits for the state memory and 1000 bits for the timing and waveform memory). There are 32 input channels in the state section, 8 more in the timing section, and 1 in the waveform section.

The varying data on the input channels is fed to IC latches where it is latched by clock pulses. At each clock pulse, a sample of the stabilized data is read from the latch into memory. The state and timing analyzers assume that data on the input channels is <u>logic</u> data; that is, that it is either TRUE or FALSE. If the input level is above a preselected threshold, the data is stored in memory as TRUE (logic 1); if below that threshold, it is stored as FALSE (logic 0).

For the <u>State Analyzer</u>, the TRUE or FALSE state of the data from bit to bit is the <u>subject under investigation</u>. Therefore, the clock pulses are taken from the system under test (the target system), are chosen so that the data of interest is stable at clock time, and are usually closely related to the master clock for that system. The source of clock pulses is <u>external</u> to the analyzer; and because the clock that is being fed to the analyzer's latches bears a fixed time relationship to the data being collected, the clocking is said to be synchronous.

For the <u>Timing Analyzer</u>, the subject under investigation is usually the time relationships of the transitions of logic data present on various data lines. The precision with which such data transitions (from TRUE to FALSE, or vice versa) can be located in relative time is a function of how often the data is sampled. Thus, the higher the frequency of the sampling clock, the higher the resolution of the timing information contained in the collected samples. The synchronous external clock used in the state mode is usually unsuitable for the timing mode because the transitions under examination are very often occuring at target-system clock intervals. Therefore, small time differences between transitions on the various incoming channels could be completely obscured if the target-system clock were used to sample the data.

Because of these considerations, an <u>internal</u> clock is provided from within the timing analyzer. This clock is <u>asynchronous</u> with respect to the incoming data. A maximum internal clock frequency of 50 MHz is available in the PI 540. However, slower internal clock rates may be selected in order to capture data over as long an interval of time as is consistent with the resolution required. (The lower the clock frequency, the longer the time interval represented by a 1000-bit memoryful of data samples.)

An external clock input is also provided on the timing analyzer, and external clocking may be selected if a suitable external clock is available and preferable for some reason. Furthermore, an alternate state-equivalent display is provided for the timing data. This alternate display, in conjunction with the external clock, allows the timing analyzer to be used as an 8-channel state analyzer with a 1000-word data collection memory.

For the <u>Waveform Analyzer</u>, the incoming data is no longer assumed to be logic data. The objective now is to capture and store a single-occurrance analog waveform so that it can later be continuously displayed for detailed analysis. As with the timing analyzer, high resolution is important, and the 50 MHz internal clock is used for data sampling. (Again, lower clock rates may be selected when some degree of resolution can be given up in exchange for a longer captured time interval.)

The voltage level on the waveform input channel is sampled at the selected clock rate, and the value of each sample is converted to digital form with 6-bit precision. The digital value of the sample is then stored in the 1000-word timing memory previously described. As with the state and timing analyzers, the occurrance of a designated trigger event stops the data collection after a preselected number of posttrigger samples. The captured waveform can then be displayed in selected ways under software control and with the aid of a special auxiliary video memory.

Aside from the state, timing, and waveform modes, the PI 540 has two broad operational modes; collection and display. While the analyzer is displaying data or a menu, it cannot collect data; and while it is collecting data it cannot display data or a menu. The analyzer enters the collection mode when the RESET key is pressed. At that time, any menu or data that was on the screen is replaced by the appropriate data format, but without data. While data is being collected, the only screen updating that occurs is the posting of short announcements of progress through the arm and trigger levels. When triggering occurs and any specified collection of posttrigger data is completed, or when the FORCE DISPLAY key is pressed, the analyzer stops data

collection and enters the display mode. It remains in the display mode, displaying either data or menus, until RESET is again pressed.

It should be mentioned that in the data display mode, only <u>valid</u> data is displayed. Valid data is data collected <u>after</u> the RESET key is pressed. This may or may not be a complete memoryful, depending on how soon triggering occurred and how much posttrigger data, if any, was specified.

# 1.2 OPERATIONAL FEATURES

A full-feature PI 540 may be configured from the keyboard to any of the following ten analyzer modes:

- a. 8 STATE channels with 1000-word data capture

- b. 16 STATE channels with 500-word data capture

- c. 32 STATE channels with 250-word data capture

- d. 40 STATE channels with 250-word data capture

- e. 8 TIMING channels with 1000-sample data capture

- f. 1 WAVEFORM channel with 1000-sample data capture

- q. 16 500-word STATE channels + 8 1000-sample TIMING channels

- h. 32 250-word STATE channels + 8 1000-sample TIMING channels

- i. 16 500-word STATE channels + 1 1000-sample WAVEFORM channel

- j. 32 250-word STATE channels + 1 1000-sample WAVEFORM channel

The 8-channel state mode is essentially the same as the 8-channel timing mode with the exception of the clock selection. In both modes (which are shown on the configuration menu as a single 8-channel tming/state dual mode) the data being displayed can be switched back and forth at will between the state and tming formats.

For <u>8-channel timing</u> analysis, the clock will probably be selected as internal, and the Timing probe's clock and clock-qualifier inputs will not be connected to the system under test. (Clock qualification is not available when an internal clock is being used.)

When the 8-channel Timing Analyzer section is used as a state analyzer, the mode may be either an 8-channel mode, in which the Timing section is used by itself as a state analyzer, or it may be a 40-channel mode, in which the 8-channel Timing section is used in cascade with the 32-channel State section in a 40-channel state analyzer.

For 8-channel state analysis, the clock will probably be selected as external, and the Timing probe's clock input will be connected to the system under test in order to provide the external clock. The clock-qualifier input may also be connected if qualification of the clock signal is desired. But the qualifier signal cannot be applied to the arm or trigger words (as the State probe's qualifier signals can with the State section).

In the <u>40-channel</u> <u>state</u> analysis mode, the 40-channel state analyzer is restricted to the more limited state analysis capabilities of the Timing Analyzer section. The clock will probably be selected as external, and the Timing probe's clock input will be connected to the system under test and will provide the external clock for both sections of the combined analyzer. (The

State section automatically receives the same clock selected for the Timing section.) The clock inputs of the two State probes cannot be used in the 40-channel mode and will not be connected. The two qualifier inputs on each of the two State probes can be used to qualify trigger words but cannot be used as clock qualifiers, and data-word clock qualification is not available. The clock-qualifier input of the Timing probe is the only clock qualifier that can be used. Keyboard control of the Timing probe's input threshold levels and hysteresis selection is still in effect.

In this 40-channel mode, only two levels of nested trigger words are available (called the arm word and trigger word in timing analysis) instead of the 16 levels that are ordinarily used in the State section. However, these two words are the full 40 bits long and can be qualified by the four State-probe qualifier bits and by the External and Waveform links. Also, the Timing section's delay functions can be applied. The memory depth is limited to the 250 words of the 32-channel State Analyzer.

Although these restrictions should be kept in mind for proper application, a 40-channel x 250-word state analyzer with a clock-qualifier bit and two levels of nested 40-bit trigger words with four qualifiers, two linkages, and a flexible delay function is nevertheless a very powerful instrument. It only seems limited in comparison with the unusually extensive features of the State Analyzer section.

Standard operational features, common to all modes unless otherwise noted, include:

- Full keyboard control of system modes, display formats, and all variable parameters

- b. Trigger and clock-qualifier linkage between state, timing, and waveform sections

- c. Sixteen levels of nested triggering in state modes (except in the 40-channel mode, which has two levels)

- d. Two levels of nested triggering in timing modes (called arm and trigger)

- e. Extensive and varied trigger delay capabilities

- f. Full data-width trigger words plus additional qualifiers

- g. Extensive clock qualification in state modes (except 40-channel mode, which has one clock qualifier)

- External input to trigger and clock-qualifier words

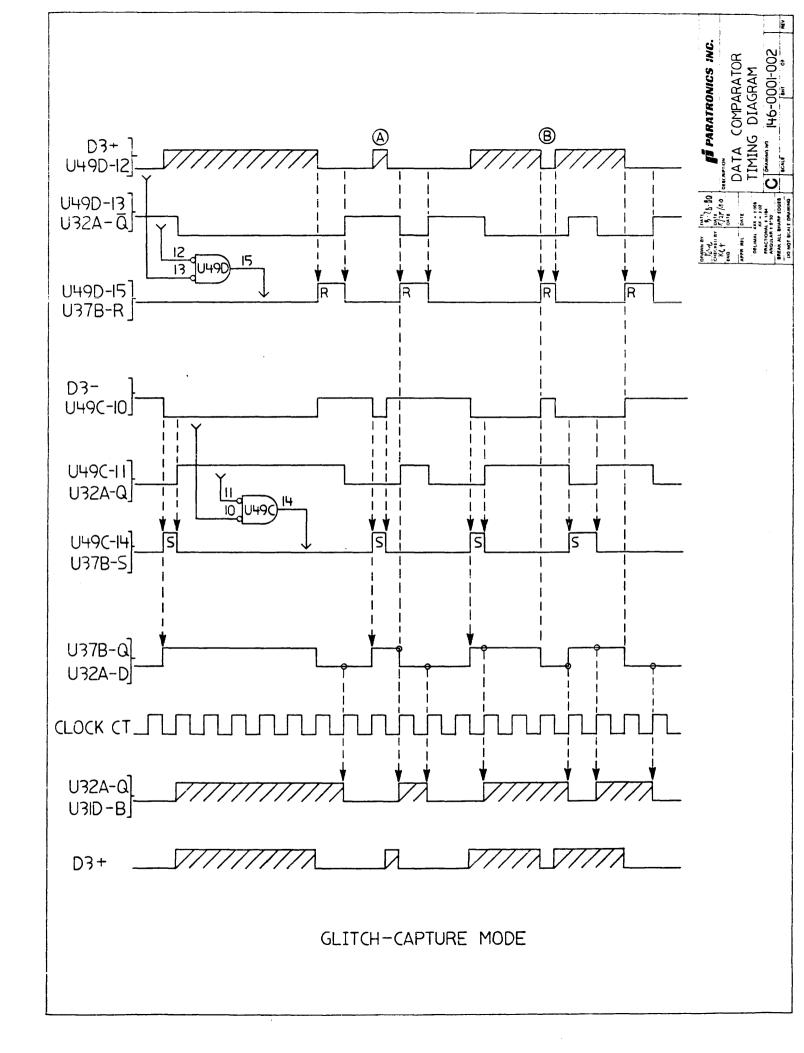

- i. Glitch capturing in the timing mode

- i. Comparison memories for various comparison functions

- k. PI's brand of signature analysis

- m. Fully controllable timing display (including channel order, movable expansion window, and equivalent-state format)

- n. Controllable waveform display (including movable expansion window)

- o. Selectable probe hysteresis and variable probe thresholds

- p. State display formats interchangeable at will between hexadecimal, octal, binary, decimal, or ASCII

# 1.3 GENERAL DESCRIPTION

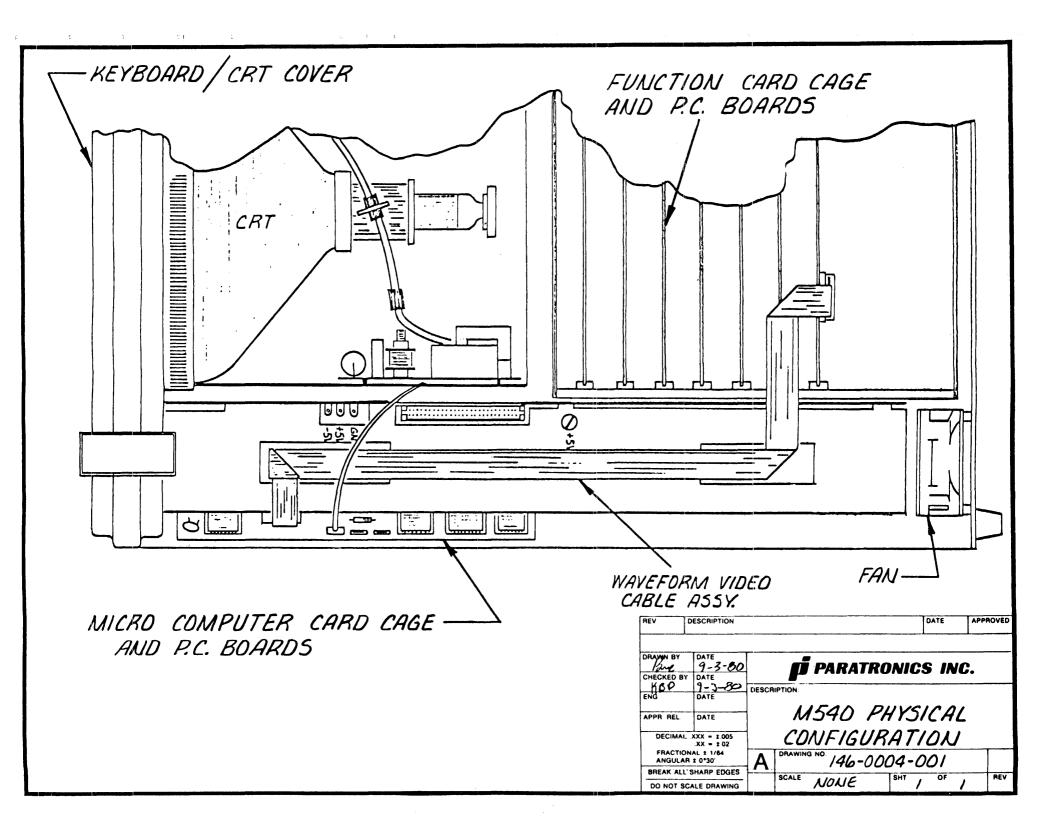

The physical configuration of the PI 540 is shown in figure 1-1. The four basic physical elements, as pointed out in the figure, are:

- a. The Folding Keyboard

- b. The Display Module

- c. The Microcomputer Section

- d. The Applications Section

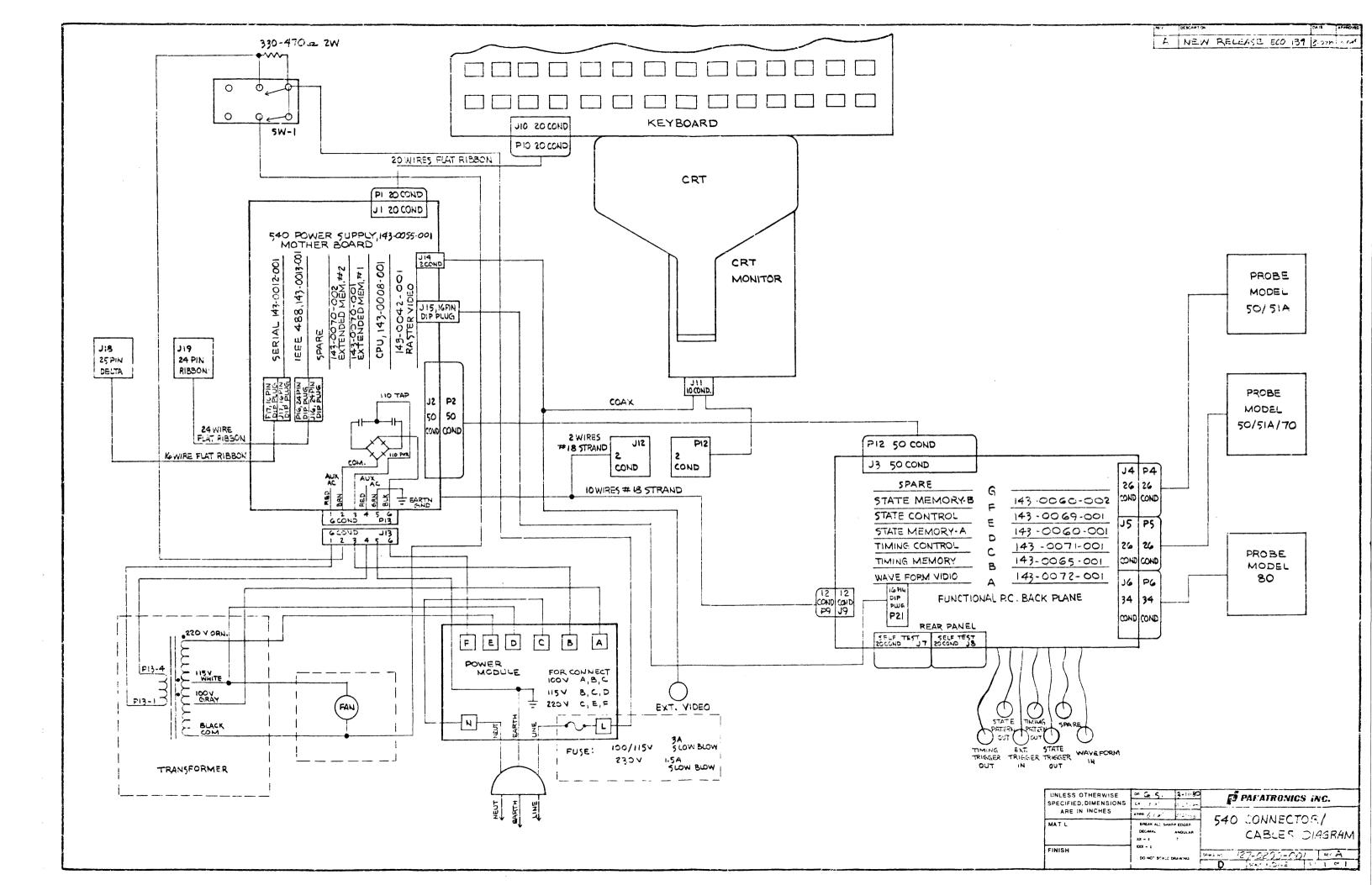

The functional configuration of the PI 540 is shown in the block diagram of figure 1-2. Please refer to these two figures when appropriate during the following discussion. They are positioned at the end of the section for easy reference.

The FOLDING KEYBOARD, when not in use, folds up against the front of the case so that the face of the CRT and the keyboard working surface are both protected during transit or storage of the analyzer. (This arrangement also allows both the CRT and the keyboard itself to be larger than they could be if they shared the same front panel.) When the analyzer is placed horizontally on a bench or table, the carrying handle may be folded back underneath the unit to act as a stand. The keyboard is then unlatched from its protective position and folded down to rest on the table surface at a comfortable angle. In some situations, it may be more convenient to place the analyzer upright on the floor; there are four rubber feet on the back of the unit for this purpose, and the folded-under handle acts as a rest for the opened keyboard. (Caution: Take care that the cooling fan in the rear is not obstructed.)

The keys themselves are completely covered by a plastic overlay sheet which protects them from dust and other contamination and carries the key legends as well as other keyboard labels. The keys are of the thin, snapaction contact type, and at each key location there is a slight dome beneath the plastic overlay. This dome gives way when pressed, thus providing tactile feedback of the key actuation. An audio feedback tone is also provided (at the operator's option). If an illegal key entry is made during any operation, a dual-tone error signal is sounded.

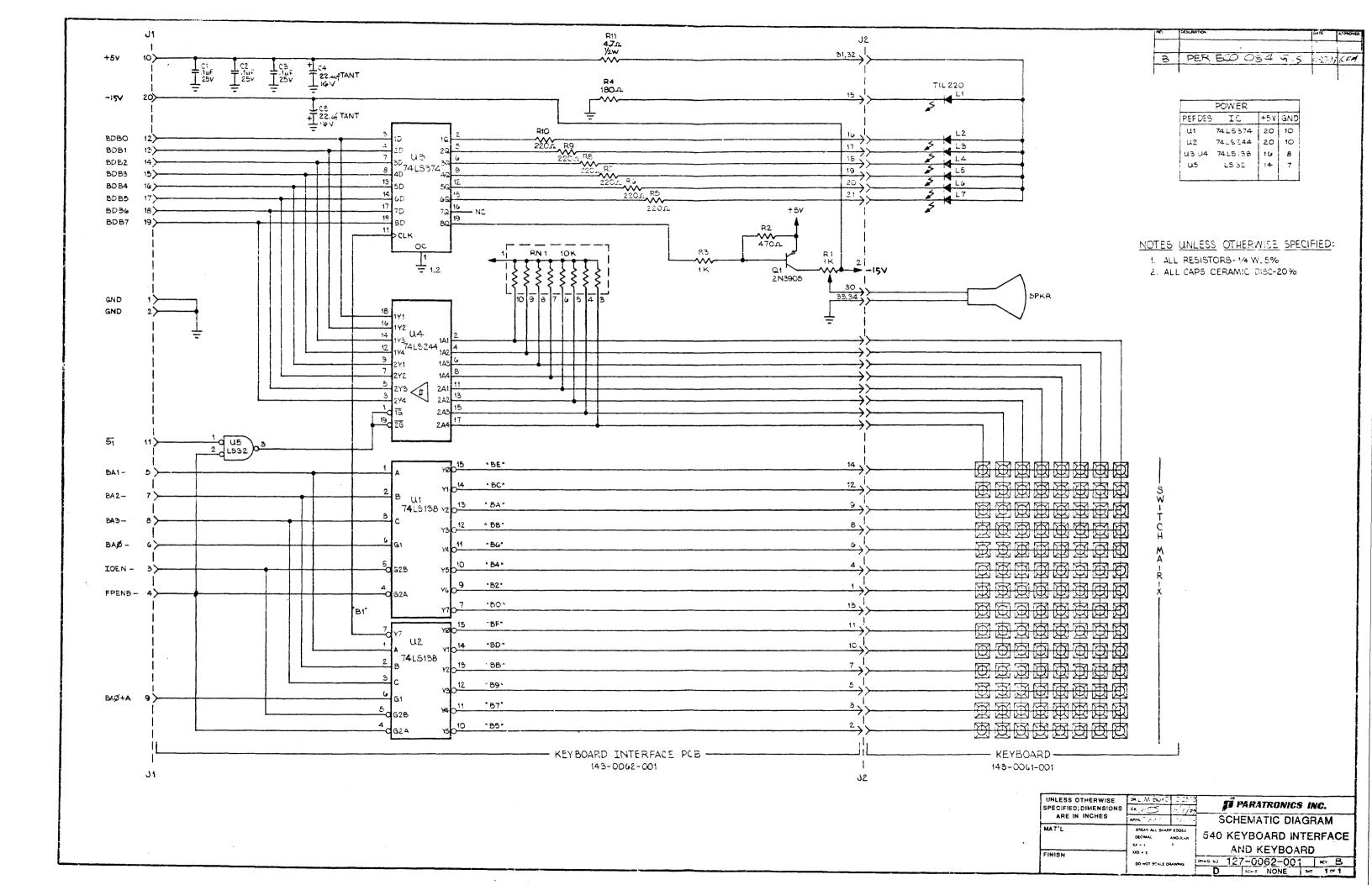

The keys are connected as input devices to the microprocessor, and the function of each key is determined entirely by software. Many keys have two functions, one for each of two different analyzer operating modes in which the key may be called into play. Such keys have two legends on the keytop, one legend in green and one in red. Above the group of keys involved, a green or red light indicates which legend applies in the current operating mode.

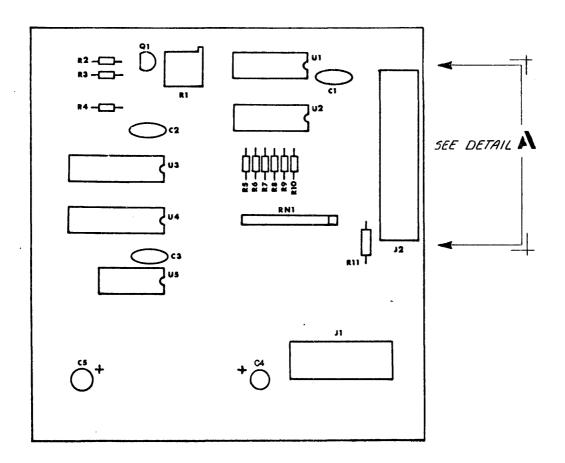

Within the keyboard housing, but underneath the keyboard itself, is the Keyboard Interface Board. This circuit board contains: scanning circuitry that allows the microcomputer to periodically scan the keyboard for switch closures; latches that allow the microprocessor to control the LED indicator lights on the keyboard; and the audio tone generator and its drive and control circuits.

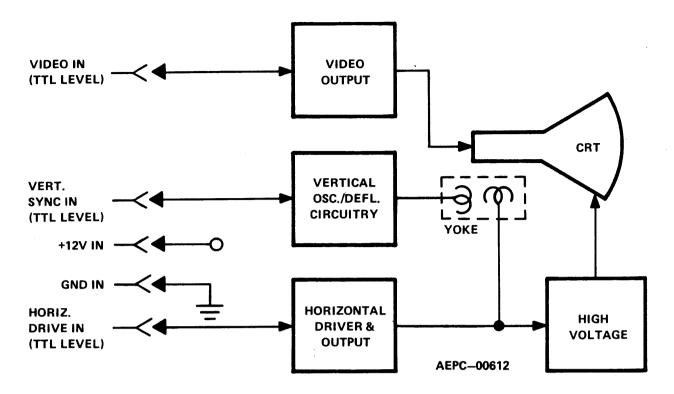

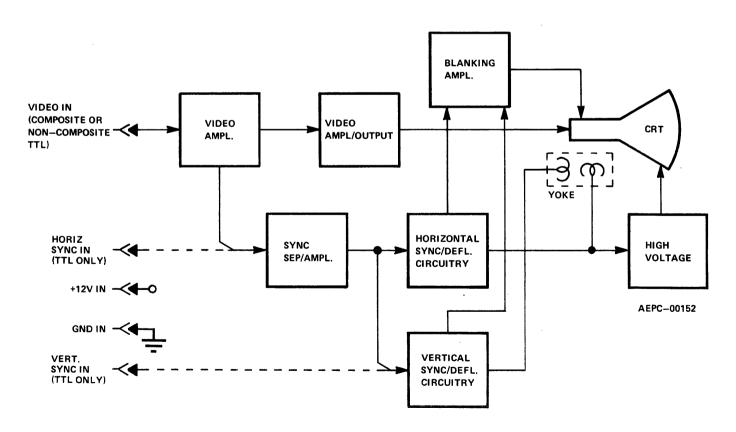

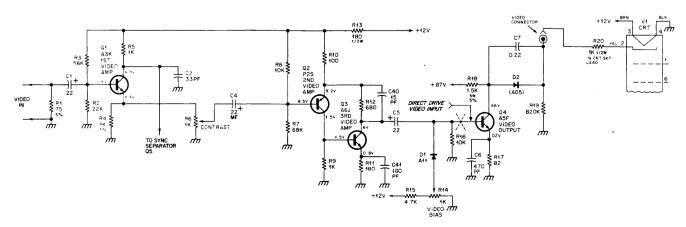

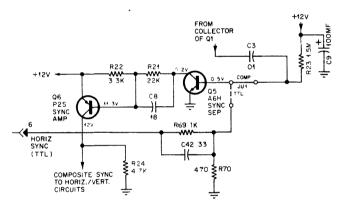

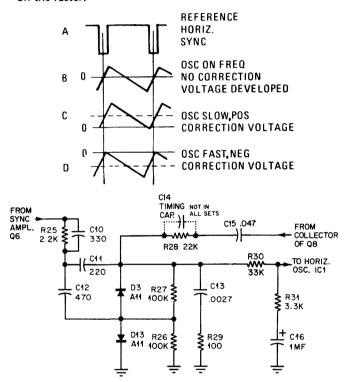

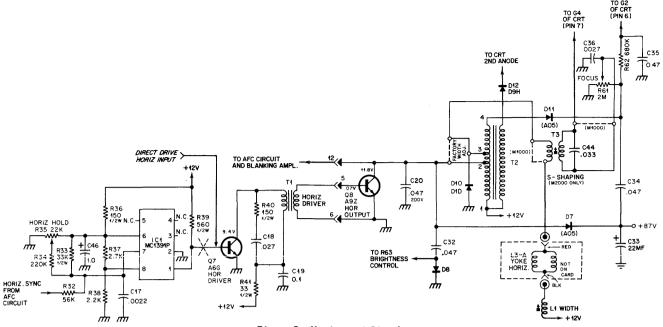

The <u>DISPLAY MODULE</u> contains a 9-inch CRT and the circuitry necessary to produce a raster scan. A composite video input signal is supplied from the Video Display Board in the Microcomputer Section. The only input power

required by the module is +12v, which is provided by the analyzer's power supply. High-voltage for the CRT is generated within the module by a circuit that operates from the +12 volts.

The MICROCOMPUTER SECTION is built up on the Microcomputer Motherboard. Mounted on the rear of this motherboard is a high-efficiency switching power supply that provides power for the entire PI 540. The remainder of the motherboard is equipped with card guides, sockets, and interconnections (the PI Standard Bus) for 8 circuit boards. Board locations are interchangeable on this motherboard, but typically, the circuit board complement is arranged as follows (top to bottom):

| Slot | <u>Circuit</u> <u>Board</u> |

|------|-----------------------------|

| 1    | Video Display Board         |

| 2    | Processor Board             |

| 3    | Extended Memory Board #1    |

| 4    | Extended Memory Board #2    |

| 5-8  | Available for options       |

The <u>Video</u> <u>Display</u> <u>Board</u> contains an LSI CRT controller (the Intel 8275), 1K bytes of screen-refresh RAM, a character-generator ROM, and various other related circuits. This board generates a composite video signal which, when sent to the Display Module, produces a memory mapped video display containing 16 rows of 64 alphanumeric characters, with each character occupying an 8 x 15 dot-matrix cell. In the timing display, line drawing is used in conjunction with the alphanumeric characters. (The waveform display, which also uses line drawing, is generated on another board, the Waveform Board, to be discussed later.)

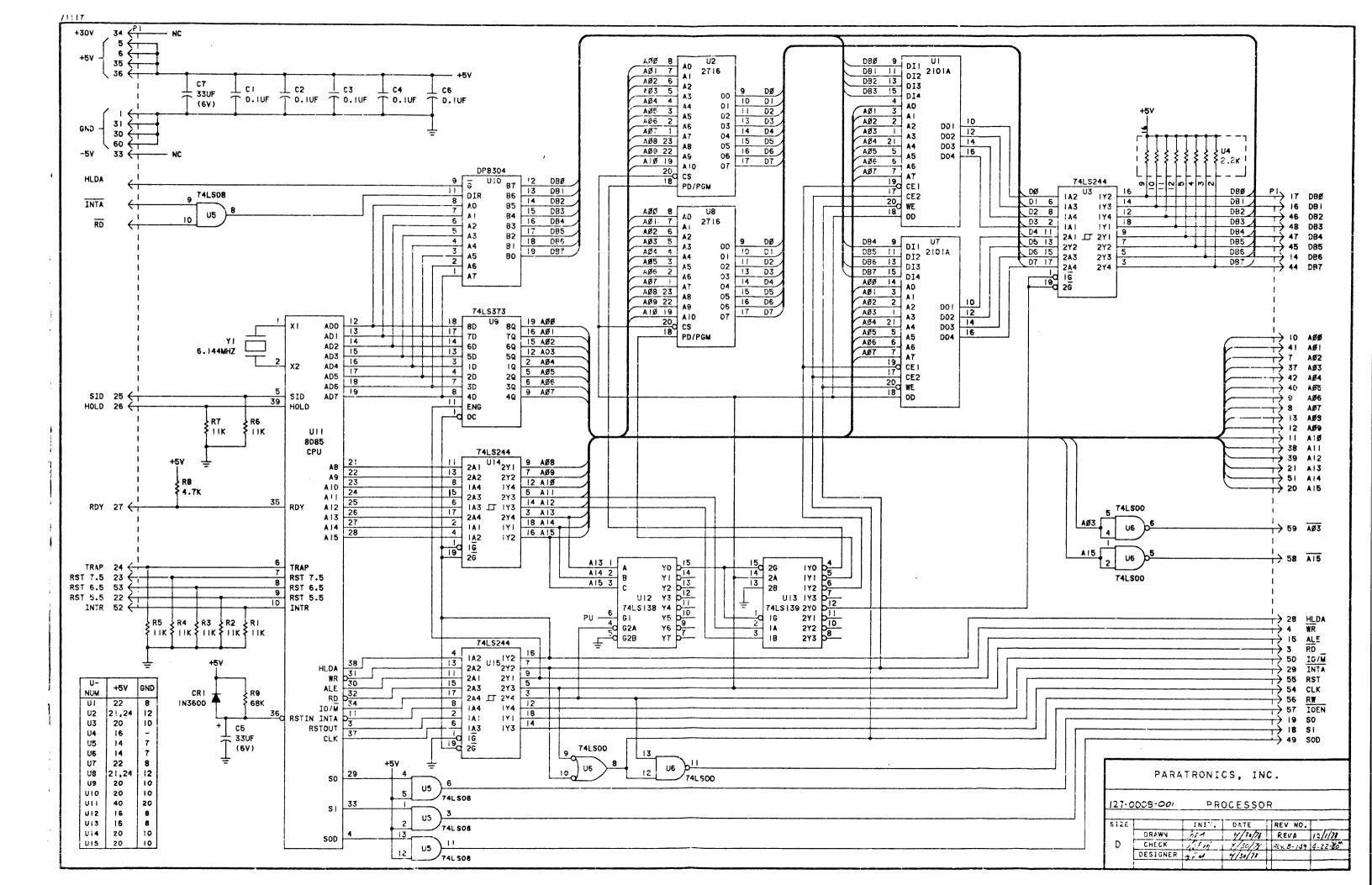

The <u>Processor Board</u> contains an 8085 microprocessor, 4K bytes of program storage ROM, 256 bytes of system RAM, and various buffering circuits. This board, by means of the system Control Program, exercises control over all analyzer functions. These functions include keyboard input, CRT display formatting and updating, storage of collected data in memory, and implementation of all operational features.

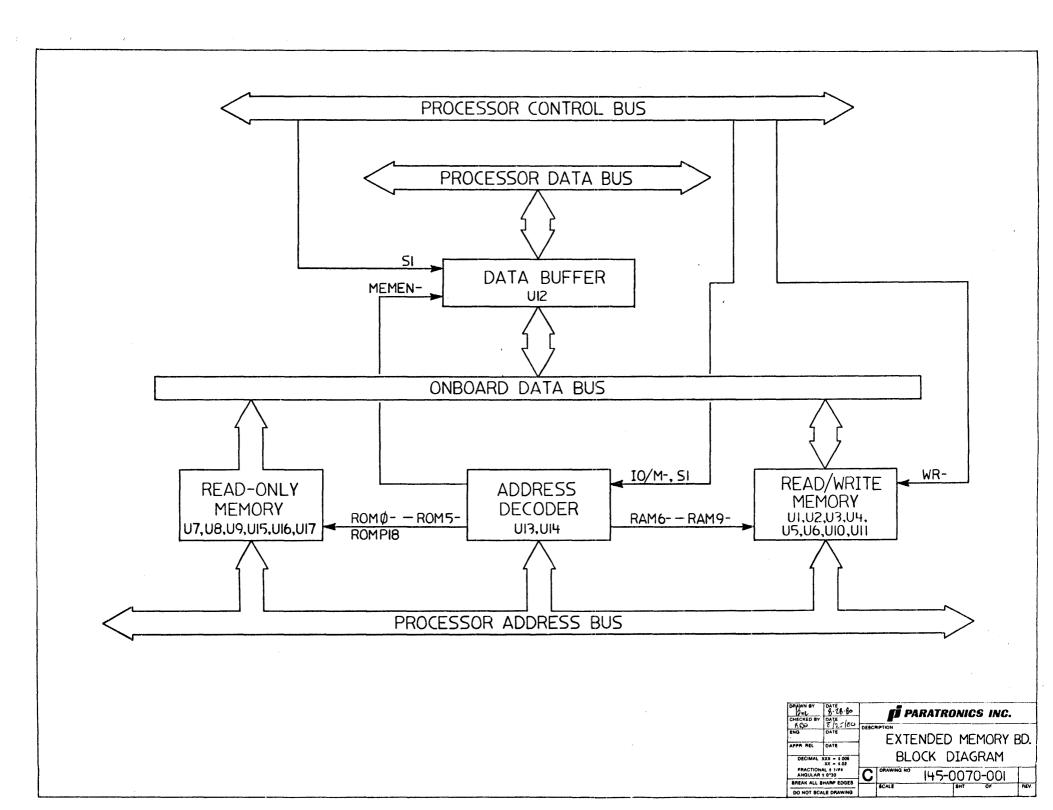

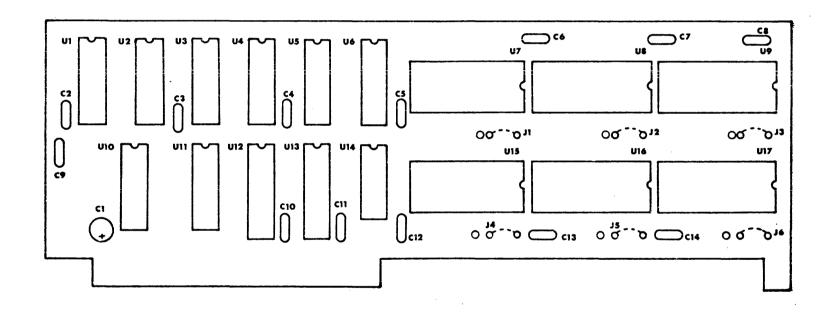

Extended Memory Boards #1 and #2 provide additional program storage ROM and working RAM for the Processor Board. They are identical in their potential memory capacity of 24K bytes of ROM and 4K bytes of RAM per board. In the PI 540, #1 contains 12K bytes of ROM and 4K bytes of RAM, and #2 contains somewhat less, depending on the configuration of the particular instrument.

The remaining four board positions in the Microcomputer Section are available for optional circuit boards such as the Serial Interface and GPIB Interface boards.

The <u>APPLICATIONS SECTION</u> is built up on the Function Motherboard, which has card guides, sockets, and interconnections for 7 circuit boards. In effect, these circuit boards, in conjunction with the Control Program, define the functions of the analyzer. They are devoted primarily to signal conditioning circuits, functional control circuits, and data collection memory.

The Applications Section in a full-feature PI 540 contains the following circuit boards (listed from front to rear):

| Slot           | Circuit Board                                       |

|----------------|-----------------------------------------------------|

| G (Front)<br>F | Spare, for expansion<br>State Memory Board, B Group |

| Ε              | State Control Board                                 |

| D              | State Memory Board, A Group                         |

| C              | Timing Control Board                                |

| В              | Timing Memory Board                                 |

| Α              | Waveform Board                                      |

Circuit board locations on the Function Motherboard are not interchangeable. Therefore, the boards and sockets are keyed so that a board can only be inserted in its designated socket. (A partial exception is that State Memory Boards A and B are identical, and either board can be installed in either memory board slot, but not in any of the other slots.)

The two <u>State Memory Boards</u>, which are identical as just noted, each contain enough RAM to collect 250 bits of data from each of 16 state input channels. They also contain input data latches, RAM for trigger and qualifier word comparison (software implemented), and circuits for generating various control signals.

The <u>State Control</u> <u>Board</u> contains circuitry that controls the collection of the state data that is stored on the State Memory Boards. This board also implements (for the state analysis mode) clock qualification, the 16 levels of trigger words, and all delay functions.

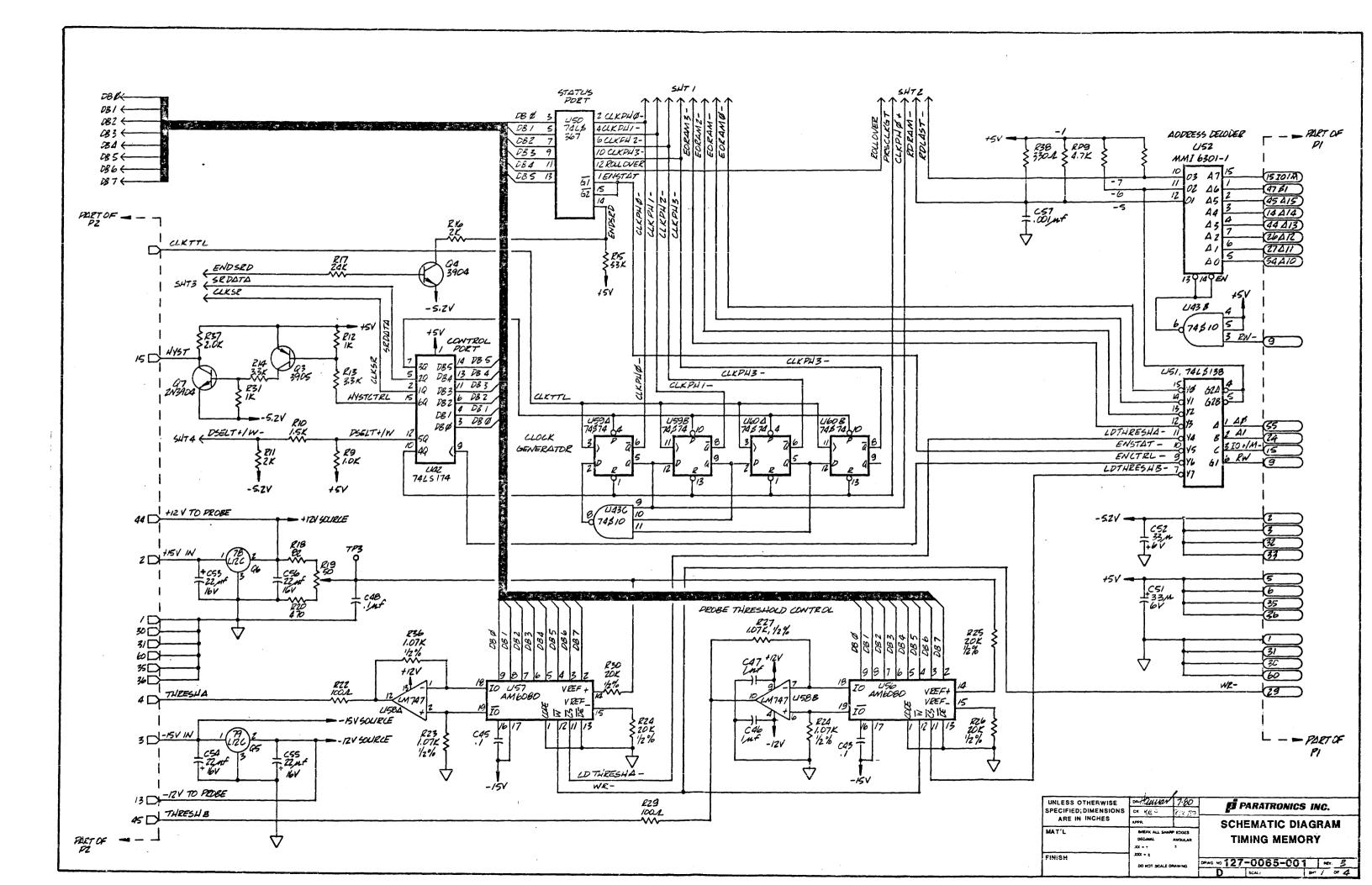

The <u>Timing Control</u> <u>Board</u> contains circuitry that controls the collection of the timing data that is stored on the Timing Memory Board. This board also generates the internal clock used for collecting timing and waveform data. And, for the timing analysis mode, this board controls clock selection, and the trigger delay functions.

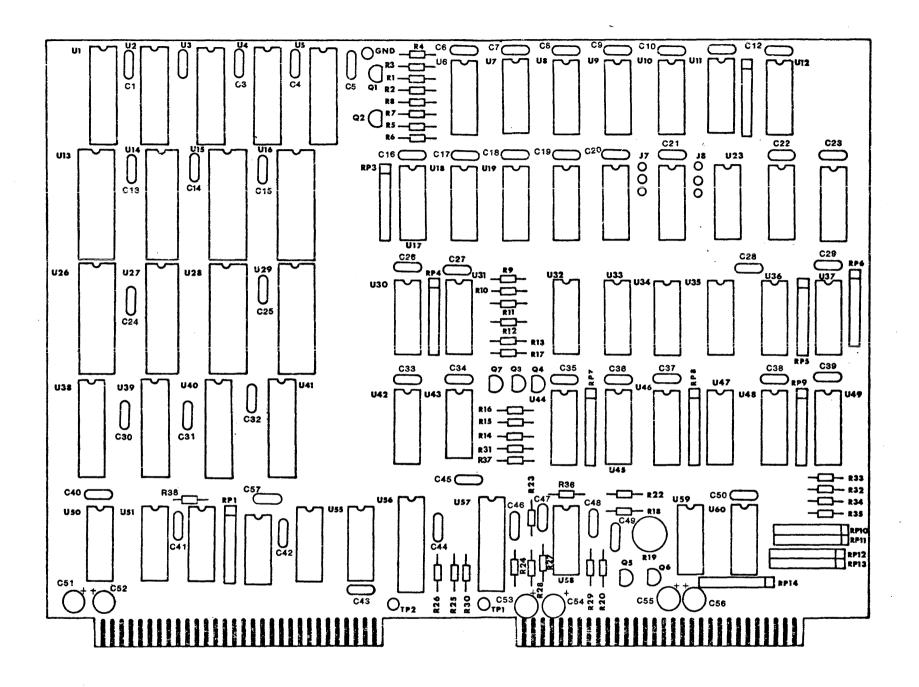

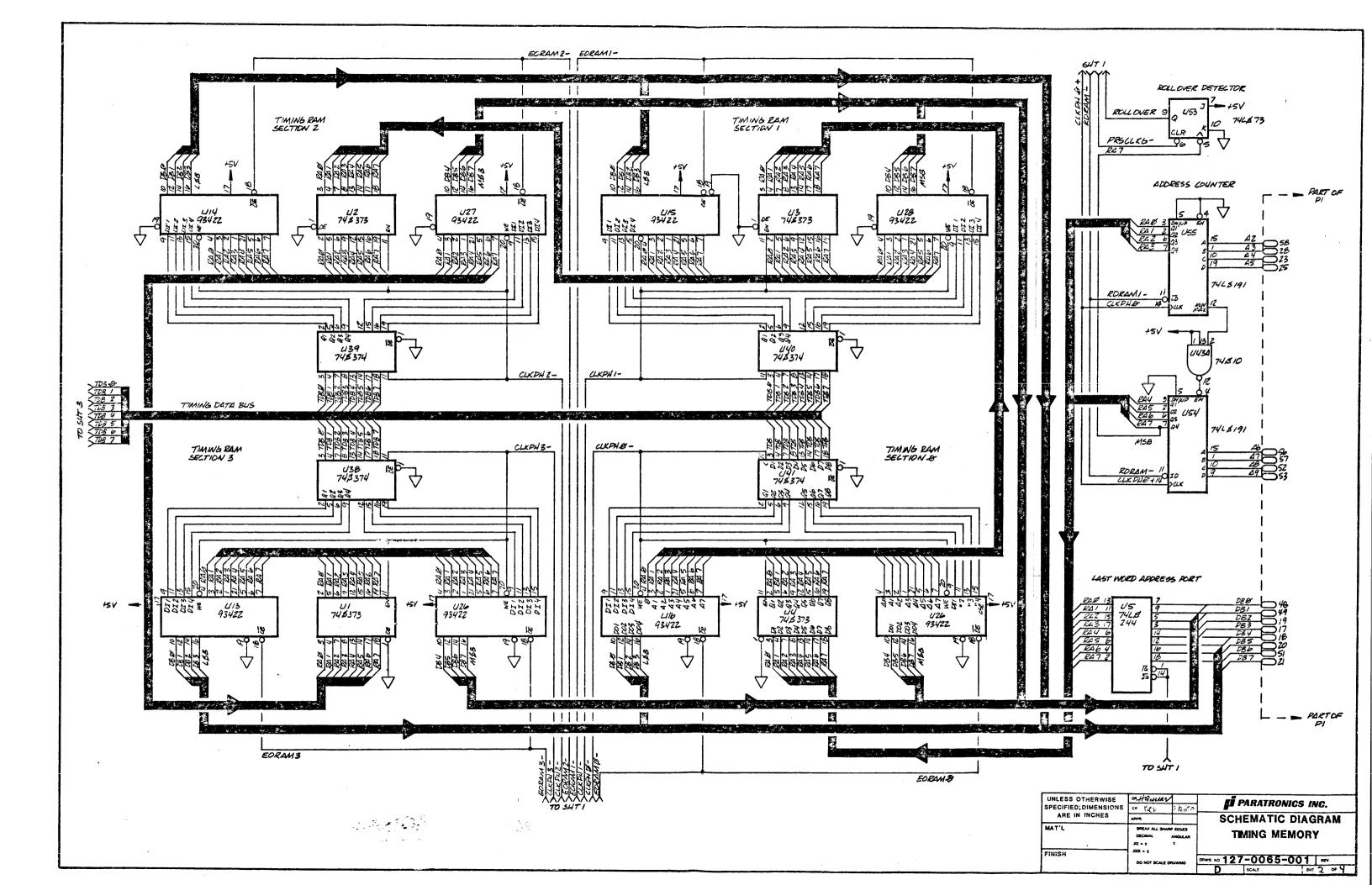

The <u>Timing Memory Board</u> contains a 1K-word x 8-bit RAM for storage of collected timing or waveform data. It also contains circuits that perform the glitch-capturing function, compare the incoming data with the arm and trigger words, and establish the voltage thresholds for the incoming timing channels.

The Waveform Board contains circuitry that samples data on the incomming waveform channel (using a clock signal obtained from the Timing Control Board) and converts the data samples to digital form. The digital data is stored in the memory on the Timing Memory Board. The Waveform Board also contains a 256 x 8-bit auxiliary video screen RAM. Once triggering has occurred, captured data is copied from the Timing Memory Board into this RAM in the course of the display manipulation that is under software and keyboard control. Circuitry on this board then converts the information in the auxiliary screen RAM into line-drawing video signals that are fed to the Video Display Board.

### 1.4 SELF-TESTS

The PI 540 provides several self-tests that can be useful in assessing the condition of the instrument. First, there is the automatic self-test that is performed every time power is turned on. Second, there is the series of self-tests that are evoked by holding down certain keyboard keys at the same time power is turned on. Third, there are the self-test probe ports on the back panel that are accessed through the Model 51A and Model 80 Probes by means of the Model 53 Self-Test Adaptors. Finally, there are the self-tests that can be performed with the Logic Analyzer Demo Card, Paratronics Inc. part number 143-0046-002.

# 1.4.1 Automatic Self-Test

The automatic self-test is performed during the first two seconds each time power is applied to the analyzer. This test goes through a set of performance checks of the PI 540 memories and other subsystems. All keyboard lights are lighted throughout the test to confirm their operation. The test also reads the power line frequency and sets the CRT vertical sync frequency to a matching 50 or 60 Hz. Although this automatic self-test does not provide an exhaustive check, it does offer a high confidence level that the analyzer is operating properly.

Successful completion of the test is announced by a short beep followed by a display of the Configuration Menu. If the test is not successful, the keyboard lights will remain on, there will be no beep, and there will be no display on the CRT. If the CRT vertical sync frequency cannot be set to approximate the power line frequency, a continuous beep will be emitted.

# 1.4.2 Keyboard Self-Tests

Each test in this series is initiated by holding down the specified key while turning the main power switch from OFF to ON, and keeping the key held down until the beep at the end of the automatic self-test is heard (about two seconds). At that point, the selected test begins. The available tests are as follows. (Unless otherwise noted, exit from the tests is made by pressing the CONFIG key.)

For the <u>CRT Alignment Check</u>, hold down the <u>"0" key</u>. This test is a fixed display of horizontal and vertical lines that are useful for evaluating and adjusting CRT alignment. (For details on using this test, refer to Display Module subsection 4.2.2.)

For the <u>Keyboard Check</u>, hold down the "1" <u>key</u>. This test can be used to check the performance of each key on the keyboard. To exit, turn off the power. (For details on using this test, refer to Keyboard subsection 3.2.)

For the <u>Video-RAM</u> and <u>Character-Set</u> <u>Check</u>, hold down the <u>"2" key</u>. This test verifies the integrity of the video refresh RAM and then uses the RAM to sequentially display a screenful of each character in the character set. To exit, turn off the power. (For details on this test, refer to Video Display Board subsection 5.4.)

For the <u>Program ROM Signature Check</u>, hold down the <u>"X" key</u>. This test performs a signature calculation on each program ROM. The CRT displays a tabulation of the ROM number, the starting address of the ROM, the correct signature, and the actual signature (which should, of course, match the correct one). If any signature is incorrect, it is displayed in reverse video.

Although, strictly speaking, the following items are not self-tests, they are given here because they are part of the series of key-hold-down-at-power-ON functions.

For the <u>CRT V-Sync Frequency Override</u>, hold down the <u>"5" key</u> or the <u>"6" key</u>. If the "5" key is held down, the CRT vertical sync frequency is set to 50 Hz. If the "6" key is held down, the setting is to 60 Hz. This setting is made after the Control Program's automatic setting and therefore remains in effect until power is turned OFF. (This function can be used to determine which of the two frequencies most closely matches the power mains frequency. For details, please refer to the Display Module subsection 4.2.1.)

For <u>Key-press Tone</u> <u>Delete</u>, hold down the <u>"T" key</u>. This turns OFF the beep tone that normally sounds when a key is pressed. The ERROR tone is <u>not</u> turned OFF. (If it is absolutely necessary for some reason, the ERROR tone can be turned OFF by setting the tone drive level to zero using variable resistor R1 on the Keyboard Interface Board. This requires disassembly of the keyboard. For details, please refer to the Keyboard section, 3.0.)

# 1.4.3 Self-Test Ports

There are two self-test ports located on the rear panel of the PI 540. One is labeled Data/Status, and the other is labeled Address. They consist of connectors which mate with the Model 53 Self-Test Adapters that attach to the Model 51A and Model 80 Probes. These ports provide access to the Processor Data Bus, certain status signals from the 8085 microprocessor, and the Processor Address Bus.

Either probe model can be connected (through a Model 53 Adapter) to either self-test port. The following tabulation lists, by channel number, the signals available to each of the probes from each of the self-test ports.

These signals can be used to investigate a certain aspect of the analyzer performance that is in question. Or they can be used to verify the overall performance of the analyzer by following the instructions given in section 6 of the Operator's Manual.

| MODEL 51A     | MODEL 80 | SELF-TEST   | PORTS     |

|---------------|----------|-------------|-----------|

| CHANNEL       | CHANNEL  | DATA/STATUS | ADDRESS   |

| 0             | 0        | AO          | DBO       |

| 1             |          | A1          | DB1       |

| 2<br>3        | 1        | A2          | DB2       |

| 3             |          | A3          | DB3       |

| 4             | 2        | A4          | DB4       |

| <b>4</b><br>5 |          | A5          | DB5       |

| 6             | 3        | A6          | DB6       |

| 7             |          | <b>A</b> 7  | DB7       |

| 8             | 4        | <b>A8</b>   | SO        |

| 9             |          | <b>A9</b>   | <b>S1</b> |

| 10            | 5        | A10         | I0+/M-    |

| 11            |          | A11         | INTA-     |

| 12            | 6        | A12         | SID       |

| 13            |          | A13         | SOD       |

| 14            | 7        | A14         | GND       |

| 15            |          | A15         | GND       |

| QTRIG (Q2)    | QCLK     | RD-         | I0+/M-    |

| QCLK (Q1)     | •        | IO+/M-      | RD-       |

| CLK           | CLK      | RW          | RW        |

# 1.4.4 The Logic Analyzer Demo Card

The Paratronics Logic Analyzer Demo Card, Part Number 143-0046-002, can be used to perform a comprehensive performance test of the PI 540 Logic Analysis System. A suitable procedure is given in the following paragraphs. All steps necessary for a comprehensive evaluation are presented, including some that do not require the Demo Card.

(This procedure assumes some familiarity with the operation of the PI 540 Analyzer. If necessary, please refer to the Operator's Manual, particularly to section 6.)

- a. Disconnect the power cord from the analyzer and visually inspect the <u>power fuse</u> and <u>voltage card</u> to determine that they are correctly installed for the current application. (For further details, please refer to the discussion of the Mains Module in the Chasis section, 2.1.) Reconnect the power cord.

- b. To check the <u>automatic CRT vertical sync setting</u>, use the "5"-key and "6"-key power-ON-hold-down functions to determine that the automatic setting is the one that produces the least mains-frequency interference with the CRT display. (For details, please refer to the Display Module subsection 4.2.1.)

- c. To evaluate the <u>Display Module</u>, turn the power ON while holding down the "O" key. Appraise the resulting CRT test pattern using the criteria presented in Display Module subsection 4.2.3, steps 5 through 10. If adjustments are needed, make them in accordance with the WARNING and instructions in the same subsection.

d. To verify the <u>contents</u> of the <u>program ROMs</u>, turn the power ON while holding down the "X" key. (For details, please refer to preceding subsection 1.4.2.)

To evaluate the <u>State Analyzer section</u>, connect two Model 51A Probes to the analyzer. Connect the A and B probe pods to edge connectors A and B, respectively, on the Logic Analyzer Demo Card. Set the probe Data Select switches to TRUE and the probe Threshold Select switches to TTL. Turn the analyzer power ON and proceed as follows:

e. Select the 32-CHANNEL STATE configuration and set up the menu as shown below.

### 32 CHANNEL STATE MENU

DISPLAY FORMAT: AAAAAAAA AAAAAAA BBBBBBBB BBBBBBBB

A HEX B HEX

CLOCK SELECT: A CHNL: 1 B CHNL: A QUALIFIERS: -AABB ET

CLOCK QUAL: 0040 0000 -0XXX X

OR OOOX XXXX -XXOX X

PRE-TRIG MEMORY (0-249): 000 WORDS

RESTART: OFF

TRIGGER:

0040 0000 -XXXX XX

**END**

- f. Test the <u>Signature function</u> by pressing RESET. When the STATE display appears, the signature should be 0D10 0A90.

- g. Test the Format function by pressing, in turn, the ASC, BIN, OCT, DEC, and HEX keys. Choose one of the data lines and confirm that the displays on that line are correct. (Start with the ASC display and scroll to a line that has all standard ASCII characters. Then switch to BIN, write down the bits, and work from there. Realize that DEC does not assume BCD, but uses straight binary conversion of the eight bits in the block. Also, OCT assumes a ninth MSB of 0 in each block.)

- h. Test the <u>Location</u> <u>function</u> as follows: Press the LOC key and then the E (End) key. The <u>memory</u> location of the display window should change from 000 at the top of the screen to +243 at the top of the screen, and the reverse-video LOC field should contain +243. Press LOC again, then B (Bottom). The memory location should return to 000 (which is Bottom in this setup because PRE-TRIG is 000).

- i. Test the <u>Scrolling function</u> as follows: Press and release the key marked with the green up-arrow. The display should step up one memory location. Hold down the up-arrow key for two seconds, then release. The data should scroll up continuously. Stop the scrolling by pressing either the up- or down-arrow key. Repeat these steps using the down-arrow key. The action should be similar, but down.

j. Test the <u>Repeat function</u> by holding down the RESET key for two seconds. The data collection should reset repeatedly at a rate of about once per second. The signature should remain constant at the value OD10 OA90. Exit from Repeat by pressing the STATE key. Press RESET once and check the signature again.

To test the <u>Hold-if-Not-Equal function</u>, perform the following steps  $\underline{k}$  through s.

- k. Press SAVE, then press ALT. The words MAIN and AUX should appear alternately about once per second at the upper left of the screen. The data should remain constant. (The data saved in AUX memory is the same as the data in MAIN memory.)

- m. Press MAIN to stop the alternating, then press HOLD \( \neq \). The data should disappear from the screen and the flashing word SAMPLING should appear. (The analyzer does not trigger because the data being sampled is equal to the data that was saved.)

- n. On the Logic Analyzer Demo Card, install a short to ground on the A-channel bit O. (<u>Leave</u> this short installed until otherwise instructed.) At the instant the short is made, the analyzer should trigger, and data and the flashing word HOLDING should appear on the screen.

- o. Press the DIFF key. Data words in the display that are the same as the saved data should drop back to half intensity; data words that are different should remain at full brightness.

- p. Press LOC, then D (Difference). Each time LOC and D are pressed, the data should scroll up so that the next <u>different</u> (full-brightness) word is at the top of the screen.

- q. On the Logic Analyzer Demo Card, remove the short to ground from A-channel bit 0 and install it on B-channel bit 7. (Leave this short installed until otherwise instructed.)

- r. Press HOLD  $\neq$ . The analyzer should retrigger and flash the word HOLDING. (Saved data is still in the AUX memory from step k.)

- s. Move the data so that there are both half- and full-intensity data words on the screen. Press ALT. The full-intensity (different) words should alternate back and forth between their MAIN and AUX values; the half-intensity words should not change.

To test the Restart and Restart- functions, perform the following steps  $\underline{t}$  through y.

t. Connect a Model 80 Probe to the Timing input of the analyzer, and connect the Timing pod to the B connector of the Demo Card in place of the B State pod. (Leave the B State probe connected to the analyzer but disconnected from the Demo Card.)

u. Select the 32 CHNL STATE/8 CHNL TIMING configuration and set up the STATE menu as follows:

# 32 CHANNEL STATE MENU

DISPLAY FORMAT: AAAAAAAA AAAAAAA BBBCCDDD DEEEEEEE

A HEX B OCT C DEC D BIN E ASC

CLOCK SELECT: A CHNL: B CHNL: A QUALIFIERS: -AABB ET

CLOCK QUAL: OFF

OR OFF

PRE-TRIG MEMORY (0-249): 010 WORDS

RESTART: OFF

TRIGGER:

| 0      | 0040 X X XXXX XX -XXXX XX |                    |

|--------|---------------------------|--------------------|

| 1 THEN | 0041 X X XXXX XX -XXXX XX | ON 0257 CLOCKS     |

| 2 THEN | 0042 X X XXXX XX -XXXX XX | BEFORE 0002 CLOCKS |

| 3 THEN | 0043 X X XXXX XX -XXXX XX | AFTER 1000 CLOCKS  |

| 4 THEN | 0044 X X XXXX XX -XXXX XX | OCCURS 0020 TIMES  |

| 5 THEN | 0045 X X XXXX XX -XXXX XX | NOT ON 0002 CLOCKS |

| END    |                           |                    |

|        |                           |                    |

- v. Press the RESET key. The signature of the collected data should be 083D 0A07.

- w. Return to the STATE menu and set up the RESTART word as follows:

RESTART: XXXX O X XXXX -XXXX XX

- x. Press the RESET key. The analyzer should not trigger, and the stack level should remain at 0 (announced on the display).

- y. Return to the STATE menu and select RESTART- (the .NOT. function of RESTART). Press RESET. The analyzer should now trigger and the data signature should be 083D 0A07 (the same as in step v).

To evaluate the <u>Timing Analyzer section</u>, select the TIMING menu (still in the 32 CHNL STATE/8 CHNL TIMING configuration) and set up the parameters as shown in the following display. Then perform the remaining steps.

### 8 CHNL TIMING/STATE MENU

EXT CLOCK CLK QUAL: 0

TRIGGER WHEN

TRIG (0,1,X): 11011000 OFF NONE

INPUT MODE (S,L): SSSSSSSS

PRE-TRIGGER (0-9): 10%

DISPLAY ORDER (0-7,X): 76543210

DISPLAY POLARITY (+,-): ++++++

THRESHOLD: CH 0-3,Q,CK CH 4-7 HYSTERESIS (-6.4V - +6.35V) +1.60 +1.60 ON

z. Press RESET to obtain a data display. Then, by pressing the appropriate keys, test the <u>left/right motions</u> and <u>position read-outs</u> of: the cursor, the expansion indicator, and the display window.

- aa. To test the Expansion function, press in turn X2, X5, X10, and X20. The data in the display window (that is, the data on the screen) should expand accordingly. The location in memory of the expanded data should be marked by a reverse-video block on the display's time scale. (NOTE: The selected magnification will always be used for the entire display window. The left boundry of the expanded window will fall at the expansion indicator provided the right boundry would not thereby extend past location 1000. Otherwise, the right boundry of the expanded window will fall at location 1000 and the window will extend to the left as necessary.)

- ab. Test the Arm, Trigger, and Delay functions as follows: Position the cursor at location 000 (clocks, words). The data read-out (just to the right of the data lines) for location 000 should be the arm word, or 80. (This is because the arm word is 100 clocks before the trigger word, and with pretrigger at  $10\% \times 1000$  words, the trigger word is at 100.) Move the cursor to location 100. The data read-out should be the trigger word, or D8.

- ac. Test the <u>Correlation function</u> as follows: Press the SAVE key, then the COR key. The correlation figure displayed at the right of each channel should be 1.000 for all eight channels.

On the Demo Card, remove the short to ground from B-channel bit 7 and install it on B-channel bit 5.

Press RESET, then COR. The correlation figures on three of the channels should change as follows:

Channel 3, 0.504 Channel 4, 0.760 Channel 5, 0.504

ad. Test the <u>Alternate function</u> by pressing the ALT key. The data in channels 3, 4, and 5 should change as the display alternates back and forth between MAIN and AUX.

ae. To test the Arm, Trigger, and Delay functions with internal clock, return to the Timing menu and change CLOCK and PRE-TRIGGER to

1mS CLOCK PRE-TRIGGER: 20%

Press RESET. Under these menu conditions, the data read-out at cursor position 100 should be the arm word, 80; and the data read-out at cursor position 200 should be the trigger word, D8.

af. To test the <u>Timing Linkage function</u>, return to the Timing menu and change the delay and the ARM LINKAGE to

TRIG OCCURS > 2500 CLOCKS AFTER FIRST ARM

LINKAGE

ARM . . . . . . . . . . . . NONE

Return to the State menu. As shown below, add a Timing link to the trigger word in the 5th trigger level.

Press RESET. Because of the time delay set into the Timing menu and the Timing linkage set into the State trigger-level 5, the progress announcements at the bottom of the State display should make evident a 2.5-second delay at STATE: STACK LEVEL 5. (There should also be a 1-second delay at level 3 as specified in the State menu.)

| 2.0 CHASSIS, MOTHERBOARDS, AND POWER SUPPLY |

|---------------------------------------------|

|                                             |

|                                             |

|                                             |

|                                             |

# 2.1.0 CHASSIS

# 2.1.1 INTRODUCTION

The chassis provides a strong supporting structure for attachment of the Folding Keyboard, the Display Module, the Microcomputer subassembly, and the Applications subassembly. The cover, which is considered a part of the chassis, encloses the top and two sides, giving complete protection to the inner components and adding to the structural strength of the completed assembly.

# 2.1.2 FUNCTIONAL DESCRIPTION

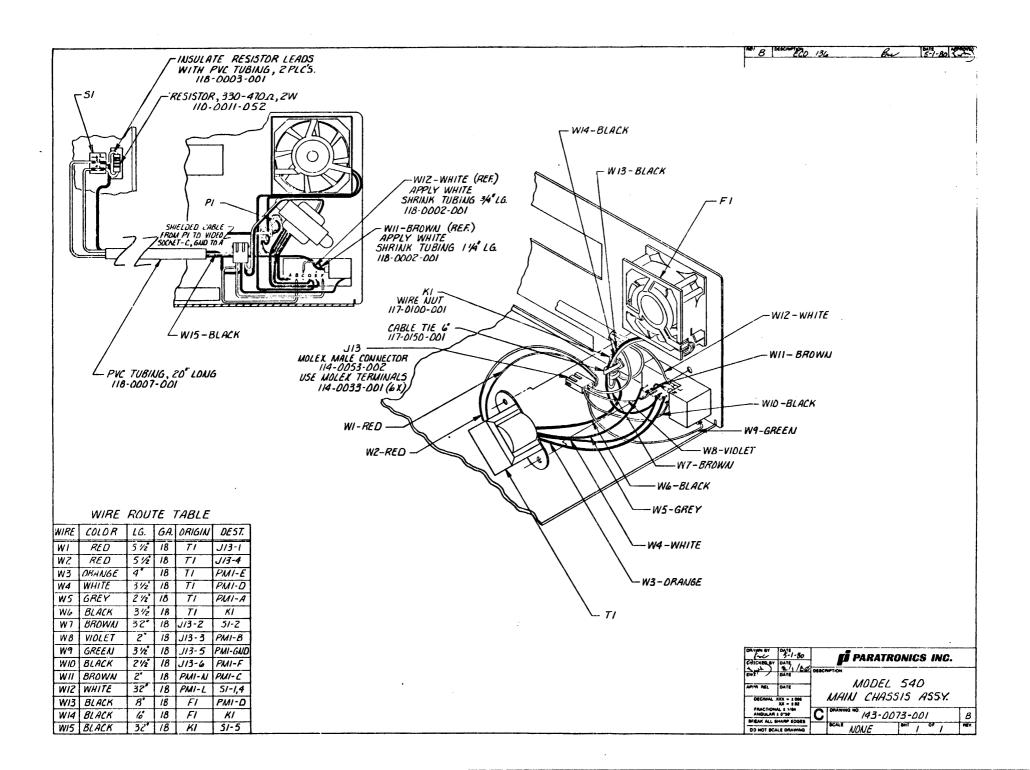

When appropriate during the following discussion, please refer to the drawings, interconnection diagram, and parts list that are included at the end of this section. Also, tables of connector pins versus signal names for all motherboard connectors are provided in section 15 along with an alphabetical list of all interboard signals. And, should the need arise, a Glossary in section 16 offers explanations for acronyms or terms that may be unfamiliar.

The units that will be discussed as part of the chassis group are the chassis itself, the cover, the carrying handle, the Mains Module, the cooling fan, the auxiliary power transformer, and the interconnecting wiring.

The <u>Chassis</u> consists of a heavy guage aluminum bottom plate bent up at a right angle at the rear to form an integral back plate. The front of the bottom plate is attached to a heavy cast-aluminum front plate. The upper corners of the front plate are joined to those of the back plate by longitudinal tie rods of 3/8 diameter aluminum. There is a large rectangular hole in the front plate through which the CRT screen is viewed. A plastic face plate is inset into the front plate and covers the entire front surface. This face plate protects the CRT and is lightly tinted to enhance the contrast of the CRT display. The main power switch is attached to the rear of the front plate, and its handle extends through a hole in the front plate and face plate.

The Folding Keyboard attaches by hinges to the bottom edge of the front plate. The Keyboard folds up against the front plate and is secured by two latches that are attached to the top edge of the front plate.

The Display Module is mounted to the bottom plate by four threaded studs set into the bottom plate. The Microcomputer subassembly is mounted to the bottom plate by five flathead screws through the bottom plate. The Applications subassembly is mounted to the bottom plate by four screws into short threaded spacers set into the bottom plate.

The cooling fan fastens to the back plate by four screws through the back plate. The auxiliary power transformer fastens to the back plate by two threaded studs set into the back plate. The Mains Module mounts into a rectangular hole in the back plate with snap-in fasteners. The BNC connector for external video output mounts in a hole in the back plate. When present, connectors for the optional serial and GPIB interfaces mount into rectangular holes in the back plate with screws through the back plate. There are seven round clearance holes in the back plate through which BNC connectors, mounted

on the Applications subassembly, extend. There is also a rectangular clearance hole in the back plate through which a 50-pin ribbon connector extends when present. This connector is for interface expansion and mounts on the Applications subassembly.

WARNING: DISCONNECT THE AC POWER CORD AT THE BACK OF THE CHASSIS BEFORE REMOVING THE COVER. THE DISPLAY MODULE CONTAINS A VERY HIGH VOLTAGE OF 9 kV WHICH CAN BE LETHAL. EXTREME CAUTION MUST BE USED WHENEVER POWER IS APPLIED TO THE PI 540 WITH THE COVER REMOVED.

The <u>cover</u> folds around the top and two sides of the instrument. It overhangs the back plate 1/4 inch and fits into a 3/8-inch recess in the front plate. The bottom edges bend around underneath the bottom plate on each side and overlap it by 3/4 inch. The cover is held in place by six screws, three on each side, that pass through holes in these overlapping flanges and the bottom plate and thread into captive nuts on the inside surface of the bottom plate. There are vent slots in strategic places in the sides of the cover for fan air intake. There is a larger slot in the side of the cover that provides access to the Probe connectors on the Applications subassembly.

The <u>carrying handle</u> attaches by pivot pins to the side edges of the front plate. When the analyzer is in use, the handle can be folded back underneath the bottom plate to act as a stand. This props up the front of the instrument so the keyboard rests at a convenient working angle.

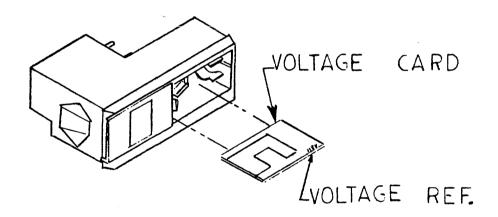

The <u>Mains Module</u> (please refer to figure 2.1-1 and to the chassis wiring diagram) is mounted into a rectangular cutout in the back plate and held in place by snap-in fasteners attached to the sides of the Module.

A voltage card in the Mains Module is used to select the power mains voltage with which the instrument is to be supplied. (The sliding cover for this voltage card can only be opened when the power cord is unplugged from the Module.) Voltage designations are etched in copper near the edges of the voltage card. The voltage designation that is visible on the upper rear edge of the card when it is in place is the voltage for which the instrument is programmed.

WARNING: BEFORE APPLYING POWER TO THE PI 540, MAKE CERTAIN THAT THE PROGRAMMED MAINS VOLTAGE CORRESPONDS TO THE VOLTAGE BEING USED. OTHERWISE SERIOUS DAMAGE TO THE INTERNAL POWER SUPPLY MAY RESULT.

To change the voltage programmed, remove the card, change its orientation, and reinsert it. The voltages available for selection are:

| Voltage<br>Programmed | Nominal<br><u>Mains</u> Voltage | Nominal<br>Mains Frequency |

|-----------------------|---------------------------------|----------------------------|

| 100 V ac              | 95—110 V ac                     | 50 or 60 Hz                |

| 115 V ac              | 110—120 V ac                    | 50 or 60 Hz                |

| 230 V ac              | 220—240 V ac                    | 50 or 60 Hz                |

The power-mains fuse is located in the Mains Module just above the voltage card. The rating of the fuse depends on the voltage programmed. The required fuse ratings are as follows:

| Programmed<br>Mains Voltage | Fuse Rating  |

|-----------------------------|--------------|

| 100 or 115 V                | 3 A, 250 V   |

| 230 V                       | 1.5 A, 250 V |

The <u>auxiliary transformer</u> is mounted by threaded studs set into the back plate just above the Mains Module. The primary of this transformer acts as an autotransformer to supply a nominal 115 V ac to the fan motor regardless of the programmed mains voltage. The secondary supplies a nominal 17 V ac (also regardless of programmed mains voltage) to the Power Supply for an auxiliary supply circuit.

The  $\underline{\text{cooling}}$   $\underline{\text{fan}}$  is mounted in a 3-inch square hole in the back plate and is supplied with  $\overline{115}$  V ac power from the auxiliary transformer. There are air vent slots in the cover; one group beside the front of the Microcomputer subassembly and one group beside the Applications subassembly. The fan draws air in through these vent slots and exhausts it from the fan mounting hole. This air flow lowers operating temperatures within the cabinet to safe levels.

WARNING: IF THE FAN IS NOT FUNCTIONING, DO NOT OPERATE THE PI 540 WITH THE COVER ON. DOING SO MAY RESULT IN SERIOUS DAMAGE TO COMPONENTS THROUGHOUT THE INSTRUMENT. HOWEVER, EXTREME CAUTION MUST BE USED WHEN OPERATING THE PI 540 WITHOUT THE COVER BECAUSE OF LETHAL HIGH VOLTAGE USED IN THE DISPLAY MODULE. SUCH OPERATION SHOULD ONLY BE UNDERTAKEN BY EXPERIENCED MAINTENANCE PERSONNEL FOR MAINTENANCE PURPOSES.

The <u>interconnecting wiring</u> is shown in the wiring diagram at the end of this section. All interconnections to the Display Module, Microcomputer subassembly, and Application subassembly are made through connectors, so any of these units can be removed without unsoldering wires.

# 2.1.3 <u>DRAWINGS</u>, <u>DIAGRAMS</u>, & <u>PARTS</u> <u>LIST</u>

Drawings, diagrams, and parts list for the Chassis are contained on the following pages.

# 2.2.0 MOTHERBOARDS

# 2.2.1 INTRODUCTION

There are two motherboards in the PI 540; the Microcomputer Motherboard and the Function Motherboard. These motherboards are relatively large printed circuit boards which contain sockets, card guides, and supporting structure for the numerous individual PC boards that constitute the analyzer.

# 2.2.2 FUNCTIONAL DESCRIPTION

When appropriate during the following discussion, please refer to the schematic diagrams, board layouts, and parts lists which are included at the end of this section. Also, tables of connector pins versus signal names for all motherboard connectors are provided in section 15 along with an alphabetical list of interboard signals. And, should the need arise, a Glossary in section 16 offers explanations for acronyms or terms that may be unfamiliar.

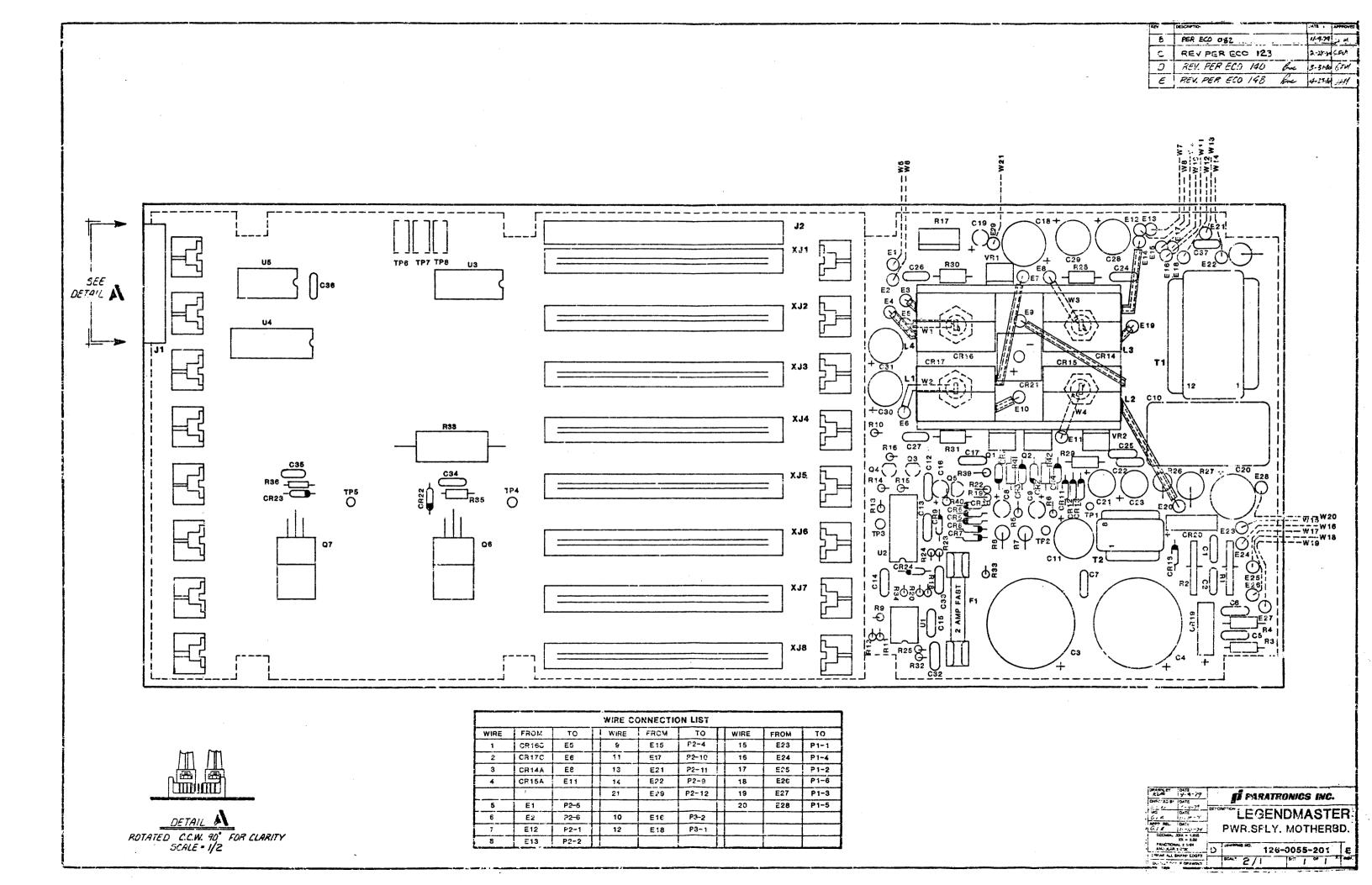

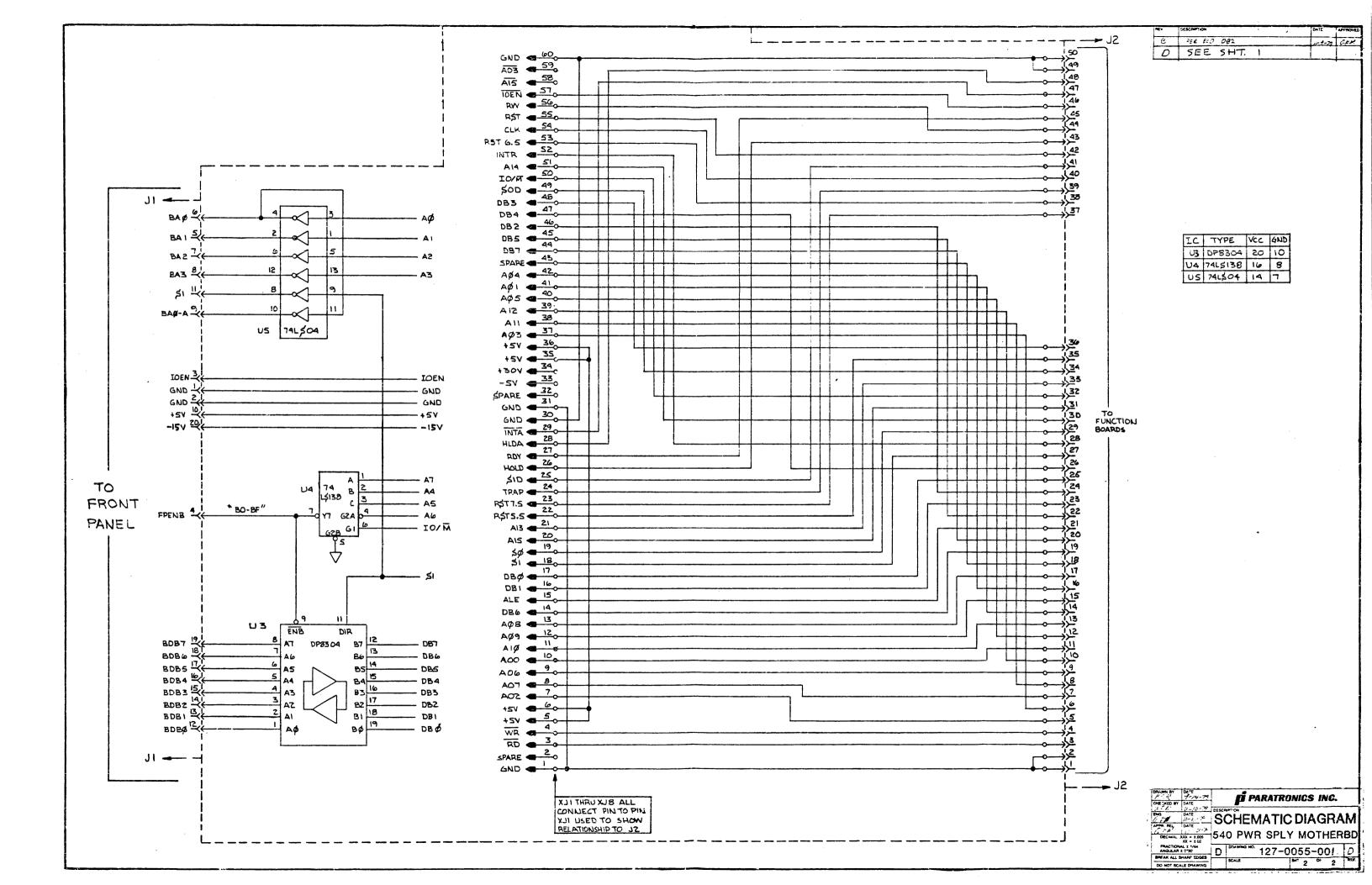

The two motherboards will be discussed separately in the following subsections. Also, the Power Supply, whose PC board is an integral part of the Microcomputer Motherboard but whose function is entirely separate, will be discussed separately in section 2.3.

# 2.2.2.1 Microcomputer Motherboard

The Microcomputer Motherboard contains sockets, card guides, and interconnections for eight circuit boards. Four of these board positions are available for optional PC boards such as the Serial Interface Board and the GPIB Interface Board. The remaining four positions are occupied by four PC boards that constitute the Microcomputer Section of the analyzer.

The slot assignments for individual PC boards are interchangeable on this motherboard. But typically, the board complement is arranged as follows (with slot 1 at the top of the motherboard):

| Slot | <u>Circuit</u> <u>Board</u> |

|------|-----------------------------|

| 1    | Video Display Board         |

| 2    | Processor Board             |

| 3    | Extended Memory Board #1    |

| 4    | Extended Memory Board #2    |

| 5-8  | (available for options)     |

The PC board sockets and card guides are located on the forward 2/3 of the motherboard. The rear 1/3 is occupied by the Power Supply, which is discussed in section 2.3. Some forward motherboard area not occupied by sockets and wiring is allocated to the Power Supply overvoltage protection circuits. The components (Q6, Q7, and the other items grouped around them) are shown on the board layout drawing. The circuits are shown on the Power Supply schematic and discussed in the Power Supply section, 2.3. Also, Power

Supply test points TP6, 7, and 8 are placed at the top edge of the forward part of the board.

Some additional area in the forward part of the board is allocated to driver circuits for the keyboard connecting cable. The components are U3, U4, U5, and C36, shown on the board layout drawing. This circuitry is shown on the motherboard schematic but is discussed in the Keyboard section, 3. The signals that must be sent to the Keyboard are fed to a connector near the front edge of the board. This connector mates with another on a flat ribbon cable that comes from the Keyboard.

The PC board sockets are interconnected in an arrangement called the PI Standard Bus (shown in the schematic and used in other PI instruments as well as the PI 540). Signals that must be sent to the Function Motherboard are fed to a connector near the top edge of the Microcomputer Motherboard. This connector mates with another on a flat ribbon cable that interconnects the two motherboards.

The motherboard is supported by a sheet metal shell which includes a vented case that completely encloses the component side of the Power Supply portion of the board. The noncomponent side of the Power Supply portion of the board is protected by a sheet of plastic mounted on short plastic spacers. The sheet metal shell fastens to the chassis bottom plate with five flathead screws through the bottom plate. (Instructions for dismounting this mother-board subassembly from the chassis bottom plate are given in the Power Supply section, 2.3.)

# 2.2.2.2 <u>Function Motherboard</u>

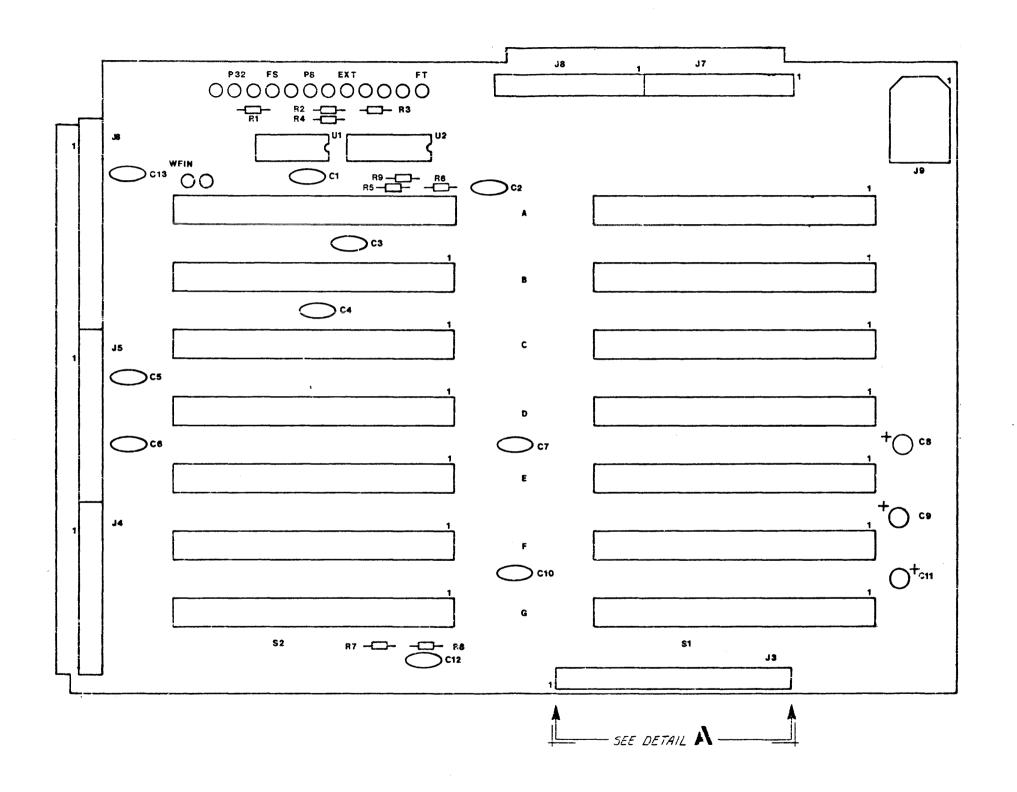

The Function Motherboard contains sockets (two per circuit board), card guides, and interconnections for seven circuit boards. One of these board positions is available for future expansion. The remaining six positions are occupied by six PC boards that constitute the analyzer's Applications Section. These six circuit boards, in conjunction with the Control Program, define the functions of the analyzer.

The slot assignments for individual PC boards are not interchangeable on this motherboard. One socket in each socket pair is keyed so that only the correct circuit board can be inserted. The Applications Section of a full-feature PI 540 contains the following circuit boards (listed front to rear):

| Slot                  | <u>Circuit</u> <u>Board</u>                                                                                                           |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (Front) G F E D C B A | (for expansion) State Memory Board B State Control Board State Memory Board A Timing Control Board Timing Memory Board Wayeform Board |  |  |

Two sheet metal end plates, as wide as the motherboard and extending upward to the height of the inserted circuit boards, are fastened to the motherboard at front and rear. Two cross pieces on each side, running fore and aft, are attached to the end plates and support the card guides. The result is a rigid card-cage assembly.

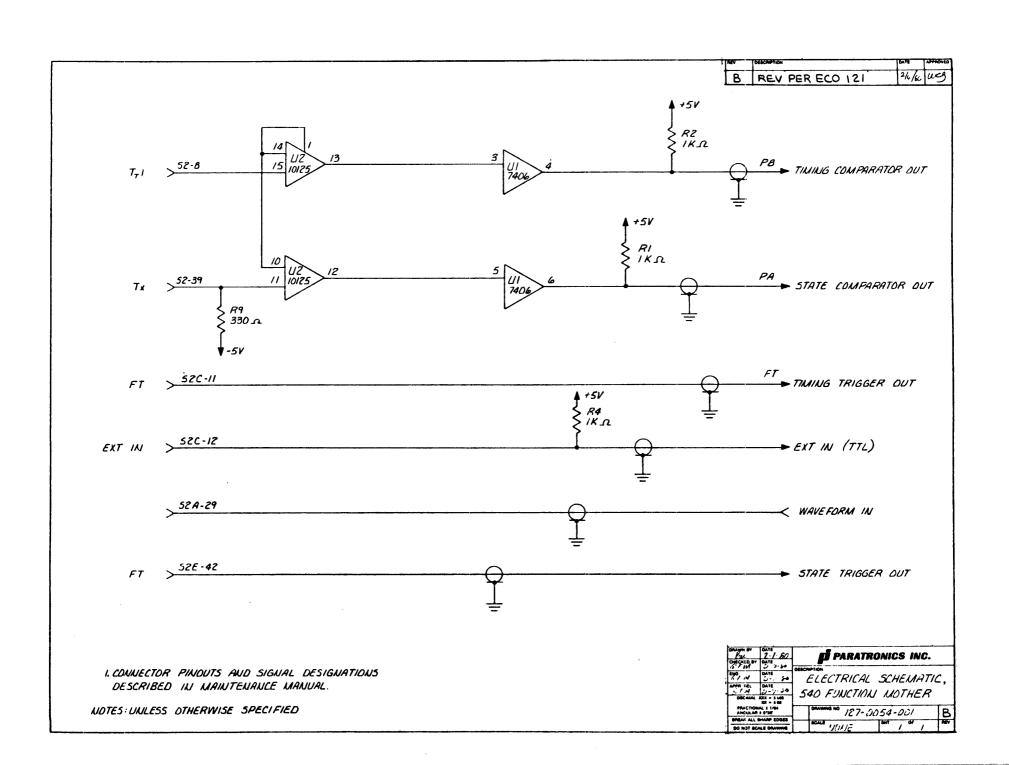

Seven BNC female connectors are mounted on the rear end plate and extend through clearance holes in the chassis back plate. One of these connectors is a spare, and the remaining six are for the following signals:

Timing Comparator Out State Comparator Out Timing Trigger Out State Trigger Out External Trigger In Waveform Probe In

Driver circuits for the two Comparator outputs and a pullup resistor for the External Trigger input are located near the rear edge of the motherboard. These components are shown on the board layout drawing and on the schematic. If the analyzer is equipped with an expansion interface, the 50-pin ribbon connector for that interface is also mounted on the rear end plate and extends through a clearance hole in the chassis back plate.

There are several round clearance holes in the front end plate that, when the Applications circuit boards are removed, provide access to maintenance adjustments on the Display Module.

The Function Motherboard subassembly fastens to the chassis bottom plate with four screws into short threaded spacers set into the bottom plate.

# 2.2.3 SCHEMATICS, BOARD LAYOUTS, & PARTS LISTS

The schematic diagrams, board layouts, and parts lists for the mother-boards are contained on the following pages.

# 2.3.0 POWER SUPPLY

# 2.3.1 INTRODUCTION

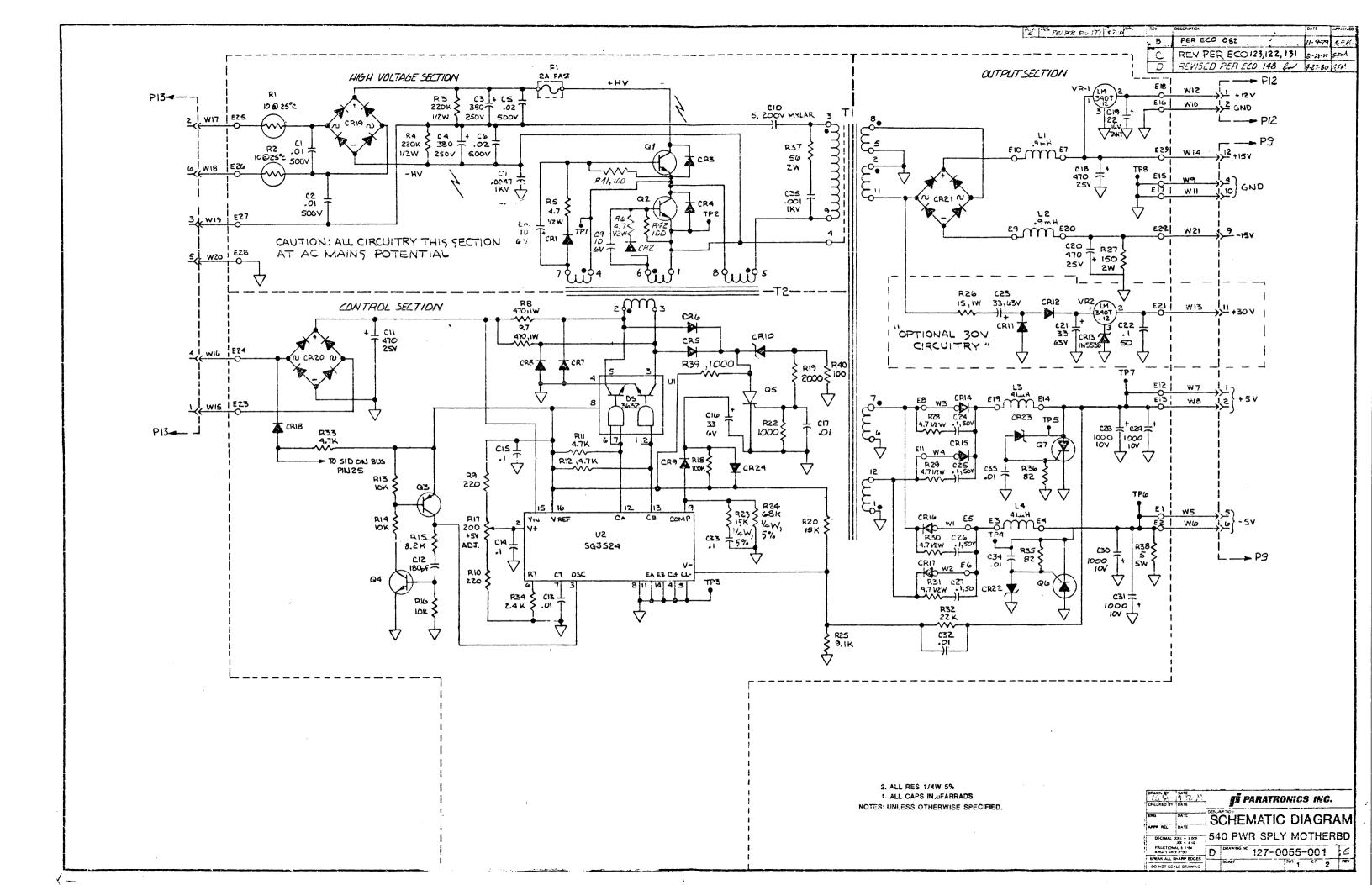

The Power Supply is an integral part of the Power Supply Motherboard and occupies the rear 1/3 of the board area, directly behind the Microcomputer Section. The Power Supply is a pulse-width modulated, half-bridge, 20 kHz switching circuit operating directly off the ac power line. It supplies  $\pm 5$  V and  $\pm 15$  V to the Keyboard, Applications, and Microcomputer Sections, and it supplies  $\pm 12$  V to the Display Module. Also, it provides very effective over-voltage and overcurrent protection for both the Power Supply itself and the circuits that it supplies.

# 2.3.2 FUNCTIONAL DESCRIPTION

When appropriate during the following discussion, please refer to the schematic diagram, board layout, and parts list which are included at the end of this section. Also, tables of connector pins versus signal names for all motherboard connectors are provided in section 15 along with an alphabetical list of all interboard signals. And, should the need arise, a Glossary in section 16 offers explanations for acronyms or terms that may be unfamiliar.

As shown on the schematic diagram, the major functional units of the Power Supply circuit are the High Voltage Section, Control Section, and Output Section. These units are discussed further in the following subsections.

WARNING: THIS POWER SUPPLY CIRCUIT IS CONNECTED DIRECTLY TO THE AC MAINS WITH NO INTERVENING ISOLATION TRANSFORMER. IT CONTAINS LETHAL VOLTAGES AND ENERGY STORAGE UNITS. ONLY QUALIFIED SERVICE PERSONNEL FAMILIAR WITH LINE-OPERATED SWITCHING POWER SUPPLIES SHOULD UNDERTAKE SERVICE OF THIS SUPPLY, AND THEN ONLY WITH THE ISOLATING TEST SETUP DESCRIBED IN THE FOLLOWING SUBSECTION, 2.3.2.1. FAILURE TO OBSERVE THESE PRECAUTIONS MAY RESULT IN SERIOUS INJURY OR DEATH.

# 2.3.2.1 <u>Test Setup</u>

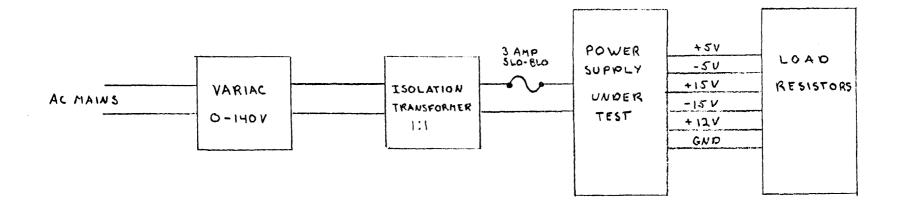

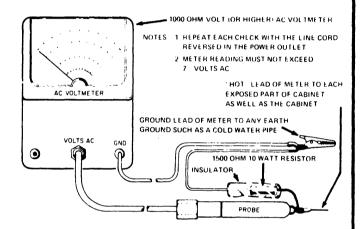

The 110 or 220 Vac input power is fed directly from the mains to the CR19 rectifier circuit without an intervening isolation transformer. Therefore, before any test equipment is connected to the High Voltage Section, it is essential that an isolation transformer be incorporated in the test setup as shown in figure 2.3-1 which is in subsection 2.3.3.

WARNING: MEASUREMENTS OR TESTS UNDERTAKEN WITHOUT THE USE OF AN ISOLATION TRANSFORMER AS SHOWN IN FIGURE 2.3-1 MAY RESULT IN EXTENSIVE DAMAGE TO EQUIPMENT OR SERIOUS INJURY OR DEATH TO PERSONNEL.

To gain access to the Power Supply and prepare it for service, proceed as follows (please read the entire procedure once before taking action):

- a. Disconnect the power cord.

- b. Close and latch the keyboard. Stand the analyzer on the keyboard end and remove the cover. Return the analyzer to the horizontal position.

- c. At the Video Display Board, disconnect the video cable to the Display Module, and, if installed, disconnect the flat cable to the Waveform Board. Remove the holddown bar and all the circuit boards from the Microcomputer Section

- d. Disconnect the 50-conductor flat cable from the top of the Micro-computer Motherboard. Disconnect plug P12 in the 2-conductor cable running from the rear of the Power Supply to the Display Module.

- e. Remove the three rear circuit boards from the Applications Section for later access to the P9 power supply plug connected to the rear of the Function Motherboard.

- f. Stand the analyzer on its rear feet and remove the five flathead screws that hold the Microcomputer Motherboard subassembly to the analyzer bottom plate. While giving support to the loosened subassembly, return the analyzer to the horizontal position.

- g. Being careful of the keyboard cable still connected to the front of the motherboard, swing the subassembly slightly outward at the rear to gain access to P9 on the Function Motherboard and P13 in the small cable to the Mains Module. Disconnect these two plugs.

- h. Swing the subassembly out a little more and slightly to the rear, and disconnect the keyboard flat cable. Move the subassembly clear of the analyzer and place it bottom-up on the work bench.

- i. Remove the white plastic cover from the Power Supply end of the motherboard, being careful to save the four screws and plastic spacers that held the cover away from the board.

- j. The entire sheet metal structure is spotwelded together and comes off as one piece. Remove the remaining four screws holding the motherboard to the sheet metal. Lift the motherboard free and carefully place it bottom-down on a soft, insulating pad on the bench.

CAUTION: Abnormal voltages will be produced unless some current is drawn from the Power Supply. But do not risk damage to valuable circuit boards by using the analyzer as a test load for the sake of convenience. Use resistors as suggested in the following paragraph. (Note that no load is needed on the +12 V supply unless it is specifically under investigation)

k. To load the Power Supply outputs, obtain a mating connector for P9 (see parts list) and make an adapter with which to connect the load resistors between the various outputs and ground returns. For your convenience, suitable load resistance values are given in the following tabulation:

|                                     | Rating | Resistance | Current | <u>Output</u> |

|-------------------------------------|--------|------------|---------|---------------|

| (R38, built in)<br>(no load needed) | 5 W    | 5 ohms     | 1 A     | +5 V          |

|                                     |        |            | 1 A     | -5 V          |

|                                     |        |            |         | +12 V         |

|                                     | 2 W    | 150 ohms   | 100 mA  | +15 V         |

|                                     | 2 W    | 150 ohms   | 100 mA  | -15 V         |

m. To bring primary and auxiliary power to the Power Supply, obtain a matching plug and socket set for P13 and make a jumper cable. Use this cable to bring power to P13 from the Mains Module and auxiliary transformer via S13. Connect the Mains Module through an ISOLATION TRANSFORMER to the power mains. PLEASE SEE PRECEDING WARNING NOTICES!

# 2.3.2.2 High Voltage Section

The High Voltage Section consists of: CR19, a GE PD-80 bridge rectifier; Q1 and Q2, both Motorola MJE13005 power switching transistors; CR1,2, both 1N3600 diodes; CR3,4, both 1N4008 diodes; transformers T1 and T2; thermistors R1 and R2: and various resistors and capacitors.

This circuitry converts a nominal 100, 110, or 220 Vac, 50 or 60 Hz mains voltage to a center-tapped nominal ±162 Vdc. This dc voltage is converted (by the action of Q1, Q2, T2, and the Control Section) to a constant-frequency, pulse-width modulated, ac voltage across T1. The output voltages at the secondaries of T1 are a nominal 5 and 15 Vac rms at a nominal frequency of 20 kHz.

Input from the power mains is fed directly to the CR19 rectifier with no intervening isolation transformer. Consequently, all components within the High Voltage Section are at mains potential! PLEASE SEE PRECEDING WARNING NOTICES! A Mains Module, shown on the Chassis schematic diagram in section 2.1, contains a voltage card that is used to select the ac mains voltage that will be used to power the analyzer. The three selection options are 100, 110, and 230 Vac. (Please refer back to figure 2.1-1 in Chassis section 2.1.)

If a mains voltage of 230 Vac is selected, it is applied across input terminals E25 and E26 via connector pins P13-2 and P13-6. With this connection, CR19 acts as a full-wave bridge rectifier and produces a nominal 325 Vdc across filter capacitors C3 and C4 connected in series. The junction of C3 and C4 is a centertap of the 325 Vdc, providing  $\pm 162$  Vdc for the switching circuit and transformer T1. R3 and R4 stabilize the centertap and act as bleeders. C5 and C6 are for EMI reduction. Fuse F1, a 2 A fast-blow type, provides circuit board protection in case Q1 or Q2 shorts out (any failure of Q1 or Q2 will happen faster than the fuse can blow).

If a mains voltage of 100 or 110 Vac is selected, it is applied across input terminals E25 and E27 via connector pins P13-2 and P13-3. With this connection, CR19 acts as a full-wave doubler rectifier and produces a nominal 325 Vdc across series-connected C3 and C4 as before.

By means of transformer T2, the Control Section turns transistor Q1 ON and OFF in alternation with Q2. The cycle time is a nominal 50 us. (Take note that Q1 and Q2 are never both ON at the same time.) This alternately applies +162 Vdc and -162 Vdc across the primary of transformer T1. (Typical waveforms at various points in the circuit are shown on the schematic diagram) The resulting ac voltages across the secondaries of T1 are rectified and averaged in the Output Section. Therefore, the longer Q1 and Q2 are ON during each cycle, the higher the dc output voltages from the Output Section. The width of the ON-pulse thus provides a means of voltage control which is used by the Control Section for very close voltage regulation.

Capacitor C10 blocks any dc bias that might otherwise result from a mismatch between Q1 and Q2. Components R37 and C35 reduce ringing and transient spikes. CR2-R6-C19 and CR1-R5-C18 speed up the turnoff times for Q1 and Q2.

# 2.3.2.3 Control Section

The Control Section consists of: U1, a National DS3632 dual peripheral driver; U2, a Silicon General SG3524 regulating pulse-width modulator; Q3, a 2N3904 transistor; Q4, a 2N3905 transistor; Q5, a Motorola MCR101 SCR; CR5 and 6, 1N3600 diodes: CR 7 and 8, 1N4009 diodes; CR9,18,24, all 1N3600 diodes; CR10, a 1N588 zener diode; and CR20, a GE PD-10 bridge rectifier.

This circuit provides drive pulses through transformer T2 that switch Q1 and Q2 ON and OFF. And by controlling the width of these drive pulses in response to voltage feedback from the Output Section, the circuit provides good voltage regulation of the output voltages. Also, it detects any overcurrent condition and reacts by shutting down the Power Supply.

The nucleus of the Control Section is the LSI circuit U2. It is powered by a nominal +20 V from the bridge rectifier CR20; and CR20 is fed, via P13-3 and 4, with a nominal 17 Vac at 50-60 Hz from a small transformer, T3, mounted on the chassis (ref. Chassis schematic diagram in section 2.1). Circuit U2 produces drive pulses at outputs CA and CB (pins 12 and 13) that are used, via U1 and transformer T2, to turn Q1 and Q2 ON and OFF. The repetition rate of the pulses is established by an oscillator in U2 whose frequency is set by the values of R34 and C13 at pins 6 and 7 to a nominal 40 kHz. And, because there are two U2 drive pulses for one cycle of the Q1-Q2 switching circuit, this sets the switching frequency of the power supply to a nominal 20 kHz. (However, as a glance at the waveform across T1 will indicate, the rise times and attendant potential for EMI are more nearly those of a 40 kHz signal than a 20 kHz signal.)

The drive pulses from U2 act as follows. When CA is low and CB is high, U1 output 5 is turned OFF and U1 output 3 is turned ON. The +20 V applied through R8 drives a current through winding 2-3 of T2 in the direction making the dot end of the winding positive. This current in 2-3 induces voltages in

windings 7-4 and 6-1, making their respective dot ends positive. The connections to these windings are such that Q2 is turned ON and Q1 remains OFF (the base of O1 is driven even further negative).

The -162 Vdc applied to the emitter of Q2 drives a current through the transformer windings T1 3-9 and T2 8-5 in the direction making the dot end of 8-5 positive. This regenerative action reinforces the base drive to Q2. Transformer T2 acts as a current transformer, so the base drive current to Q2 is proportional to the T1 primary current through T2 8-5. The current ratio is such that Q2 is assured of being fully ON and well out of the linear region. Due to energy storage in inductive elements of the circuit, the T1 primary current that goes through T2 8-5 increases throughout the ON time of Q2. This sustains the high level of Q2 base drive supplied from T2 6-1.

Q2 is turned OFF again by the action of the blanking pulse within U2 which brings CA high along with CB. This turns U1 output 5 ON along with output 3, thus short circuiting winding T2 2-3 and cutting off the Q2 base drive current in T2 6-1. This short circuit condition lasts for at least the duration of the blanking pulse (a nominal 4 us), and during this time Q2 and Q1 are both forced to remain OFF. This insures that Q1 cannot be turned ON until Q2 is well OFF. The turn-on time of this type of transistor is shorter than the turn-off time. So without an adequately long blanking pulse, it would be possible for Q1 to turn ON while Q2 was still ON (for example, under conditions of low mains voltage and a compensating maximum pulse width for the switching circuit). This would put a short circuit across the ±162 V supply with undesirable results.

The next half of the 20 kHz switching cycle starts with the leading edge of the blanking pulse, but any drive pulse that would turn Q1 ON is inhibited within U2 for the duration of the blanking pulse. At the end of the blanking pulse, the voltage regulation circuitry in U2 is again in control, and as soon as that circuitry determines that it is time to start the Q1 drive pulse, CB is brought low. This turns U1 output 3 OFF and starts a current through winding 2-3 of T2 in the direction to turn Q1 ON and hold Q2 OFF. The rest of the action is analogous to that of the first half cycle.